# LDO Regulator - Ultra-Low I<sub>q</sub>, Dual Power Mode

## 50 nA, 80 mA

### NCP171

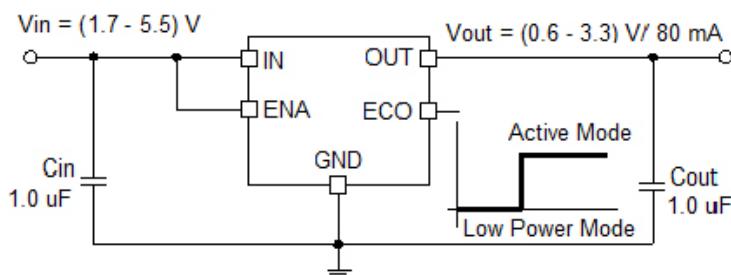

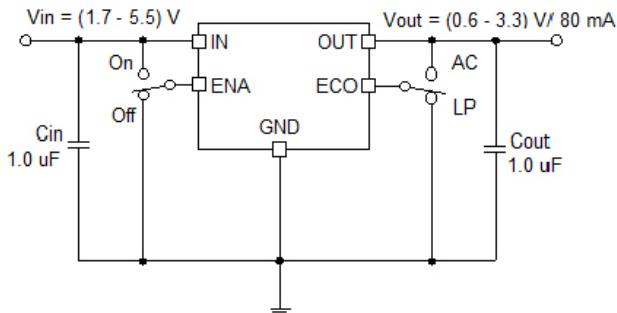

The NCP171 is a Dual mode LDO offering up to 80 mA in Active Mode and as low as 50 nA of I<sub>q</sub> in Low Power Mode. The Dual Mode function is selectable with the ECO pin allowing for dynamic switching between Active and Low Power Modes, ideal in long life battery powered applications.

The output Voltage in Low Power mode can be lowered by an internally factory programmed value ranging 50 mV, 100 mV, 150 mV or 200 mV with respect to the nominal output voltage in Active Mode. This feature further lowers the application consumption in sleep mode. The NCP171 is in the SLIQ (Super Low I<sub>q</sub>) LDO family and is available in small XDFN4 1.2 x 1.2 package.

#### Features

- Operating Input Voltage Range: 1.7 V to 5.5 V

- Output Voltage Range: 0.6 V to 3.3 V (50 mV steps)

- Low Power Mode / Active Mode Externally Controlled by ECO pin

- Internally Factory Programmable Output Voltage Offset for Low Power/Active Mode to 50 mV, 100 mV, 150 mV, 200 mV

- Quiescent Current of 50 nA at No Load, (Low Power mode)

- Maximum Current 80 mA in Active Mode and 5 mA in Low Power Mode

- Low Dropout: 41 mV Typ. at 80 mA (V<sub>out</sub> = 3.3 V)

- $\pm 2\%$  Output Voltage Accuracy in Active Mode

- High PSRR: 65 dB at 1 kHz in Active Mode

- Active Output Discharge for Fast Output Turn-Off

- Current Limitation, Thermal Shutdown

- Available in Small XDFN4 1.2x1.2 Package

- These are Pb-Free Devices

#### Typical Applications

- IoT

- RFID

- Portable Communication Equipment

- Consumer Electronics

Figure 1. Typical Application Schematic

**ON Semiconductor®**

[www.onsemi.com](http://www.onsemi.com)

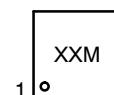

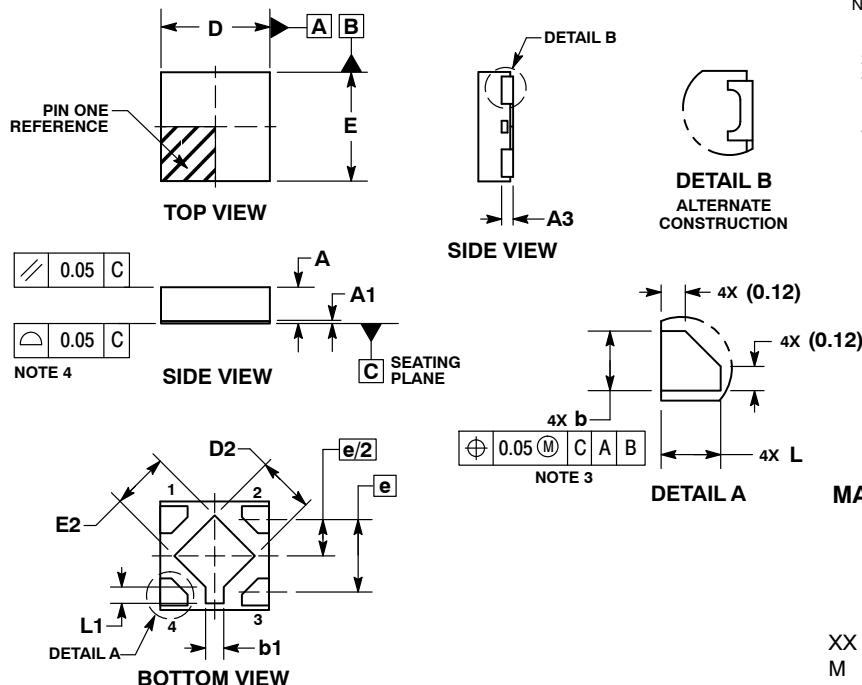

XDFN4 1.2x1.2

AM SUFFIX

CASE 711BC

#### MARKING DIAGRAM

XX = Specific Device Code

M = Date Code

#### PIN CONNECTIONS

(Top View)

#### ORDERING INFORMATION

See detailed ordering, marking and shipping information on page 20 of this data sheet.

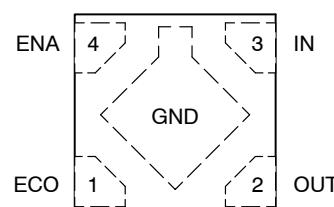

Figure 2. Simplified Schematic Block Diagram

Table 1. PIN FUNCTION DESCRIPTION

| Pin No.<br>XDFN4 | Pin Name | Description                                                                                                                                                                            |

|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | ECO      | Low Power and Active mode control pin. Pulling this pin to ground switches the device into Low Power mode and pushing this pin to output voltage switches the device into Active mode. |

| 2                | OUT      | Output pin                                                                                                                                                                             |

| 3                | IN       | Input pin                                                                                                                                                                              |

| 4                | ENA      | Enable pin. Driving ENA above 1.2 V turns on the regulator. Driving ENA below 0.4 V puts the regulator into shutdown mode.                                                             |

| 5(EP)            | GND      | Ground                                                                                                                                                                                 |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                    | Symbol      | Value            | Unit |

|-------------------------------------------|-------------|------------------|------|

| Input Voltage (Note 1)                    | $V_{IN}$    | 6.0              | V    |

| Output Voltage                            | $V_{OUT}$   | −0.3 to $V_{IN}$ | V    |

| Enable pin                                | $V_{ENA}$   | −0.3 to $V_{IN}$ | V    |

| ECO pin                                   | $V_{ECO}$   | −0.3 to $V_{IN}$ | V    |

| Output Current                            | $I_{OUT}$   | 120              | mA   |

| Power Dissipation XDFN4                   | $P_D$       | 400              | mW   |

| Maximum Junction Temperature              | $T_J(MAX)$  | 85               | °C   |

| Storage Temperature                       | $T_{STG}$   | −55 to 125       | °C   |

| ESD Capability, Human Body Model (Note 2) | $ESD_{HBM}$ | 2000             | V    |

| ESD Capability, Machine Model (Note 2)    | $ESD_{MM}$  | 200              | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating tested per JEDEC standard: JESD78

**Table 3. THERMAL CHARACTERISTICS (Note 3)**

| Rating                                                                | Symbol          | Value | Unit |

|-----------------------------------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, XDFN4<br>Thermal Resistance, Junction-to-Air | $R_{\theta JA}$ | 170   | °C/W |

3. This data was derived by thermal simulations for a single device mounted on the 40 mm × 40 mm × 1.6 mm FR4 PCB with 2-ounce 800 sq mm copper area on top and bottom.

**Table 4. ELECTRICAL CHARACTERISTICS**  $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ ;  $V_{IN} = V_{OUTNOM} + 0.5 \text{ V}$  or  $1.7 \text{ V}$ , whichever is greater;  $I_{OUT} = 100 \mu\text{A}$  at Low Power Mode /  $1 \text{ mA}$  at Active Mode,  $C_{IN} = C_{OUT} = 1.0 \mu\text{F}$ , unless otherwise noted. Typical values are at  $T_J = +25^\circ\text{C}$ . (Note 4)

| Parameter                 | Test Conditions                                                                                                                                    |                                                    | Symbol                               | Min               | Typ | Max   | Unit          |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------|-------------------|-----|-------|---------------|

| Operating Input Voltage   |                                                                                                                                                    |                                                    | $V_{IN}$                             | 1.7               |     | 5.5   | V             |

| Output Voltage            | $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ , $I_{OUT} < 5 \text{ mA}$                                                                      | Low Power Mode (LP)<br>ECO = 0<br>NCP171A3MXxxxxyy | $V_{OUTAC} = V_{OUTLP} + V_{OFFSET}$ | x0.97             |     | x1.03 | V             |

|                           | $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ , $I_{OUT} < 5 \text{ mA}$                                                                      | Low Power Mode (LP)<br>ECO = 0<br>NCP171AMXxxxxyy  |                                      | x0.95             |     | x1.05 | V             |

|                           | $T_J = +25^\circ\text{C}$ , $0 \leq I_{OUT} < 80 \text{ mA}$                                                                                       | Active Mode (AC)<br>ECO = $V_{OUTNOM}$             |                                      | x0.98             |     | x1.02 | V             |

|                           | $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ , $0 \leq I_{OUT} < 80 \text{ mA}$                                                              | Active Mode<br>ECO = $V_{OUTNOM}$                  |                                      | x0.97             |     | x1.03 | V             |

| Offset (Note 5)           |                                                                                                                                                    | $T_J = +25^\circ\text{C}$                          | $V_{OFFSET}$                         | 50, 100, 150, 200 |     |       | mV            |

| Line Regulation           | $V_{IN} = V_{OUT} + 0.5 \text{ V}$ to $5.5 \text{ V}$ , $V_{IN} \geq 1.7 \text{ V}$                                                                | $I_{OUT} = 100 \mu\text{A}$ , LP Mode              | Line <sub>Reg</sub>                  |                   |     | 10    | mV            |

|                           |                                                                                                                                                    | $I_{OUT} = 1 \text{ mA}$ , AC Mode                 |                                      |                   |     | 10    |               |

| Load Regulation           | $1 \text{ mA} \leq I_{OUT} \leq 80 \text{ mA}$ , $V_{IN} = V_{OUT} + 0.5 \text{ V}$ or $V_{IN} \geq 1.7 \text{ V}$ Active Mode, ECO = $V_{OUTNOM}$ |                                                    | Load <sub>Reg</sub>                  |                   |     | 10    | mV            |

|                           | $0 \text{ mA} < I_{OUT} < 5 \text{ mA}$ , $V_{IN} = V_{OUT} + 0.5 \text{ V}$ or $V_{IN} \geq 1.7 \text{ V}$ Low Power Mode, ECO = 0                |                                                    |                                      |                   |     | 30    | mV            |

| Dropout Voltage (Note 6)  | $I_{OUT} = 80 \text{ mA}$ , Active Mode, ECO = $V_{OUTNOM}$                                                                                        | $V_{OUT} = 1.8 \text{ V}$                          |                                      |                   | 81  | 110   | mV            |

|                           |                                                                                                                                                    | $V_{OUT} = 2.5 \text{ V}$                          |                                      |                   | 51  | 80    |               |

|                           |                                                                                                                                                    | $V_{OUT} = 2.8 \text{ V}$                          |                                      |                   | 47  | 75    |               |

|                           |                                                                                                                                                    | $V_{OUT} = 3.0 \text{ V}$                          |                                      |                   | 43  | 65    |               |

|                           |                                                                                                                                                    | $V_{OUT} = 3.3 \text{ V}$                          |                                      |                   | 41  | 55    |               |

| Output Current            | Active Mode, ECO = $V_{OUTNOM}$                                                                                                                    |                                                    | $I_{OUTAM}$                          | 80                |     |       | mA            |

| Output Current            | Low Power Mode, ECO = 0                                                                                                                            |                                                    | $I_{OUTLP}$                          | 5                 |     |       | mA            |

| Output Current Limit      | $V_{OUT} = 90\% V_{OUT(nom)}$ , Active mode, ECO = $V_{OUTNOM}$                                                                                    |                                                    | $I_{SC}$                             |                   | 140 | 170   | mA            |

| Output Current Limit      | $V_{OUT} = 90\% V_{OUT(nom)}$ , Low Power mode, ECO = 0                                                                                            |                                                    | $I_{SC}$                             |                   | 9   | 15    | mA            |

| Quiescent Current         | $I_{OUT} = 0$<br>Low Power Mode                                                                                                                    | $T_J = +25^\circ\text{C}$                          | $I_Q$                                |                   | 50  |       | nA            |

|                           | $I_{OUT} = 0 \text{ mA}$ ,<br>Low Power Mode                                                                                                       | $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ |                                      |                   |     | 150   | nA            |

|                           | $I_{OUT} = 0 \text{ mA}$ ,<br>Active Mode                                                                                                          | $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ |                                      |                   | 55  | 95    | $\mu\text{A}$ |

| Shutdown Current (Note 7) | $V_{ENA} \leq 0.4 \text{ V}$ , $V_{IN} = 5.5 \text{ V}$                                                                                            |                                                    | $I_{DIS}$                            |                   | 30  |       | nA            |

- Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at  $T_J = T_A = 25^\circ\text{C}$ . Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

- The Offset voltage is internally programmed to 50 mV, 100 mV, 150 mV or 200 mV. See the table ORDERING INFORMATION for more details.

- The Dropout at Nominal Output Voltage below 1.8 V and output current 80 mA was not defined and tested. The dropout at Nominal Output Voltage above 1.8 V was characterized when  $V_{OUT}$  falls 3% below the nominal regulated voltage.

- Shutdown Current is the current flowing into the IN pin when the device is in the disable state ( $V_{ENA} < 0.4 \text{ V}$ ).

- Guaranteed by design and characterization.

**Table 4. ELECTRICAL CHARACTERISTICS**  $-40^{\circ}\text{C} \leq T_J \leq 85^{\circ}\text{C}$ ;  $V_{IN} = V_{OUTNOM} + 0.5 \text{ V}$  or  $1.7 \text{ V}$ , whichever is greater;  $I_{OUT} = 100 \mu\text{A}$  at Low Power Mode /  $1 \text{ mA}$  at Active Mode,  $C_{IN} = C_{OUT} = 1.0 \mu\text{F}$ , unless otherwise noted. Typical values are at  $T_J = +25^{\circ}\text{C}$ . (Note 4)

| Parameter                             | Test Conditions                                                                                                                                                                  | Symbol     | Min | Typ  | Max | Unit                |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|-----|---------------------|

| Ground Current                        | Low Power Mode, $I_{OUT} = 10 \mu\text{A}$                                                                                                                                       | $I_{GND}$  |     | 230  |     | nA                  |

|                                       | Low Power Mode, $I_{OUT} = 100 \mu\text{A}$                                                                                                                                      |            |     | 620  |     |                     |

|                                       | Low Power Mode, $I_{OUT} = 1 \text{ mA}$                                                                                                                                         |            |     | 1500 |     |                     |

|                                       | Low Power Mode, $I_{OUT} = 5 \text{ mA}$                                                                                                                                         |            |     | 2500 |     |                     |

|                                       | Active Mode, $I_{OUT} = 1 \text{ mA}$                                                                                                                                            |            |     | 120  |     | $\mu\text{A}$       |

|                                       | Active Mode, $I_{OUT} = 10 \text{ mA}$                                                                                                                                           |            |     | 190  |     |                     |

|                                       | Active Mode, $I_{OUT} = 80 \text{ mA}$                                                                                                                                           |            |     | 420  |     |                     |

| ENA Pin Threshold Voltage             | ENA Input Voltage "H"                                                                                                                                                            | $V_{ENAH}$ | 1.2 |      |     | V                   |

|                                       | ENA Input Voltage "L"                                                                                                                                                            | $V_{ENAL}$ |     |      | 0.4 | V                   |

| ECO Pin Threshold Voltage             | ECO Input Voltage "H"                                                                                                                                                            | $V_{ECOH}$ | 0.5 |      |     | V                   |

|                                       | ECO Input Voltage "L"                                                                                                                                                            | $V_{ECOL}$ |     |      | 0.2 |                     |

| Power Supply Rejection Ratio          | $V_{IN} = V_{OUT} + 1 \text{ V}$ or $2.0 \text{ V}$ whichever is higher, $\Delta V_{IN} = 0.1 \text{ V}_{pk-pk}$ , $I_{OUT} = 10 \text{ mA}$ , $f = 1 \text{ kHz}$ , Active Mode | PSRR       |     | 65   |     | dB                  |

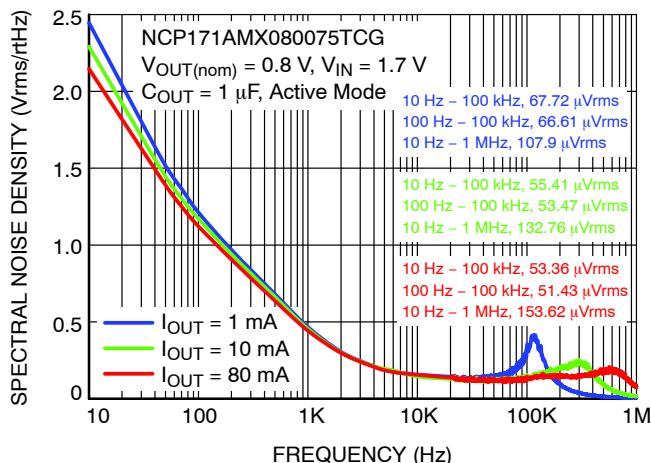

| Output Noise Voltage                  | $V_{OUT} = 0.8 \text{ V}$ , $I_{OUT} = 80 \text{ mA}$ , $f = 10 \text{ Hz}$ to $100 \text{ kHz}$ , Active Mode                                                                   | $V_N$      |     | 54   |     | $\mu\text{V}_{rms}$ |

| Thermal Shutdown Temperature (Note 8) | Temperature increasing from $T_J = +25^{\circ}\text{C}$ , Active Mode                                                                                                            | $T_{SD}$   |     | 165  |     | $^{\circ}\text{C}$  |

| Thermal Shutdown Hysteresis (Note 8)  | Temperature falling from $T_{SD}$ , Active Mode                                                                                                                                  | $T_{SDH}$  |     | 20   |     | $^{\circ}\text{C}$  |

- Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at  $T_J = T_A = 25^{\circ}\text{C}$ . Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

- The Offset voltage is internally programmed to 50 mV, 100 mV, 150 mV or 200 mV. See the table ORDERING INFORMATION for more details.

- The Dropout at Nominal Output Voltage below 1.8 V and output current 80 mA was not defined and tested. The dropout at Nominal Output Voltage above 1.8 V was characterized when  $V_{OUT}$  falls 3% below the nominal regulated voltage.

- Shutdown Current is the current flowing into the IN pin when the device is in the disable state ( $V_{ENA} < 0.4 \text{ V}$ ).

- Guaranteed by design and characterization.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

## APPLICATION INFORMATION

A typical application circuit for NCP171 series is shown in Figure 3.

Figure 3. Typical Application Schematic

#### Input Decoupling Capacitor (C1)

A 1.0  $\mu$ F ceramic input decoupling capacitor should be connected as close as possible to the input and ground pin of the NCP171. Higher values and lower ESR improves line transient response.

#### Output Decoupling Capacitor (C2)

A 1.0  $\mu$ F ceramic output decoupling capacitor is sufficient to achieve stable operation of the IC. If tantalum capacitor is used, and its ESR is high, the loop oscillation may result. If output capacitor is composed from few ceramic capacitors in parallel, the operation can be unstable. The capacitor should be connected as close as possible to the output and ground pin. Larger values and lower ESR improves dynamic parameters. The maximum capacitor 4.7  $\mu$ F could be connected to the output in order to keep stable operation.

#### ECO Mode, Voltage Scaling

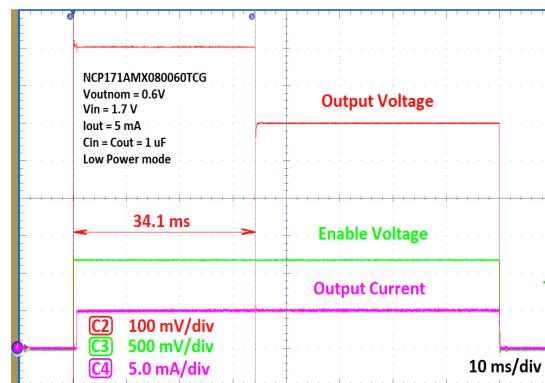

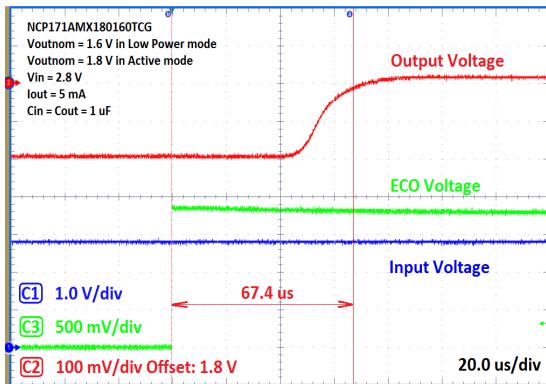

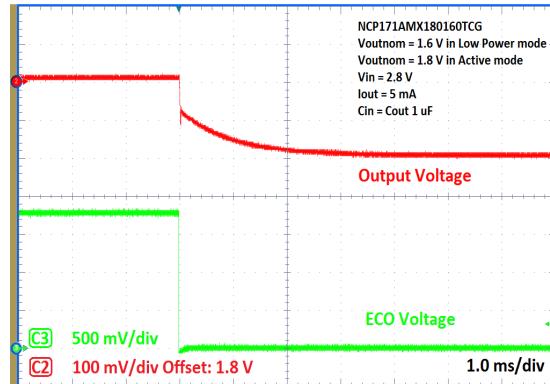

The NCP171 has two distinct modes of operation, Active mode and Low Power mode, selectable with the ECO pin. When asserted low the ECO pin switches the device to Low Power mode with reduced load of 5 mA and while significantly reducing the quiescent current down to 50 nA. Further system level power reduction is made possible by reducing the output Voltage by the internally programmed offsets of 50 mV, 100 mV, 150 mV and 200 mV in Low Power mode. When asserted high the ECO pin switches the device to Active mode. Active mode features higher loads, up to 80 mA, Faster transient, High PSRR and lower noise.

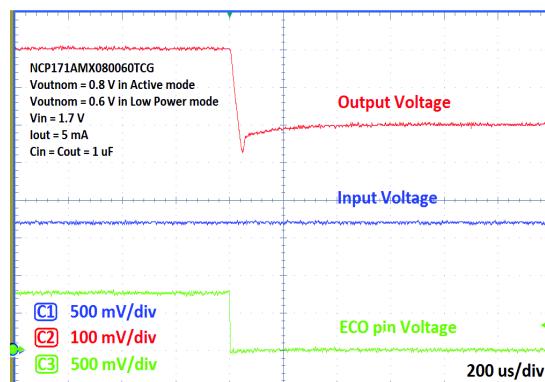

Upon startup by Enable or Input Voltage the NCP171 defaults into Active mode, regardless of the state of the ECO pin, to enable fast and stable startup to the target output voltage. The duration of this enforced Active mode is typically 35 ms. This function helps to absorb high current spikes for the proper charging of output capacitor and startup current of the customer's application. The transitions from

Low power mode to Active mode and reversely are depicted in Typical Characteristics chapter.

#### Enable Operation

The NCP171 device uses the ENA pin to enable/disable its device. If the ENA pin voltage is higher than 1.2 V the device is guaranteed to be enabled. The voltage below 0.4 V at the ENA pin assures turned-off output voltage. The active discharge transistor is active so that the output voltage VOUT is pulled to GND through the internal NMOS with  $R_{DS(on)}$  about 50 ohms. In the disable state the device consumes as low as 30 nA from the VIN. In the case where the ENABLE function isn't required the ENA pin should be tied directly to VIN.

#### Thermal

As power across the NCP171 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and also the ambient temperature affect the rate of temperature rise for the part. This is stating that when the NCP171 has good thermal conductivity through the PCB, the junction temperature will be relatively low with high power dissipation.

The power dissipation across the device can be roughly represented by the equation:

$$P_D = (V_{IN} - V_{OUT}) \cdot I_{OUT} \text{ [W]} \quad (\text{eq. 1})$$

The maximum power dissipation depends on the thermal resistance of the case and circuit board, the temperature differential between the junction and ambient, PCB orientation and the rate of air flow.

The maximum allowable power dissipation can be calculated using the following equation:

$$P_{MAX} = (T_{JUNCTION} - T_{AMBIENT}) / \theta_{JA} \text{ [W]} \quad (\text{eq. 2})$$

Where  $(T_{JUNCTION} - T_{AMBIENT})$  is the temperature differential between the junction and the surrounding environment and  $\theta_{JA}$  is the thermal resistance from the junction to the ambient.

Connecting the exposed pad or non connected pins to a large ground pad or plane helps to conduct away heat and improves thermal relief.

#### PCB layout

Make VIN and GND line sufficient. If their impedance is high, noise pickup or unstable operation may result. Connect capacitors C1 and C2 as close as possible to the IC, and make wiring as short as possible.

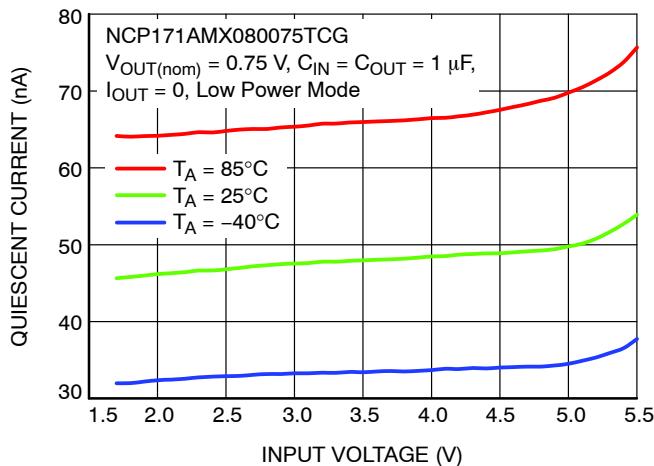

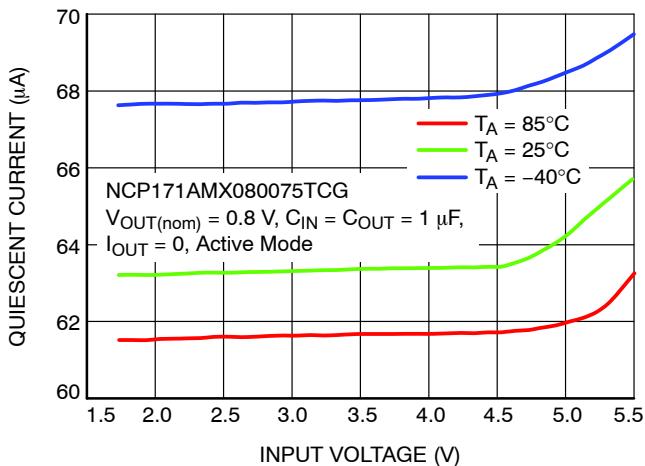

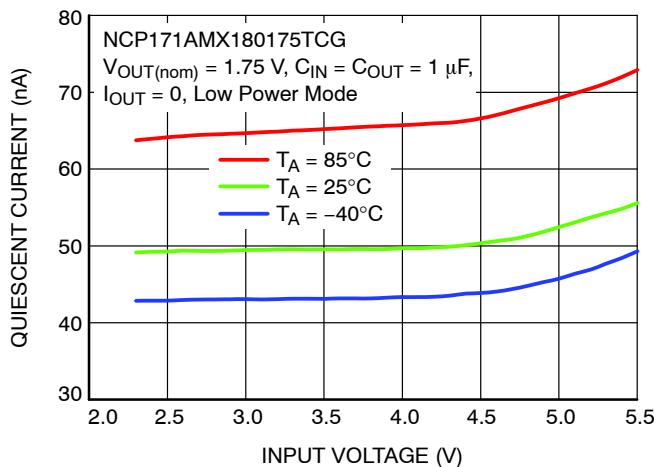

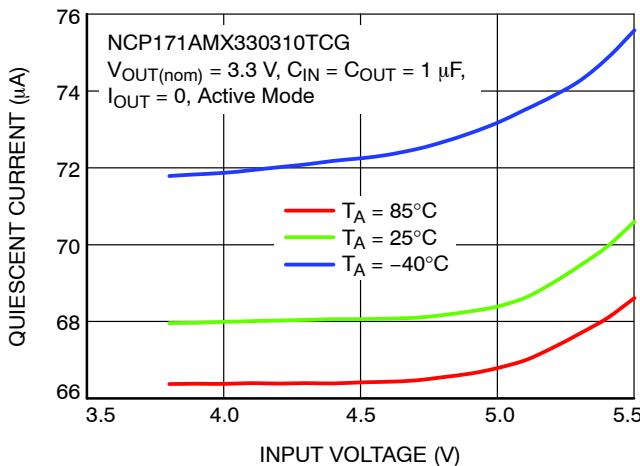

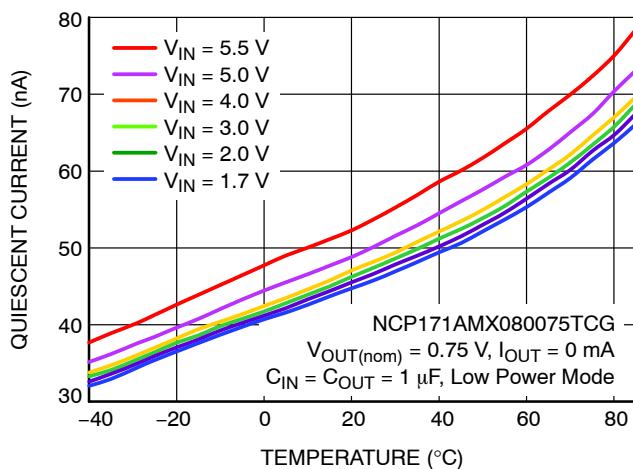

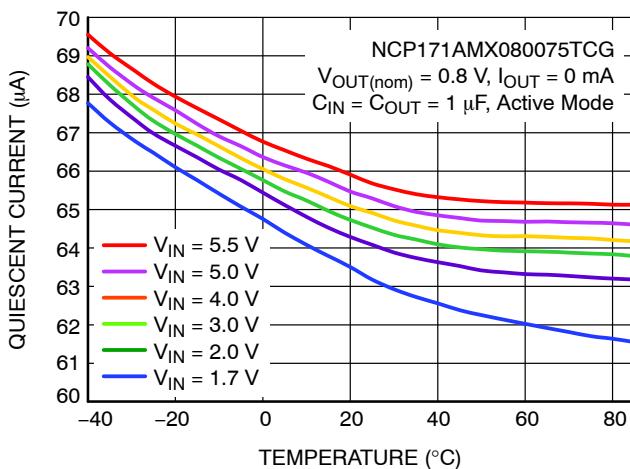

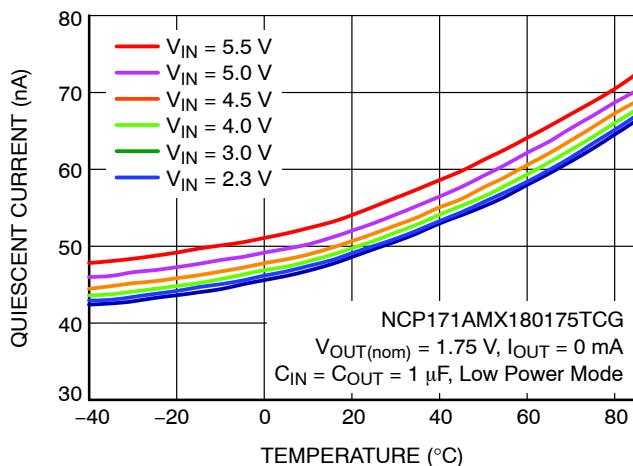

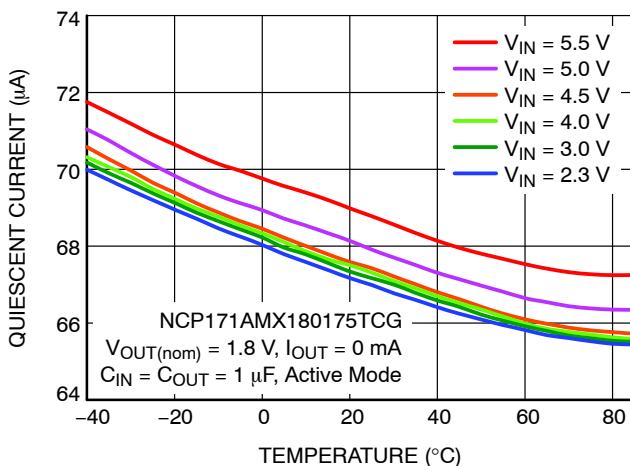

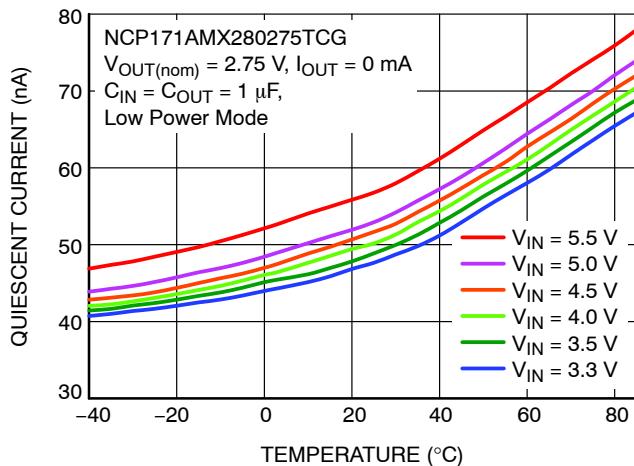

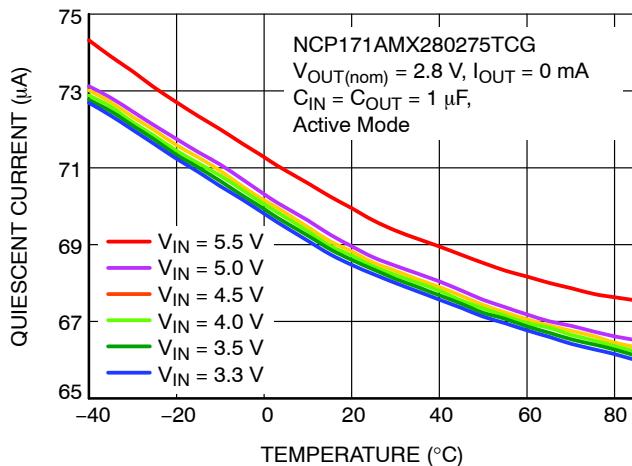

## TYPICAL CHARACTERISTICS

Figure 4. Quiescent Current vs. Input Voltage in Low Power Mode

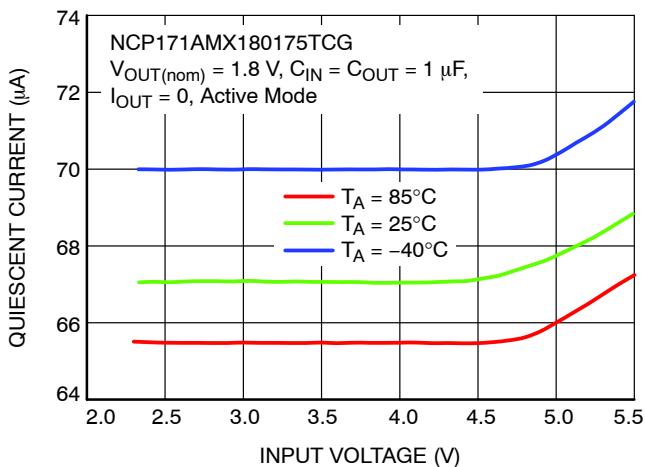

Figure 5. Quiescent Current vs. Input Voltage in Active Mode

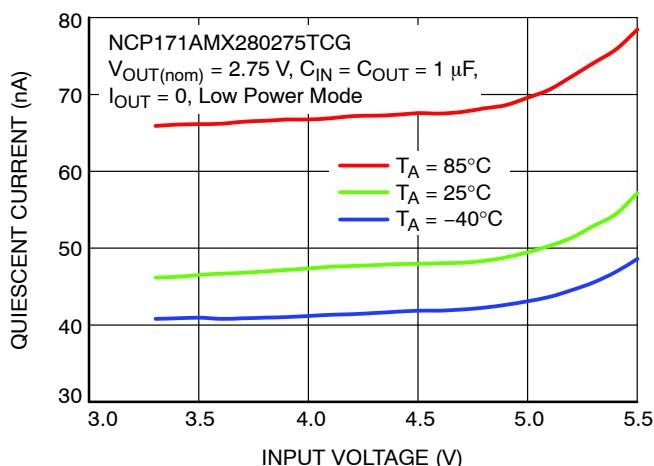

Figure 6. Quiescent Current vs. Input Voltage in Low Power Mode

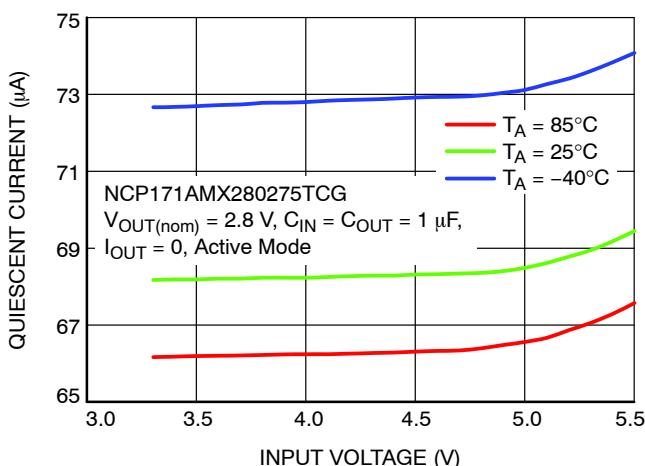

Figure 7. Quiescent Current vs. Input Voltage in Active Mode

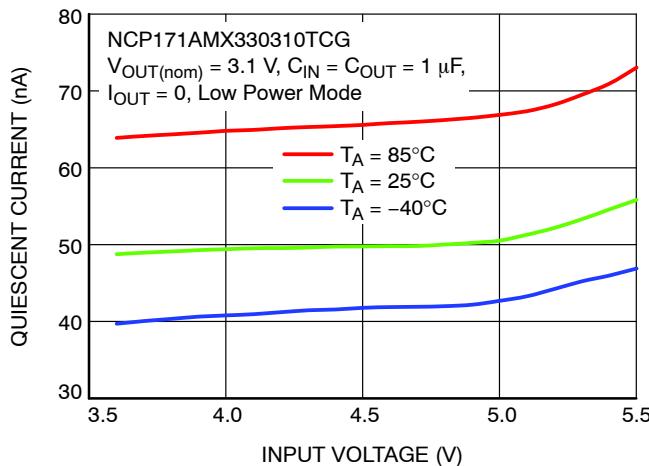

Figure 8. Quiescent Current vs. Input Voltage in Low Power Mode

Figure 9. Quiescent Current vs. Input Voltage in Active Mode

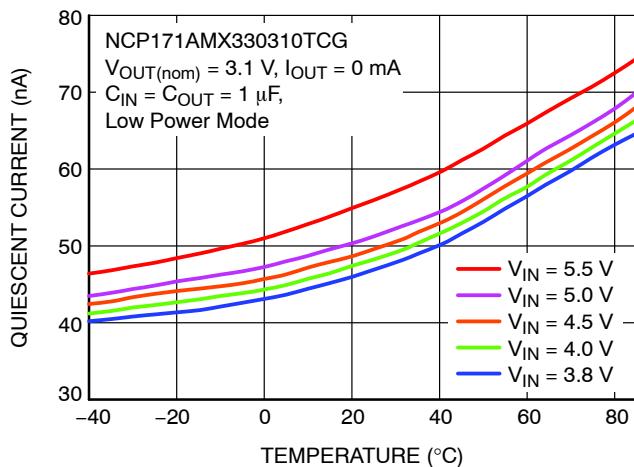

## TYPICAL CHARACTERISTICS

Figure 10. Quiescent Current vs. Input Voltage in Low Power Mode

Figure 11. Quiescent Current vs. Input Voltage in Active Mode

Figure 12. Quiescent Current vs. Temperature in Low Power Mode

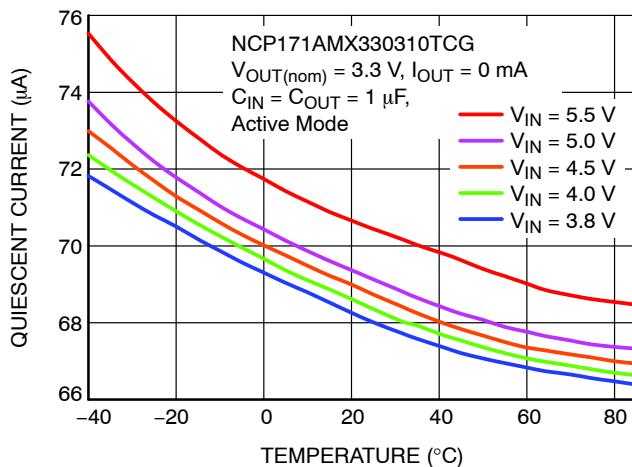

Figure 13. Quiescent Current vs. Temperature in Active Mode

Figure 14. Quiescent Current vs. Temperature in Low Power Mode

Figure 15. Quiescent Current vs. Temperature in Active Mode

## TYPICAL CHARACTERISTICS

Figure 16. Quiescent Current vs. Temperature in Low Power Mode

Figure 17. Quiescent Current vs. Temperature in Active Mode

Figure 18. Quiescent Current vs. Temperature in Low Power Mode

Figure 19. Quiescent Current vs. Temperature in Active Mode

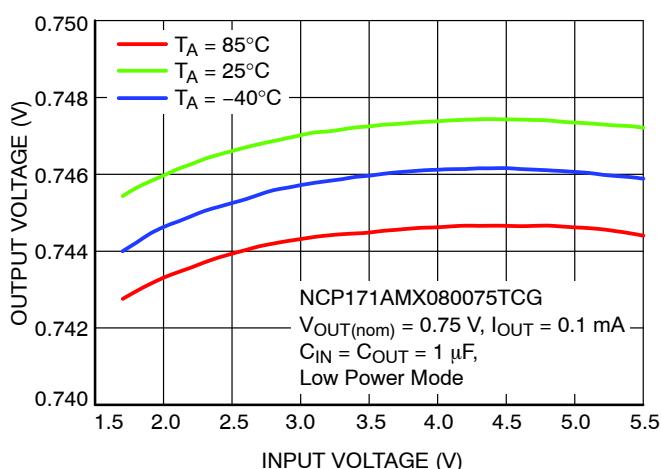

Figure 20. Output Voltage vs. Input Voltage in Low Power Mode

Figure 21. Output Voltage vs. Input Voltage in Active Mode

## TYPICAL CHARACTERISTICS

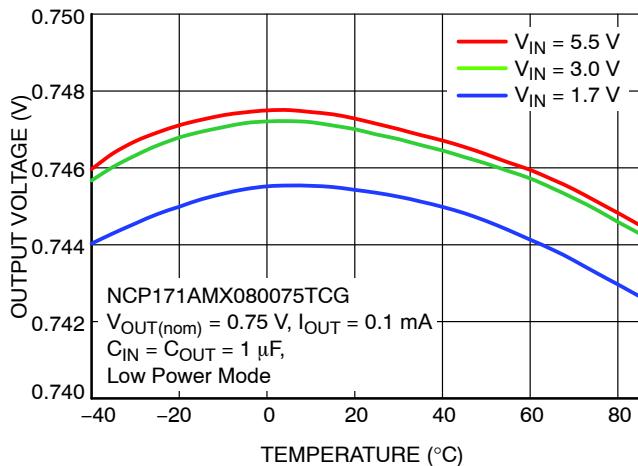

Figure 22. Output Voltage vs. Temperature in Low Power Mode

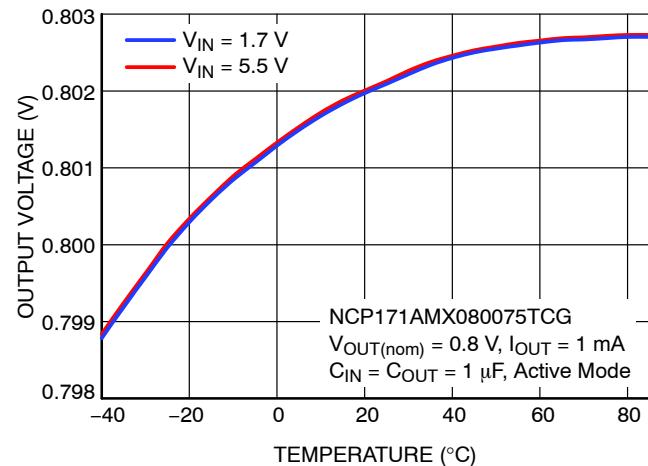

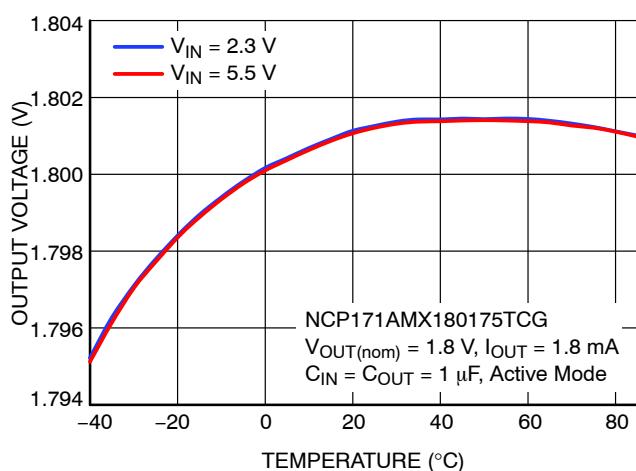

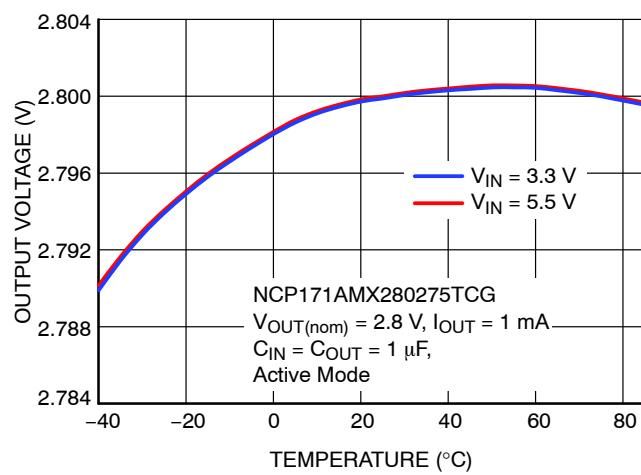

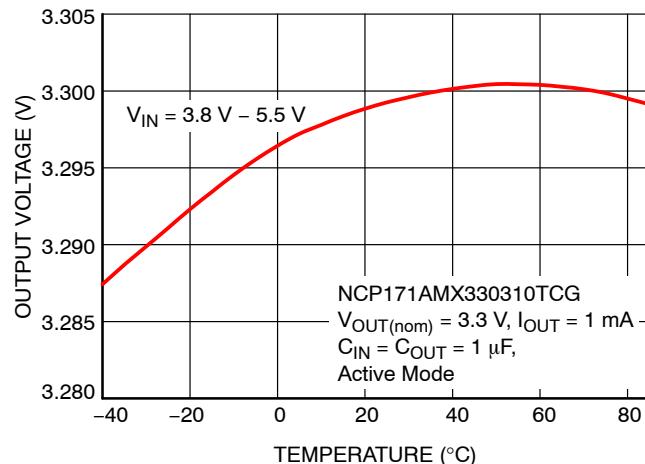

Figure 23. Output Voltage vs. Temperature in Active Mode

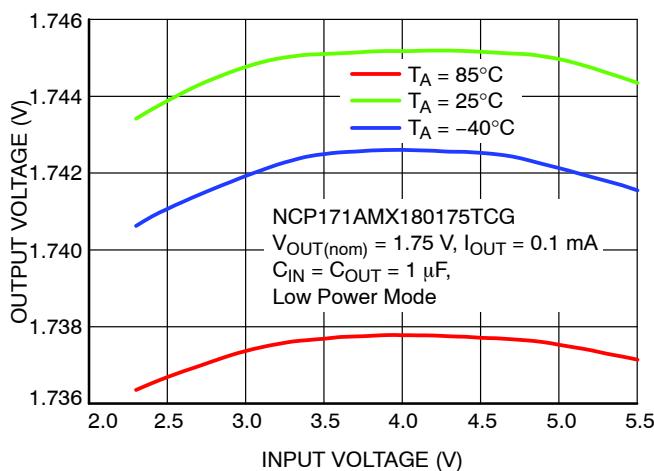

Figure 24. Output Voltage vs. Input Voltage in Low Power Mode

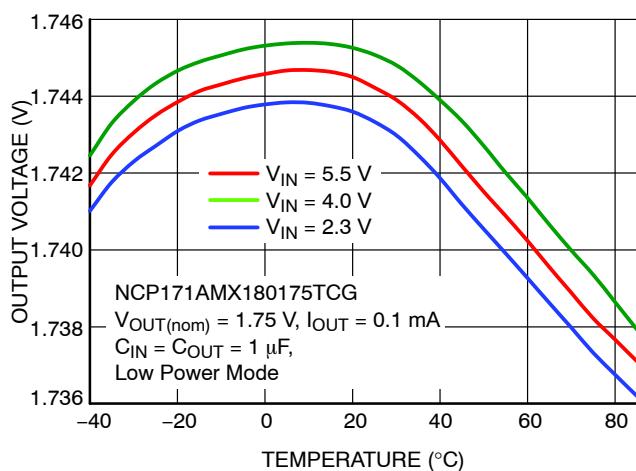

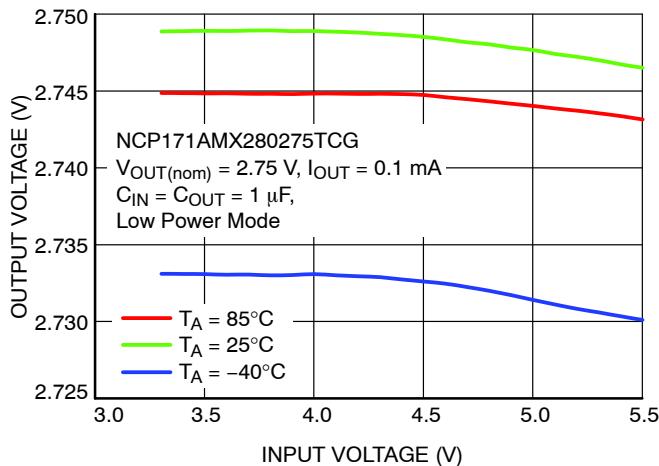

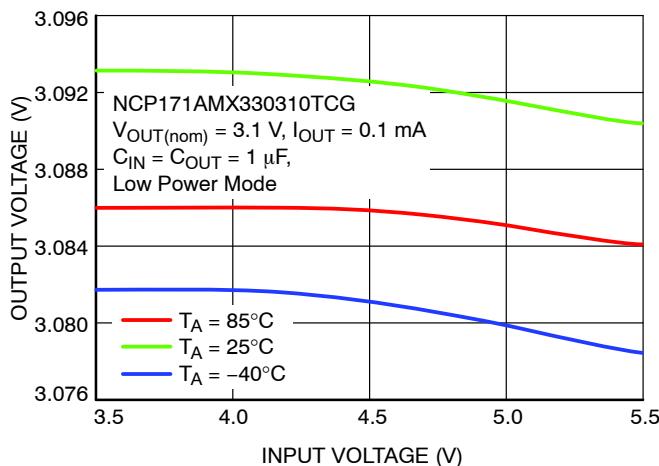

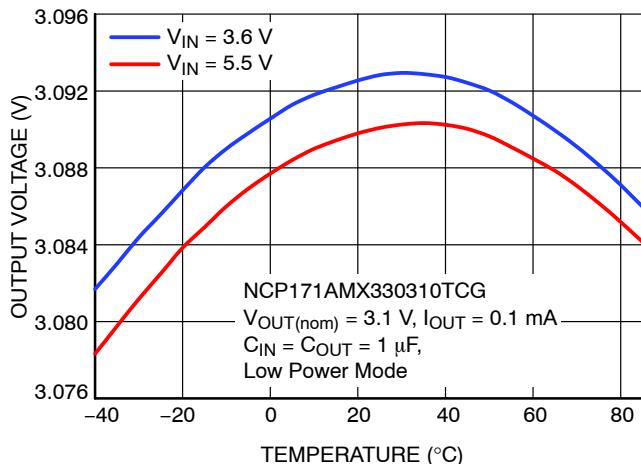

Figure 25. Output Voltage vs. Temperature in Low Power Mode

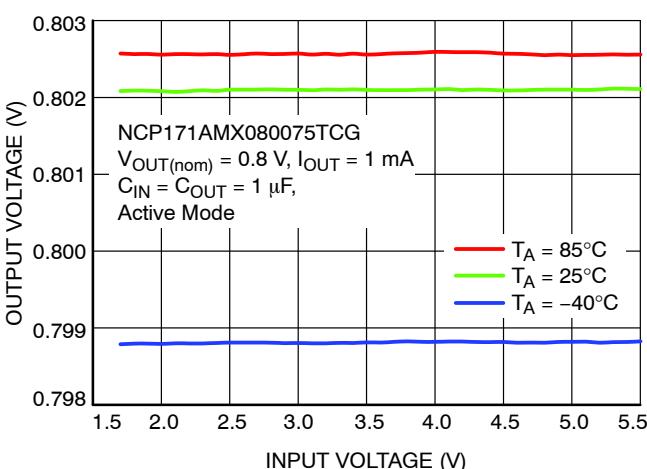

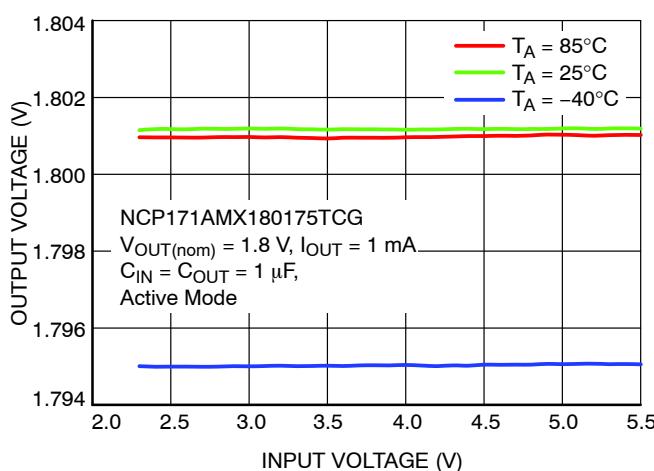

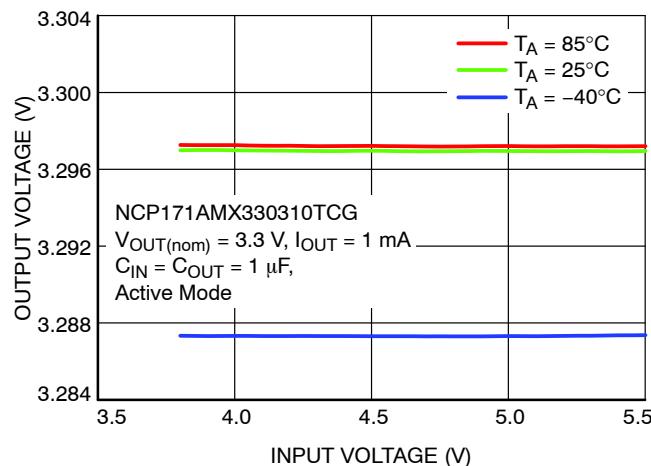

Figure 26. Output Voltage vs. Input Voltage in Active Mode

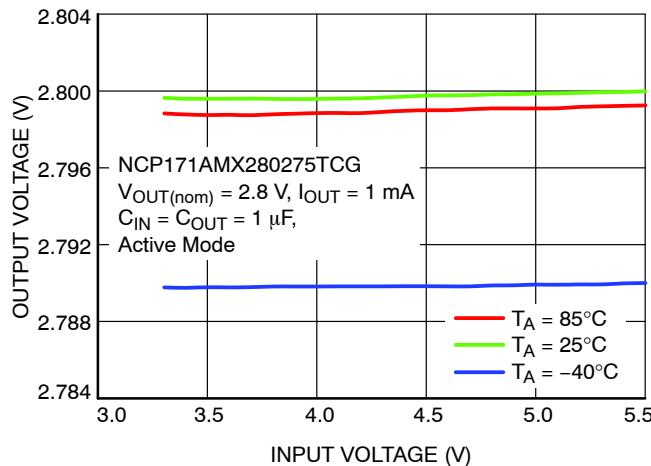

Figure 27. Output Voltage vs. Temperature in Active Mode

## TYPICAL CHARACTERISTICS

Figure 28. Output Voltage vs. Input Voltage in Low Power Mode

Figure 29. Output Voltage vs. Input Voltage in Active Mode

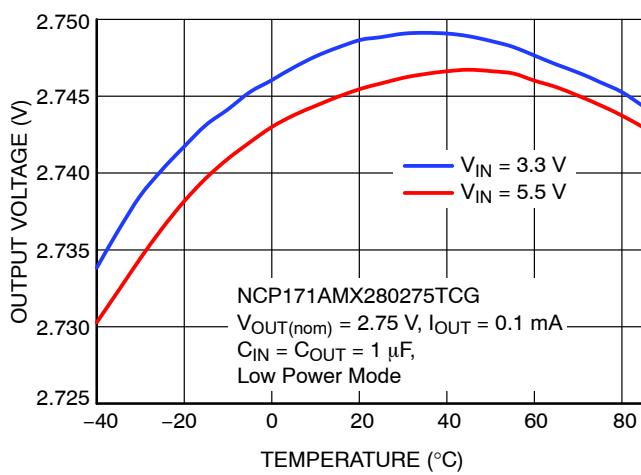

Figure 30. Output Voltage vs. Temperature in Low Power Mode

Figure 31. Output Voltage vs. Temperature in Active Mode

Figure 32. Output Voltage vs. Input Voltage in Low Power Mode

Figure 33. Output Voltage vs. Input Voltage in Active Mode

## TYPICAL CHARACTERISTICS

Figure 34. Output Voltage vs. Temperature in Low Power Mode

Figure 35. Output Voltage vs. Temperature in Active Mode

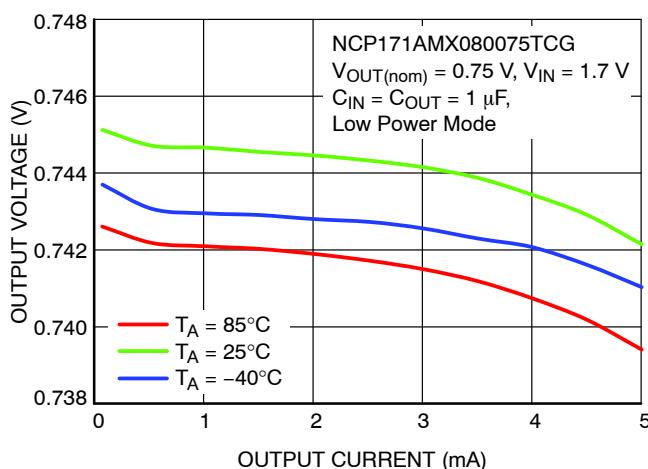

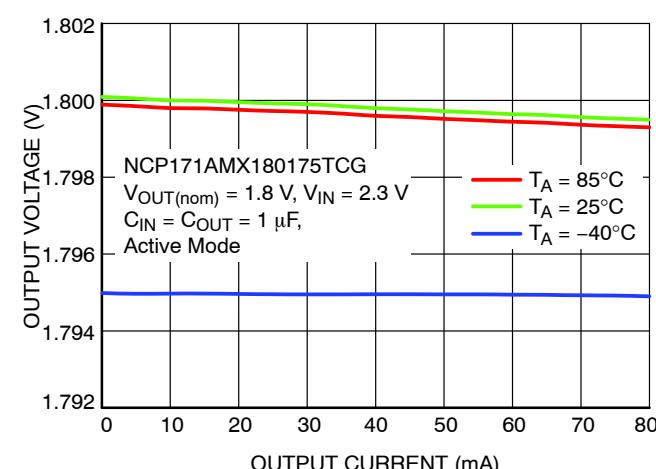

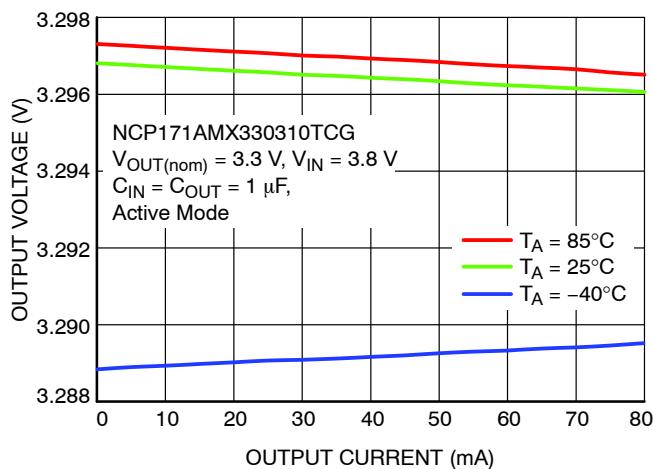

Figure 36. Output Voltage vs. Output Current in Low Power Mode

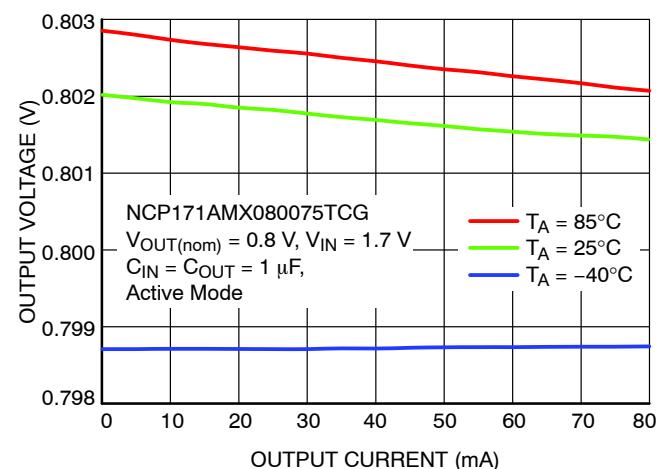

Figure 37. Output Voltage vs. Output Current in Active Mode

Figure 38. Output Voltage vs. Output Current in Low Power Mode

Figure 39. Output Voltage vs. Output Current in Active Mode

## TYPICAL CHARACTERISTICS

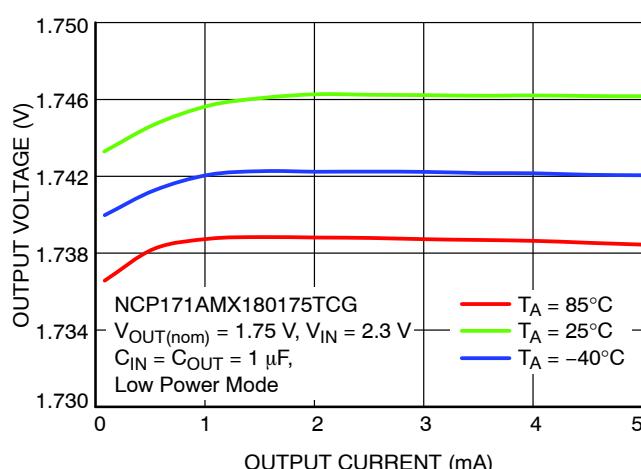

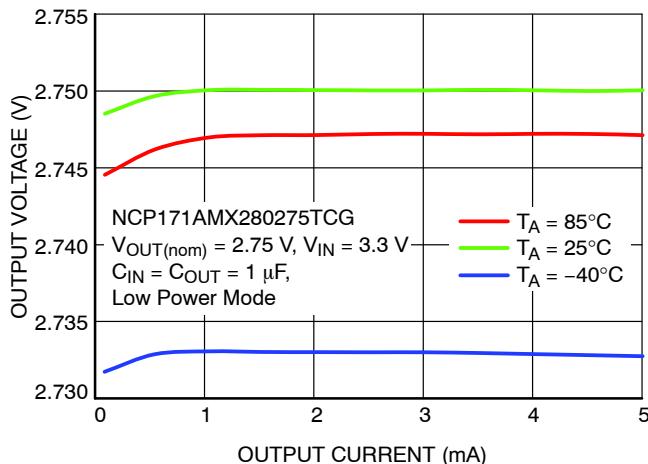

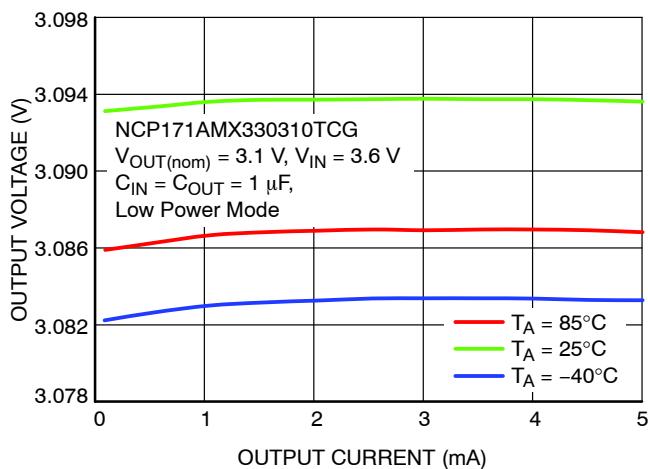

Figure 40. Output Voltage vs. Output Current in Low Power Mode

Figure 41. Output Voltage vs. Output Current in Active Mode

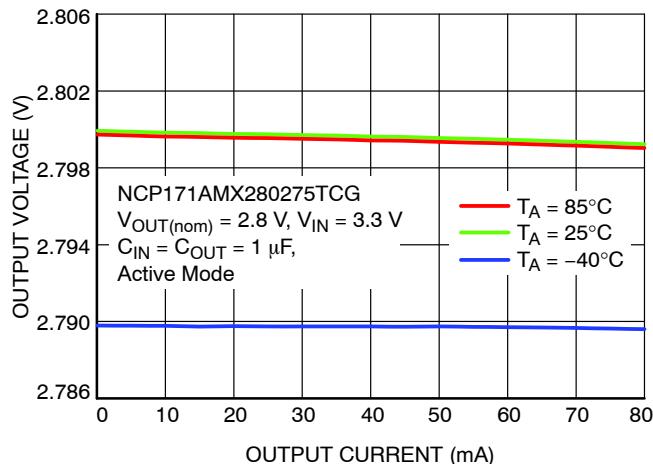

Figure 42. Output Voltage vs. Output Current in Low Power Mode

Figure 43. Output Voltage vs. Output Current in Active Mode

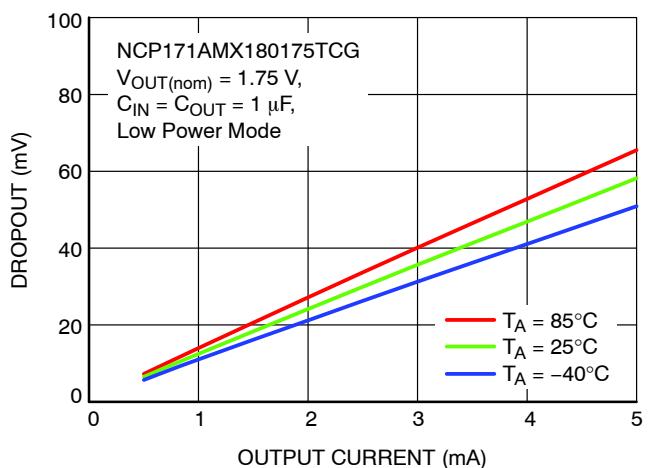

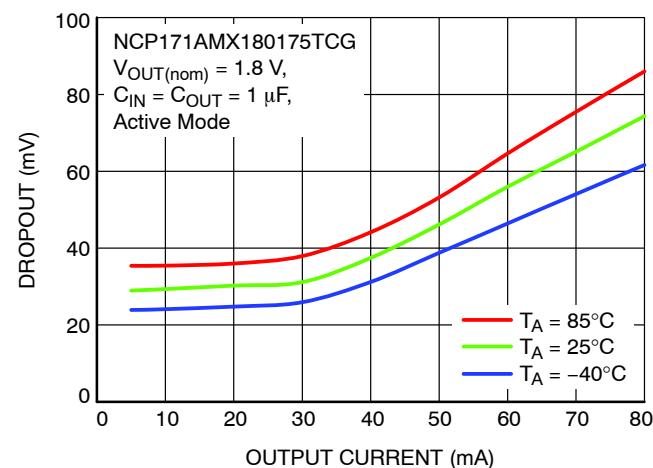

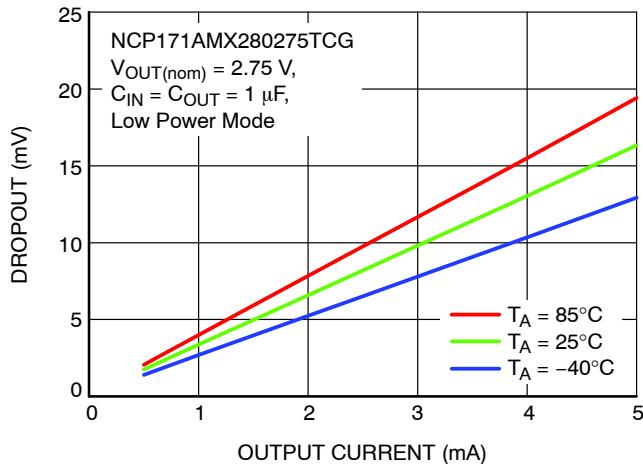

Figure 44. Dropout vs. Output Current in Low Power Mode

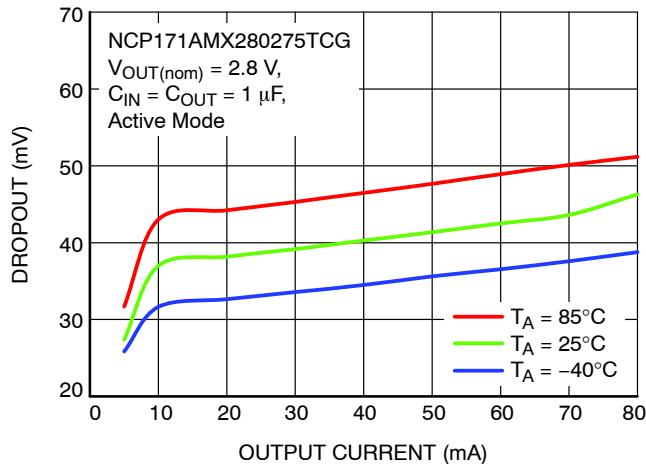

Figure 45. Dropout vs. Output Current in Active Mode

## TYPICAL CHARACTERISTICS

Figure 46. Dropout vs. Output Current in Low Power Mode

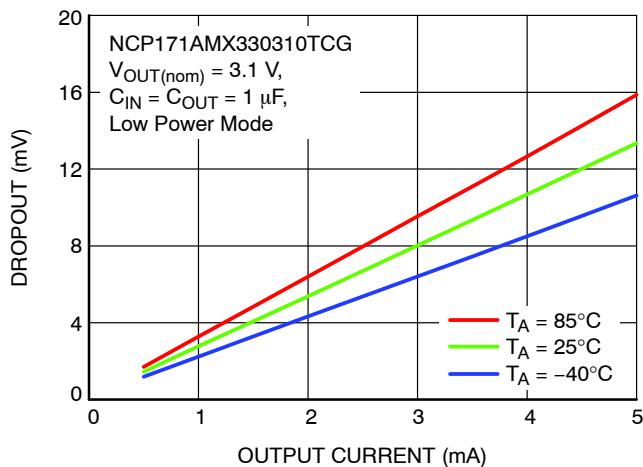

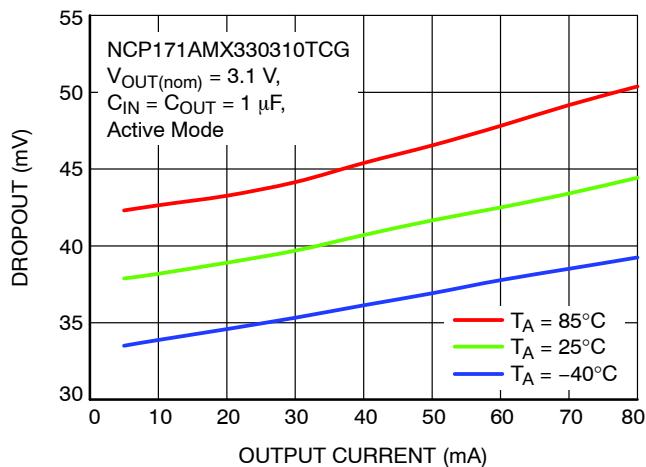

Figure 47. Dropout vs. Output Current in Active Mode

Figure 48. Dropout vs. Output Current in Low Power Mode

Figure 49. Dropout vs. Output Current in Active Mode

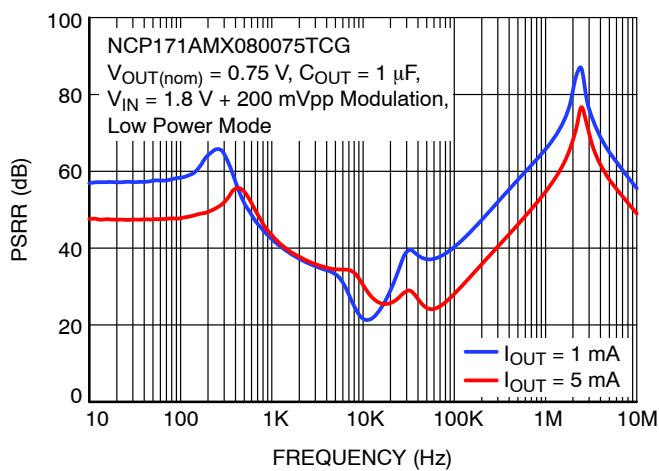

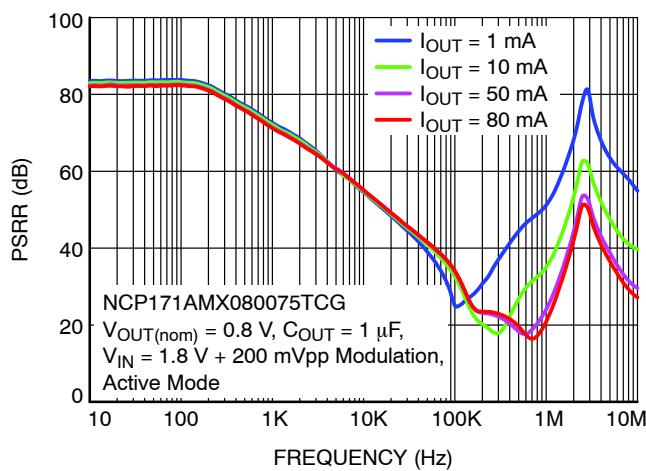

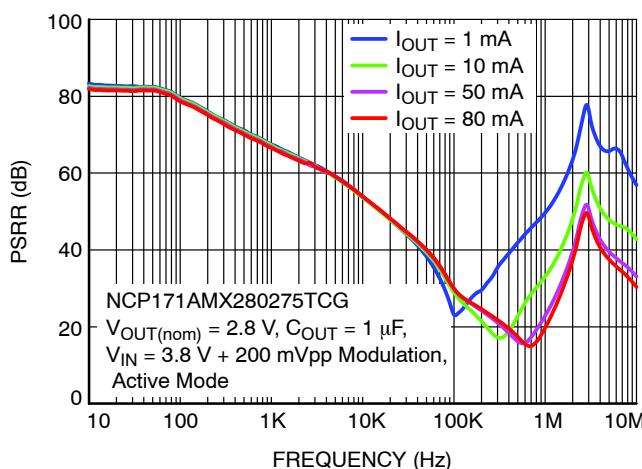

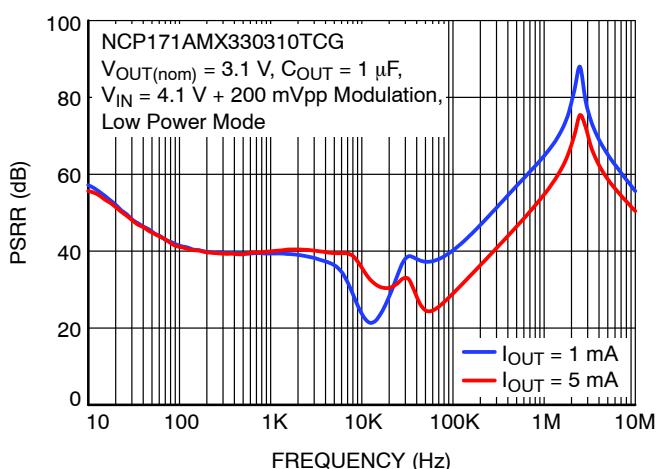

Figure 50. PSRR vs. Frequency in Low Power Mode

Figure 51. PSRR vs. Frequency in Active Mode

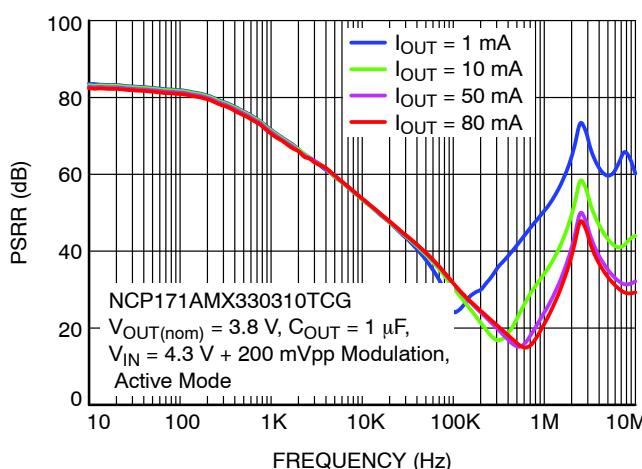

## TYPICAL CHARACTERISTICS

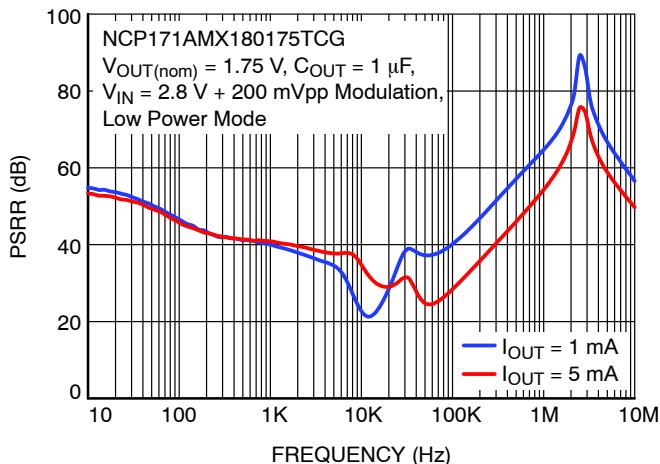

Figure 52. PSRR vs. Frequency in Low Power Mode

Figure 53. PSRR vs. Frequency in Active Mode

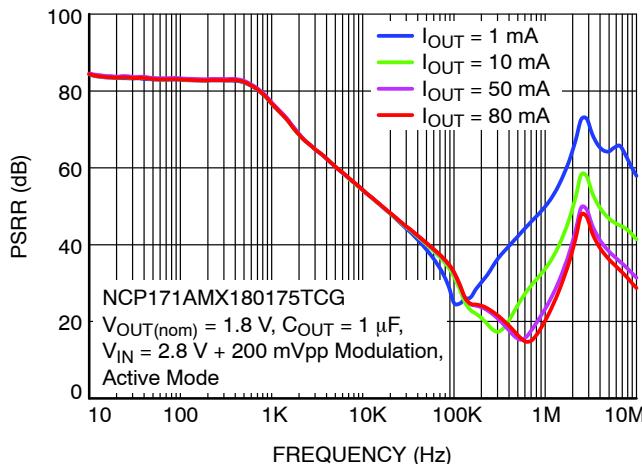

Figure 54. PSRR vs. Frequency in Low Power Mode

Figure 55. PSRR vs. Frequency in Active Mode

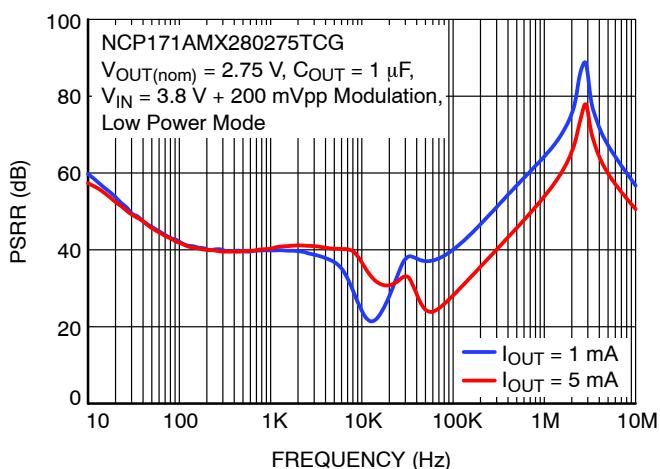

Figure 56. PSRR vs. Frequency in Low Power Mode

Figure 57. PSRR vs. Frequency in Active Mode

## TYPICAL CHARACTERISTICS

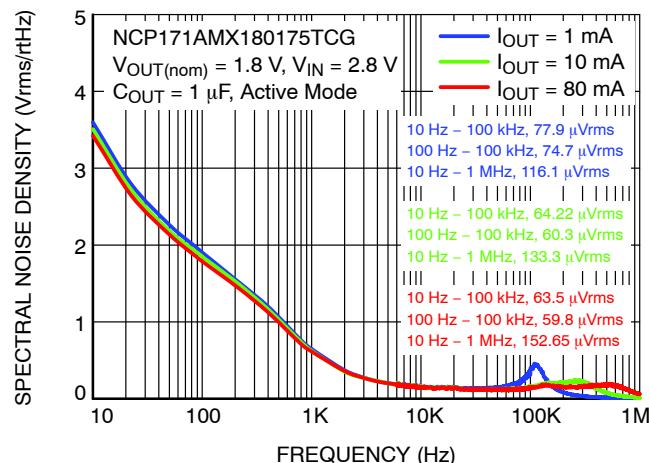

Figure 58. Noise vs. Frequency

Figure 59. Noise vs. Frequency

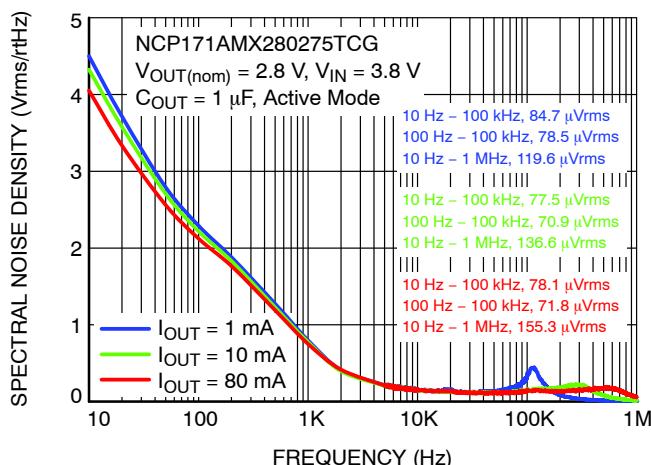

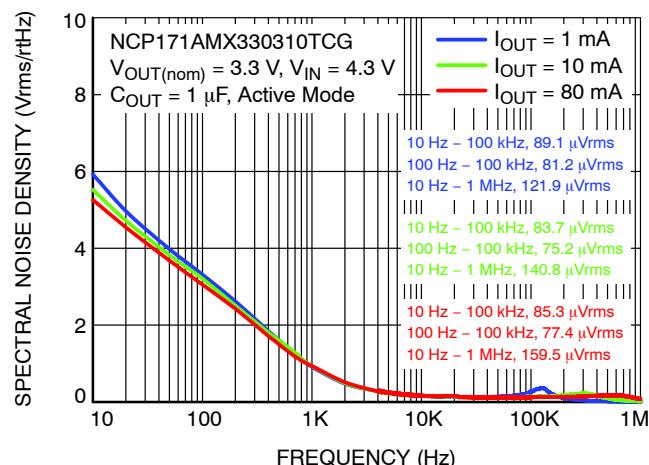

Figure 60. Noise vs. Frequency

Figure 61. Noise vs. Frequency

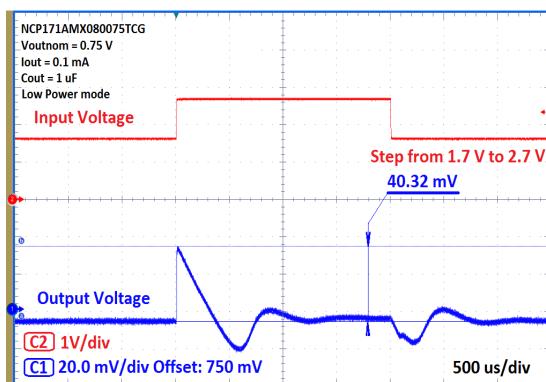

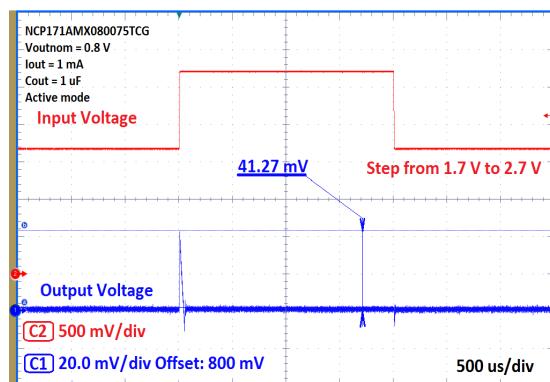

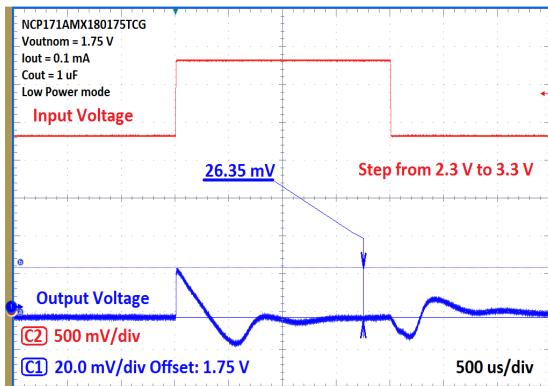

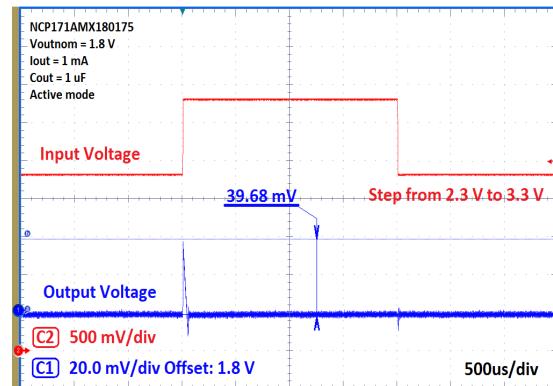

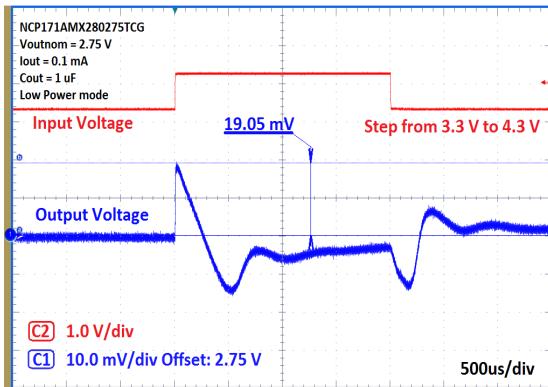

Figure 62. Line Transient Response in Low Power Mode

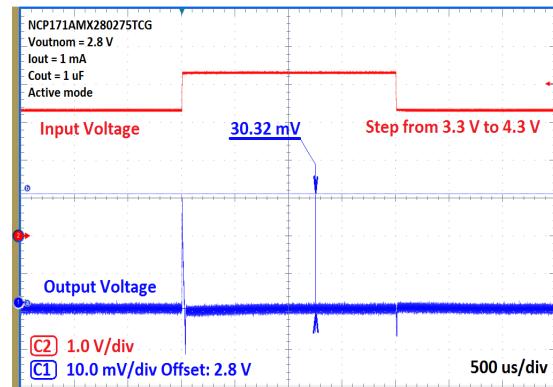

Figure 63. Line Transient Response in Active Mode

## TYPICAL CHARACTERISTICS

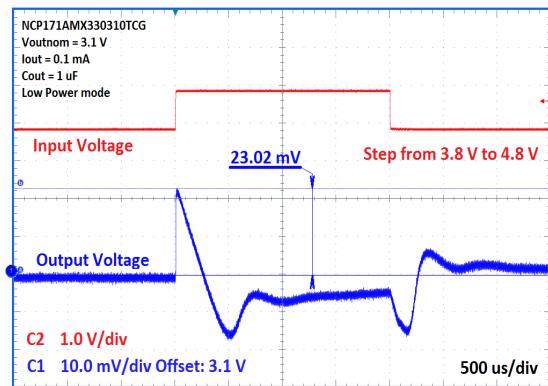

Figure 64. Line Transient Response in Low Power Mode

Figure 65. Line Transient Response in Active Mode

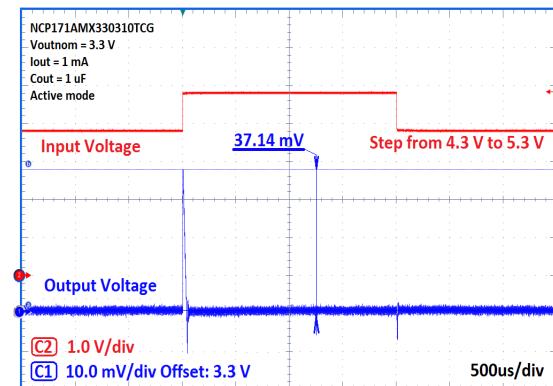

Figure 66. Line Transient Response in Low Power Mode

Figure 67. Line Transient Response in Active Mode

Figure 68. Line Transient Response in Low Power Mode

Figure 69. Line Transient Response in Active Mode

## TYPICAL CHARACTERISTICS

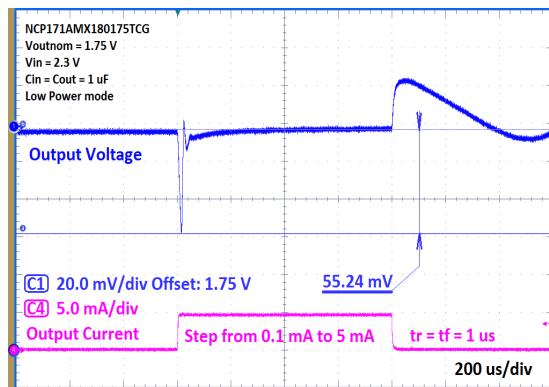

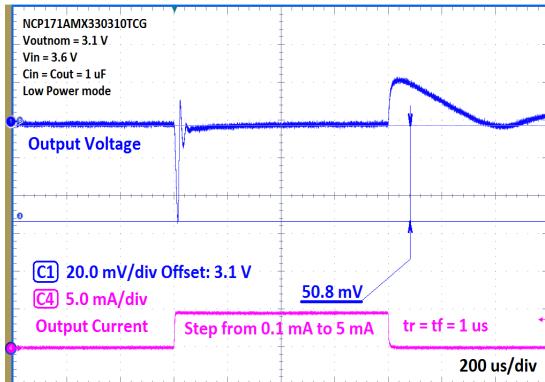

Figure 70. Load Transient Response in Low Power Mode

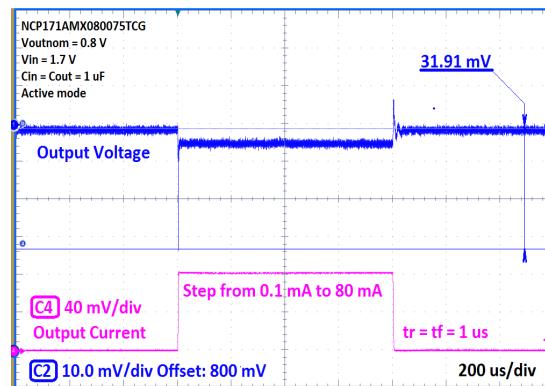

Figure 71. Load Transient Response in Active Mode

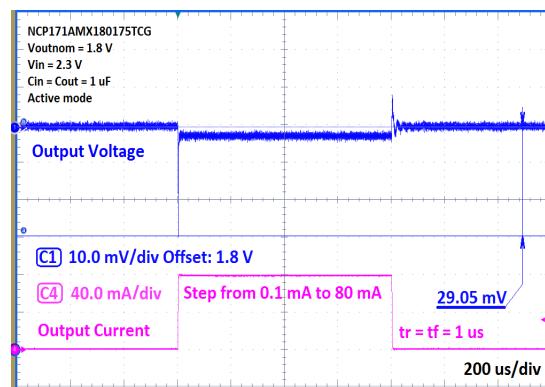

Figure 72. Load Transient Response in Low Power Mode

Figure 73. Load Transient Response in Active Mode

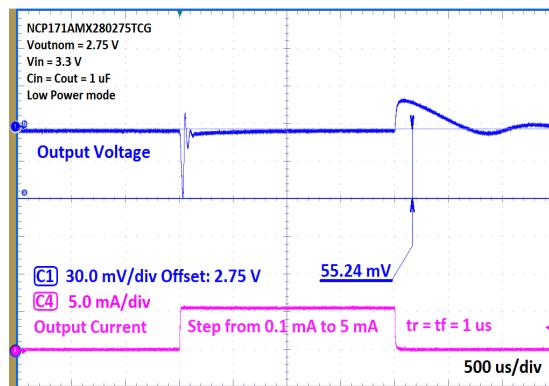

Figure 74. Load Transient Response in Low Power Mode

Figure 75. Load Transient Response in Active Mode

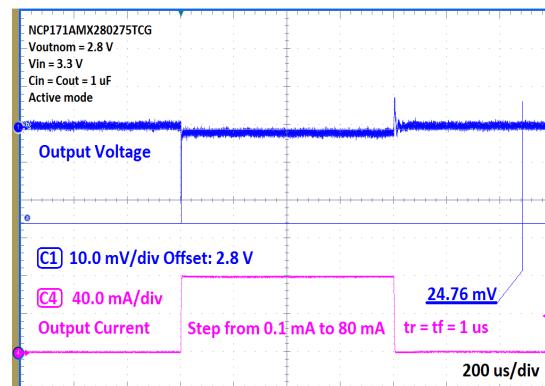

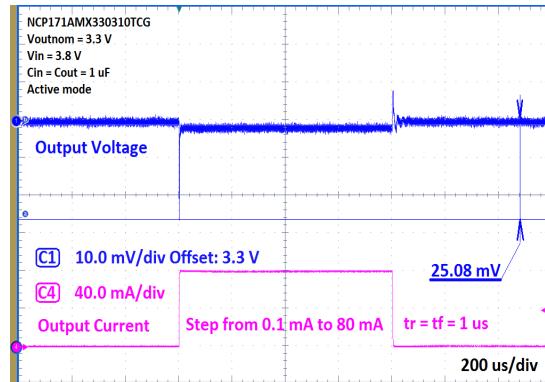

## TYPICAL CHARACTERISTICS

Figure 76. Load Transient Response in Low Power Mode

Figure 77. Load Transient Response in Active Mode

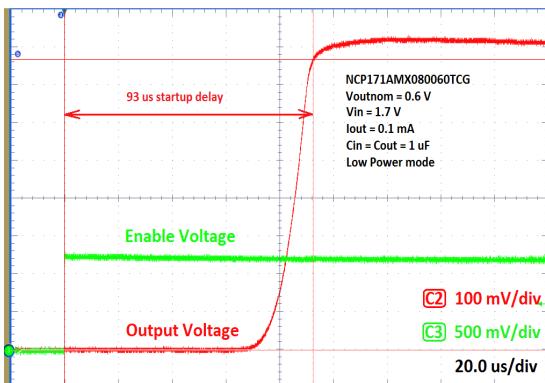

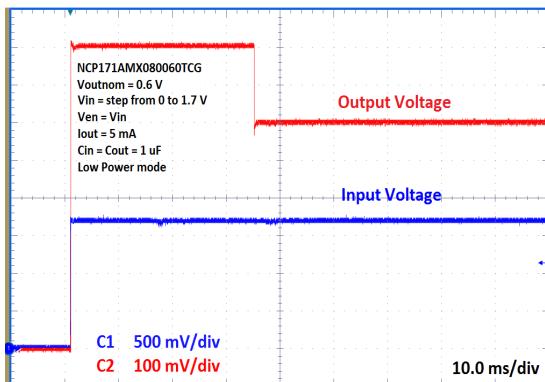

Figure 78. Startup by Enable in Low Power Mode

Figure 79. Startup by Enable in Low Power Mode

Figure 80. Startup by Input Voltage in Low Power Mode

Figure 81. Output Voltage vs. ECO Voltage

## TYPICAL CHARACTERISTICS

Figure 82. Transition from Low Power Mode to Active Mode

Figure 83. Transition from Active Mode to Low Power Mode

## ORDERING INFORMATION

| Device              | Nominal Output Voltage | Output Voltage Offset | Marking | Active Discharge | Package | Shipping <sup>†</sup> |

|---------------------|------------------------|-----------------------|---------|------------------|---------|-----------------------|

| NCP171AMX080075TCG  | 0.8 V                  | 50 mV                 | JA      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX080060TCG  | 0.8 V                  | 200 mV                | JT      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX100080TCG  | 1.0 V                  | 200 mV                | JP      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX120100TCG  | 1.2 V                  | 200 mV                | JM      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX165160TCG  | 1.65 V                 | 50 mV                 | JL      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX170165TCG  | 1.7 V                  | 50 mV                 | JN      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171A3MX170165TCG | 1.7 V                  | 50 mV                 | JQ      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX180175TCG  | 1.8 V                  | 50 mV                 | JU      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX250245TCG  | 2.5 V                  | 50 mV                 | JD      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX280275TCG  | 2.8 V                  | 50 mV                 | JH      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX330325TCG  | 3.3 V                  | 50 mV                 | JE      | Yes              | XDFN4   | 3000 / Tape & Reel    |

| NCP171AMX330310TCG  | 3.3 V                  | 200 mV                | JF      | Yes              | XDFN4   | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

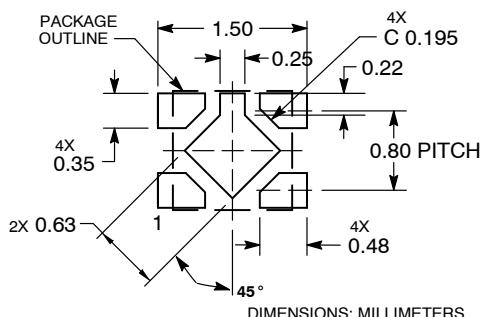

# MECHANICAL CASE OUTLINE

## PACKAGE DIMENSIONS

ON Semiconductor®

SCALE 4:1

### XDFN4 1.2x1.2, 0.8P

#### CASE 711BC

#### ISSUE O

DATE 15 SEP 2015

### RECOMMENDED MOUNTING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERMM/D.

#### NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.20 mm FROM THE TERMINAL TIPS.

4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

| MILLIMETERS |          |      |

|-------------|----------|------|

| DIM         | MIN      | MAX  |

| A           | 0.35     | 0.45 |

| A1          | 0.00     | 0.05 |

| A3          | 0.13 REF |      |

| b           | 0.25     | 0.35 |

| b1          | 0.15     | 0.25 |

| D           | 1.15     | 1.25 |

| D2          | 0.58     | 0.68 |

| E           | 1.15     | 1.25 |

| E2          | 0.58     | 0.68 |

| e           | 0.80 BSC |      |

| L           | 0.25     | 0.35 |

| L1          | 0.13     | 0.23 |

### GENERIC MARKING DIAGRAM\*

XX = Specific Device Code

M = Date Code

\*This information is generic. Please refer to device data sheet for actual part marking.

Pb-Free indicator, "G" or microdot "■", may or may not be present.

|                  |                      |                                                                                                                                                                                     |

|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOCUMENT NUMBER: | 98AON04908G          | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |

| DESCRIPTION:     | XDFN4, 1.2X1.2, 0.8P | PAGE 1 OF 1                                                                                                                                                                         |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

**onsemi, ONSEMI, and other names, marks, and brands** are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "**onsemi**" or its affiliates and/or subsidiaries in the United States and/or other countries. **onsemi** owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of **onsemi**'s product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). **onsemi** reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and **onsemi** makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Email Requests to: [orderlit@onsemi.com](mailto:orderlit@onsemi.com)

**onsemi** Website: [www.onsemi.com](http://www.onsemi.com)

### TECHNICAL SUPPORT

#### North American Technical Support:

Voice Mail: 1 800-282-9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

#### Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[onsemi:](#)

[NCP171AMX080060TCG](#) [NCP171AMX080075TCG](#) [NCP171AMX100080TCG](#) [NCP171AMX120100TCG](#)

[NCP171AMX165160TCG](#) [NCP171AMX170165TCG](#) [NCP171AMX180175TCG](#) [NCP171AMX280275TCG](#)

[NCP171AMX330310TCG](#) [NCP171AMX330325TCG](#) [NCP171A3MX170165TCG](#)