# MCX W23

**Ultra-low power, small footprint Bluetooth Low Energy solution with integrated flash and security for IoT**

Rev. 2.0 — 20 June 2025

Product data sheet

## 1 General description

The MCX W23 constitutes a highly integrated, single chip ultra-low power Bluetooth Low Energy 5.3 wireless transceiver with embedded microcontroller and flash, targeted at Internet of things (IoT) applications.

Because of the integrated ultra-low power radio and flash, the MCX W23 provides an extended battery lifetime.

The MCX W23 provides a cost-effective solution within a small solution area required for body-worn sensors and actuators application. The MCX W23 chip integrates the following key functionality:

- An Arm Cortex-M33 with floating point unit (FPU) and memory protection unit (MPU) for application control and Bluetooth Low Energy host stack

- The Arm Cortex-M33 provides a security foundation, offering isolation to protect valuable software IP and data with TrustZone-M technology.

- To support safety and security requirements, the MCX W23 also offers support for SHA-1, SHA2-256, AES, RSA, error code correction, UUID, dynamic encryption and decryption of embedded flash memory with the PRINCE engine, secure boot, protected flash regions, physical unclonable function (PUF) for key store protection and debug authentication.

- A 2.4 GHz RF transceiver supporting Bluetooth Low Energy 5.3

- A low-power 32 MHz crystal oscillator

- 32-bit real-time clock (RTC) with 1 s resolution running in the always-on power domain. Another timer in the RTC can be used for wake-up from all low-power modes, including deep power-down, with 1 ms resolution. The 32.768 kHz free running oscillator (FRO\_32k) or a 32.768 kHz external crystal clocks the RTC.

- Integrated flash memory with error code correction, which enables autonomous operation or operation with a host microcontroller.

- Multiple interfaces for control, data, debug, and test

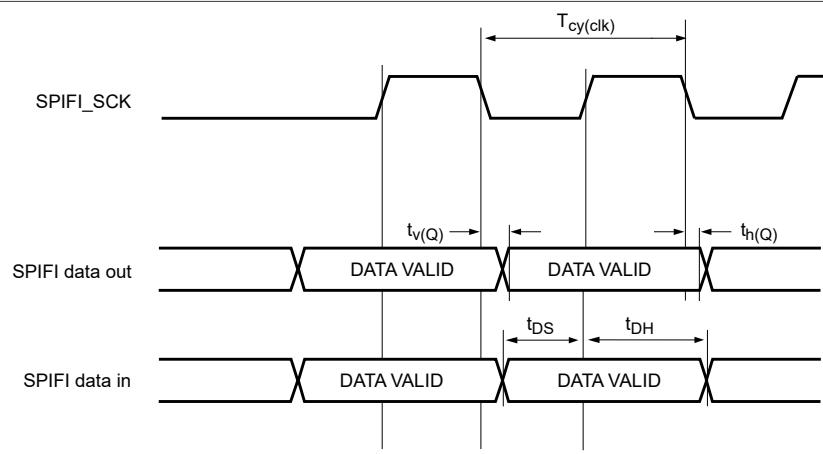

- SPIFI with execute-in-place (XIP) feature uses up to four data lines to access off-chip SPI/DSPI/QSPI flash memory at a higher rate than standard SPI interfaces.

- Flexible power management:

- MXCW23xB

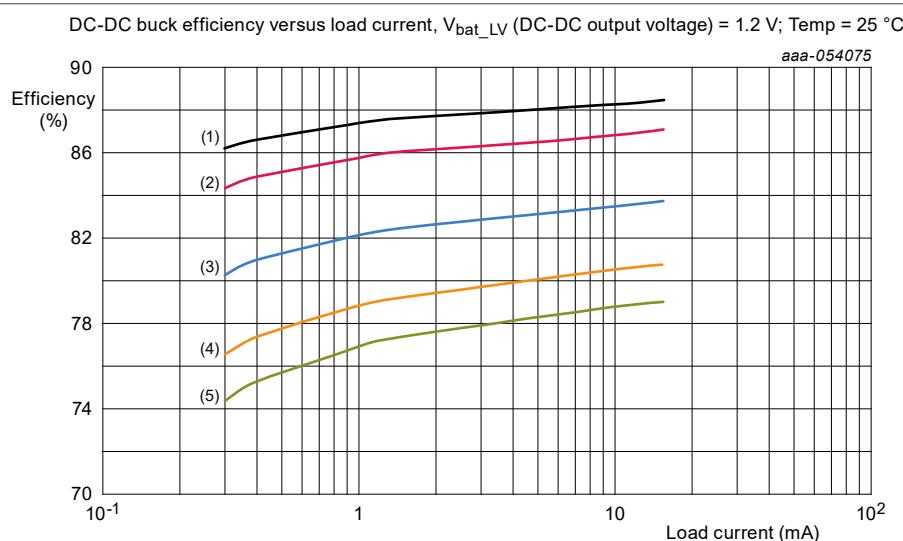

- High-voltage supply mode (HV\_SM) for 3 V battery support using integrated buck DC-DC converter

- External regulated supply mode (XR\_SM) for PMIC support (bypassing the integrated DC-DC converter)

- High integration, which enables a small solution size

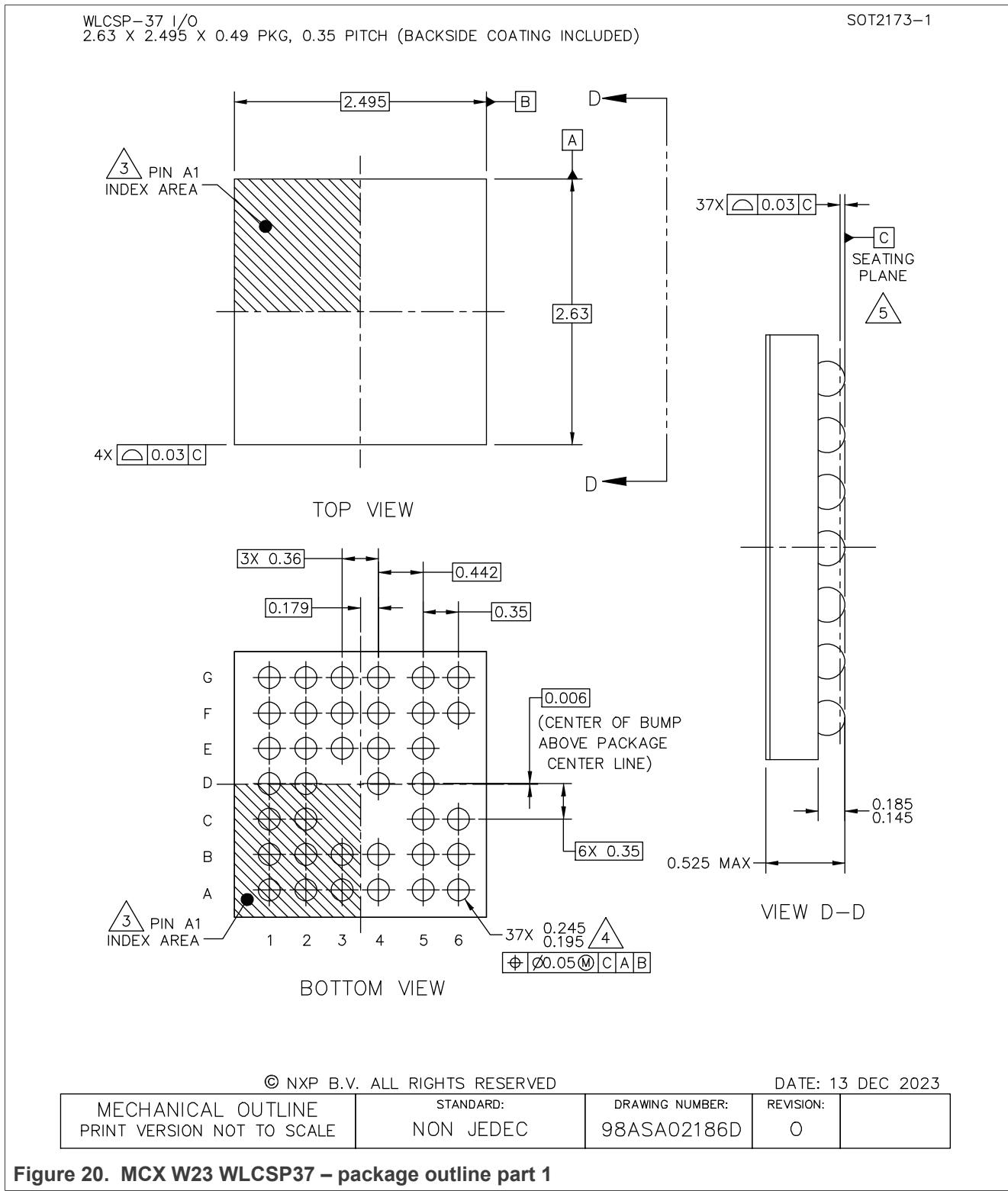

The MCX W23 is offered in a WLCSP37 or QFN40 package.

## CAUTION

Semiconductors devices are sensitive to light. Exposure to light sources might cause the WLCSP package variant of the MCX W23 to malfunction.

The MCX W23 WLCSP needs protection from all sides against light.

## 2 Features and benefits

- Arm Cortex-M33

- up to 32 MHz

- TrustZone-M® enabled

- Floating point unit (FPU)

- Memory protection unit (MPU)

- Serial wire debug (SWD) with eight break points and four watch points

- Controller subsystem memories:

- up to 1 MB of flash with cache and error code correction management, including single bit correction and double bit fault detection

- up to 128 KB RAM

- Dedicated packet RAM buffer for radio subsystem: 16 KB data RAM and 512 bytes sequencer RAM

- 256 KB of ROM

- ROM bootloader supports:

- Booting of images from an on-chip flash

- Supports CRC32 image integrity checking

- Supports flash programming through in-system programming (ISP) commands over the following interfaces: SPI slave interfaces (Flexcomm 0) using mode 3 (CPOL = 1 and CPHA = 1), I2C slave interface (Flexcomm 1), and UART interface (Flexcomm 2) with autobaud. ROM API functions: Flash programming API, MBED TLS API, and secure firmware update API using NXP secure boot file format, version 2.1 (SB2 files)

- Supports preloading a TrustZone-M® configuration before the application boots

- Supports booting of images from PRINCE encrypted flash regions

- Supports NXP Debug Authentication Protocol version 1.0 (RSA-2048) and 1.1 (RSA-4096)

- Supports setting a sealed part to fault analysis mode through debug authentication

- Supports boot seed as described in the Arm platform security architecture specification

- Supports OEM key provisioning during device manufacturing

- Secure boot support:

- Uses RSASSA-PKCS1-v1\_5 signature of SHA256 digest as cryptographic signature verification.

- Supports RSA-2048 bit public keys (2048-bit modulus, 32-bit exponent).

- Supports RSA-4096 bit public keys (4096-bit modulus, 32-bit exponent).

- Uses a x509 certificate format to validate image public keys.

- Supports up to four revocable root of trust (RoT) or certificate authority keys, root of trust (RoT) establishment by storing the SHA-256 hash digest of the SHA-256 hashes of four RoT public keys in a protected flash region (PFR).

- Supports an antirollback feature using image key revocation and supports up to 16 image key certificates revocations using the serial number field in the x509 certificate.

- Two flexible DMA engines

- Control/data interfaces

- Three FlexComm: Each FlexComm can be configured as an SPI, UART, or I<sup>2</sup>C interface

- SPIFI: Quad SPI interface for external serial flash support with execute-in-place (XIP)

- Up to 23 GPIO

- Security features

- Arm TrustZone-M® enabled.

- AES-256 encryption/decryption engine with keys fed directly from PUF or a software-supplied key.

- Secure hash algorithm (SHA1 and SHA2-256) module supports secure boot with a dedicated DMA controller.

**Ultra-low power, small footprint Bluetooth Low Energy solution with integrated flash and security for IoT**

- Physical unclonable function (PUF) using dedicated SRAM for silicon fingerprint; PUF can generate, store, and reconstruct key sizes from 64 bits to 4096 bits. Includes hardware for key extraction.

- True random number generator (TRNG) compliant to NIST SP 800-90B, NIST SP 800-22.

- 128-bit unique device serial number for identification (universal unique identifier: UUID).

- Secure GPIO.

- To enable hardware acceleration for various functions required for certain asymmetric cryptographic algorithms, such as elliptic curve cryptography (ECC) or RSA, a public key coprocessor (PKC) is provided.

- PRINCE module for real-time encryption of data written to on-chip flash and decryption of encrypted flash data during read to allow asset protection, such as securing application code, and enabling secure flash update.

- Protected flash region (PFR) is available to configure secure boot, debug authentication, read UUID, store PUF in a key store area, and user-defined fields available for specific data storage.

- The MCX W23 is compatible with the Bluetooth Low Energy 5.3 specification:

- Bluetooth Low Energy 5.3 controller subsystem (QDID 200592)

- Bluetooth Low Energy 5.3 host subsystem (QDID 226395)

- Includes a 48-bit unique Bluetooth device address

- Up to 4 simultaneous connections supported

- The MCX W23 supports the following Bluetooth Low Energy features:

- Device privacy and network privacy modes (Version 5.0)

- Advertising extension PDUs (Version 5.0)

- Anonymous device address type (Version 5.0)

- Up to 2 Mbps data rate (Version 5.0)

- Long range (Version 5.0)

- High-duty cycle, non-connectable advertising (Version 5.0)

- Channel selection algorithm #2 (Version 5.0)

- High output power (Version 5.0)

- Advertising Channel Index (Version 5.1)

- Periodic Advertising Sync Transfer (PAST) (Version 5.1)

- Supports LE power control feature (Version 5.2)

- RF antenna: 50 Ω single-ended

- RF receiver characteristics

- Sensitivity -94 dBm in Bluetooth Low Energy 2 Mbps

- Sensitivity -97 dBm in Bluetooth Low Energy 1 Mbps

- Sensitivity -100 dBm in Bluetooth Low Energy 500 kbps

- Sensitivity -102 dBm in Bluetooth Low Energy 125 kbps

- Accurate RSSI measurement with ±3 dB accuracy

- Flexible RF transmitter level configurability:

- TX mode 1 (TXM1): Range from -31 dBm to +2 dBm when  $V_{DD\_RF}$  exceeds 1.1 V

- TX mode 2 (TXM2): Range from -28 dBm to +6 dBm when  $V_{DD\_RF}$  exceeds 1.7 V

- Flexible boot modes:

- Autonomous boot from flash

- In-system programming (ISP)

- Secure bootloader, which enables OEM key provisioning by creating a root of trust for execution of authenticated and encrypted application images (SB2.1 format).

- Flexible power management:

- MXCW23xB

- High-voltage supply mode (HV\_SM) for 3 V battery support using integrated buck DC-DC converter

Ultra-low power, small footprint Bluetooth Low Energy solution with integrated flash and security for IoT

- External regulated supply mode (XR\_SM) for PMIC support (bypassing the integrated DC-DC converter)

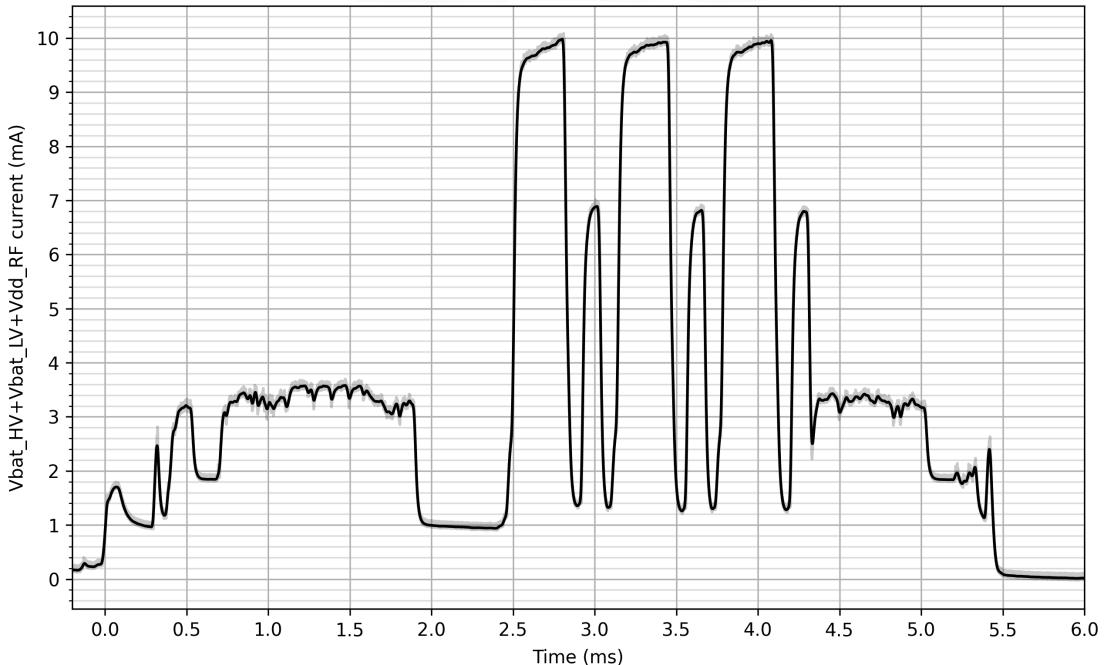

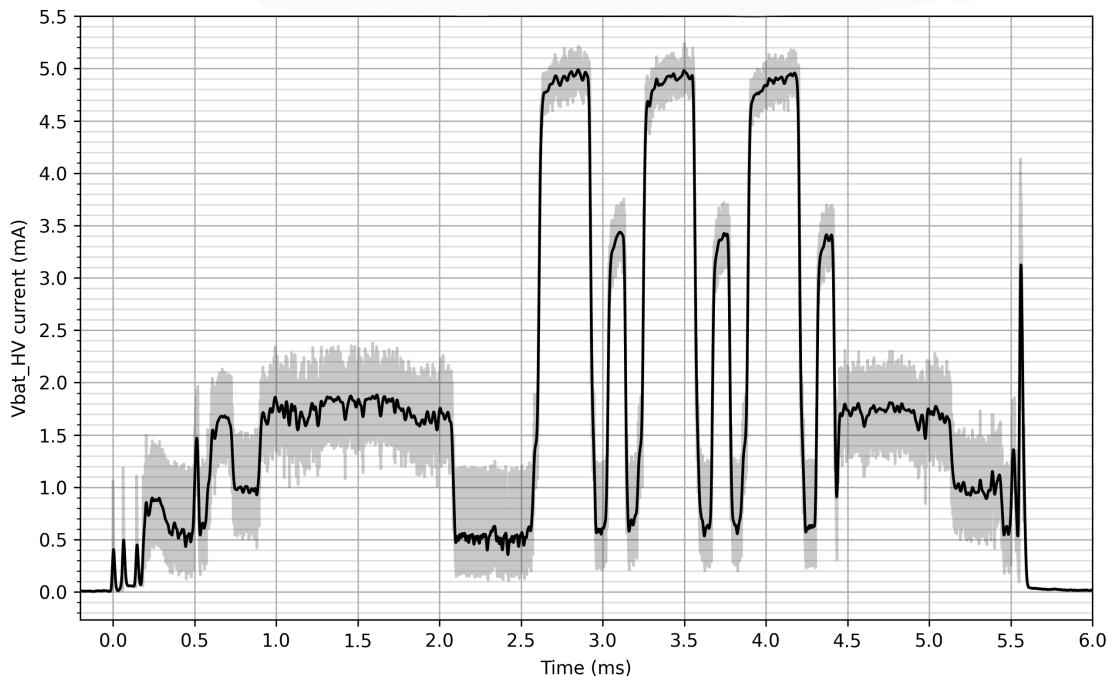

- Low current consumption at room temperature ( $T_{amb} = 25^{\circ}C$ ):

- MCX W23xB in XR\_SM mode (1.8 V)

- Power-off current: 80 nA with PIO0\_21 pin wake-up

- Deep power-down current: 650 nA with RTC FRO\_32k wake-up

- Deep power-down current: 695 nA with RTC XO\_32k wake-up

- Power-down current: 1.18  $\mu$ A (16 kB RAM retention) with RTC FRO\_32k wake-up

- Deep-sleep current: 4.50  $\mu$ A (full RAM retention) with RTC FRO\_32k wake-up

- Bluetooth Low Energy current during radio RX packet phase: 6.64 mA

- Bluetooth Low Energy current during radio TX packet phase: 9.68 mA (0 dBm output power)

- MCX W23xB in HV\_SM mode (3.0 V)

- Power-off current: 25 nA with PIO0\_21 pin wake-up

- Deep power-down current: 645 nA with RTC FRO\_32k wake-up

- Deep power-down current: 690 nA with RTC XO\_32k wake-up

- Power-down current: 1.23  $\mu$ A (16 kB RAM retention) with RTC FRO\_32k wake-up

- Deep-sleep current: 4.61  $\mu$ A (full RAM retention) with RTC FRO\_32k wake-up

- Bluetooth Low Energy current during radio RX packet phase : 3.33 mA

- Bluetooth Low Energy current during radio TX packet phase : 4.83 mA (0 dBm output power)

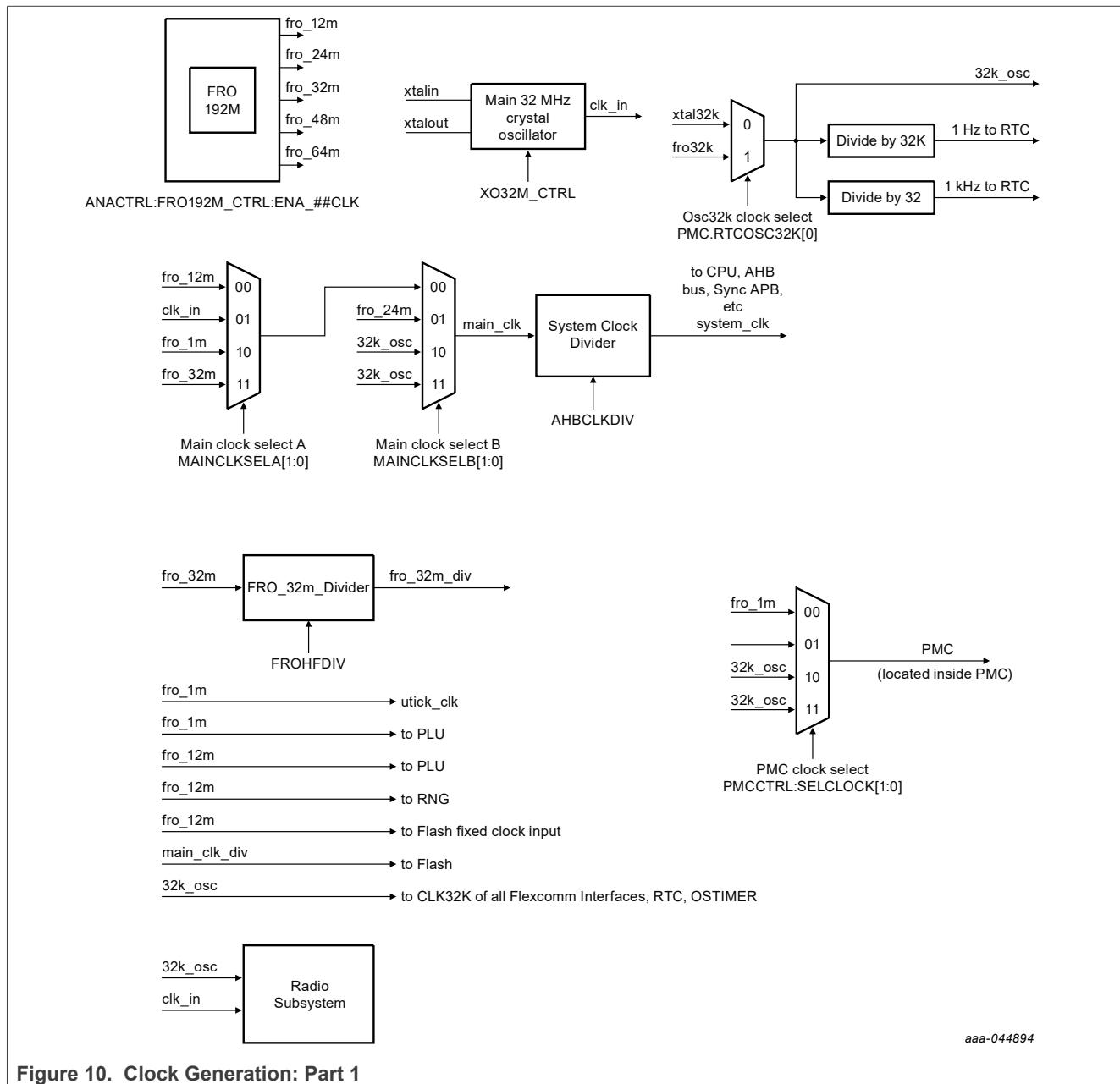

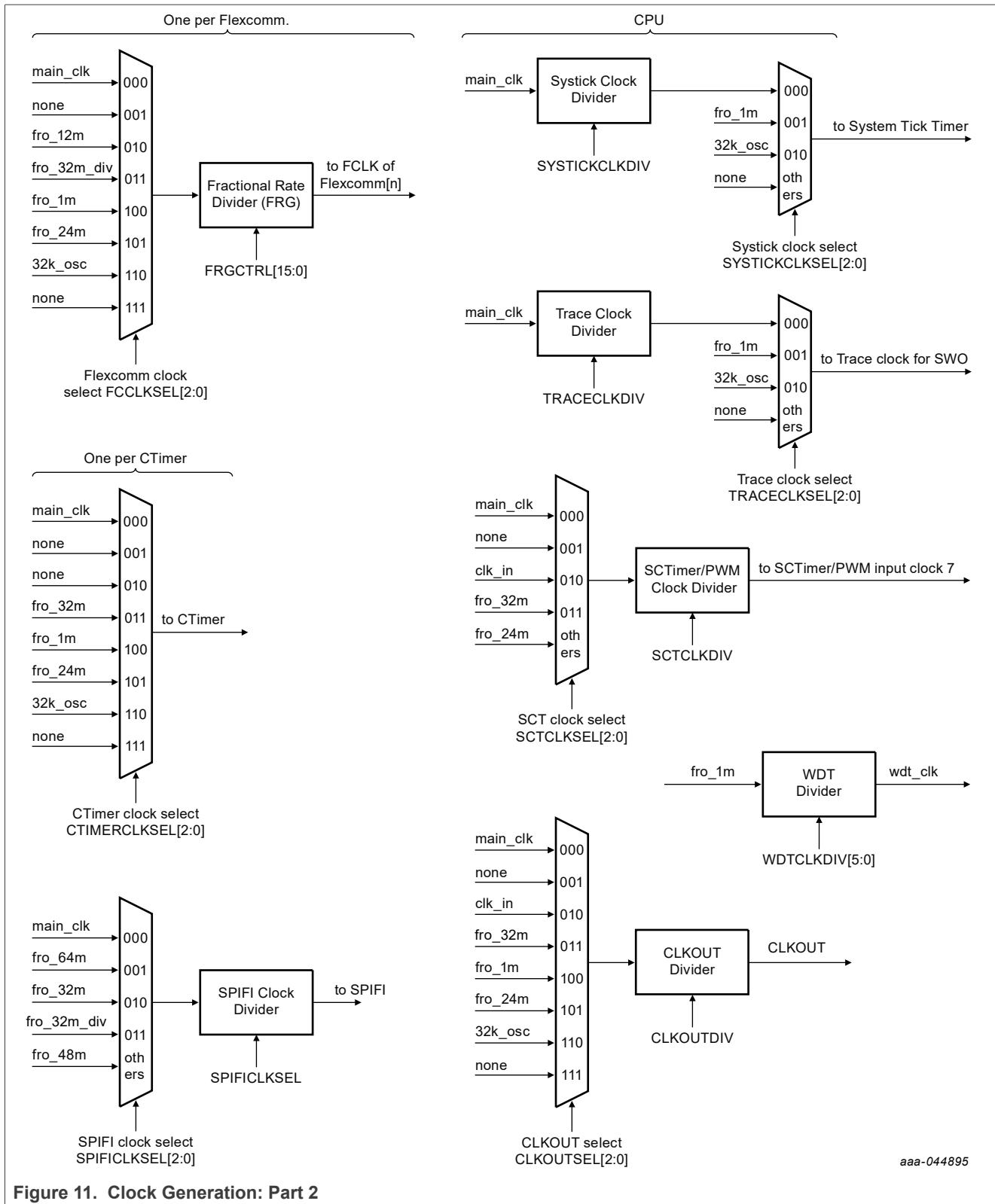

- Clock generation:

- Integrated low-power high-frequency free running oscillator (FRO) providing a set of selectable outputs, 32 MHz, 24 MHz, and 12 MHz

- Crystal oscillator for a 32 MHz crystal required for radio functionality (XO\_32M)

- Integrated 32.768 kHz ultra-low power free running oscillator (FRO\_32k)

- Crystal oscillator for a 32.768 kHz crystal (XO\_32k)

- Integrated 1 MHz ultra-low power free running oscillator (FRO\_1M)

- Timers:

- 5 Standard timer/counters (CTIMER)

- Windowed watchdog timer (WWDT)

- Real-time clock (RTC)

- Multirate timer (MRT)

- Microtick timer (UTICK)

- SCTimer/PWM

- 42-bit free running OS Timer

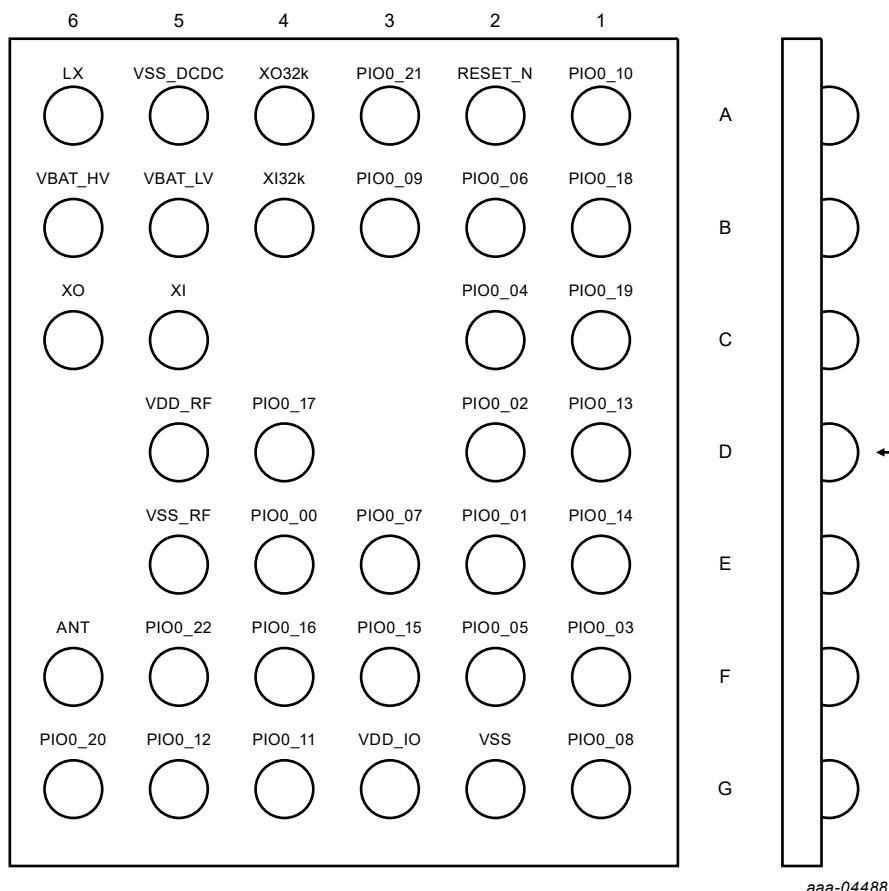

- Packaging:

- WLCSP package: 6.56 mm<sup>2</sup> with 37 bumps

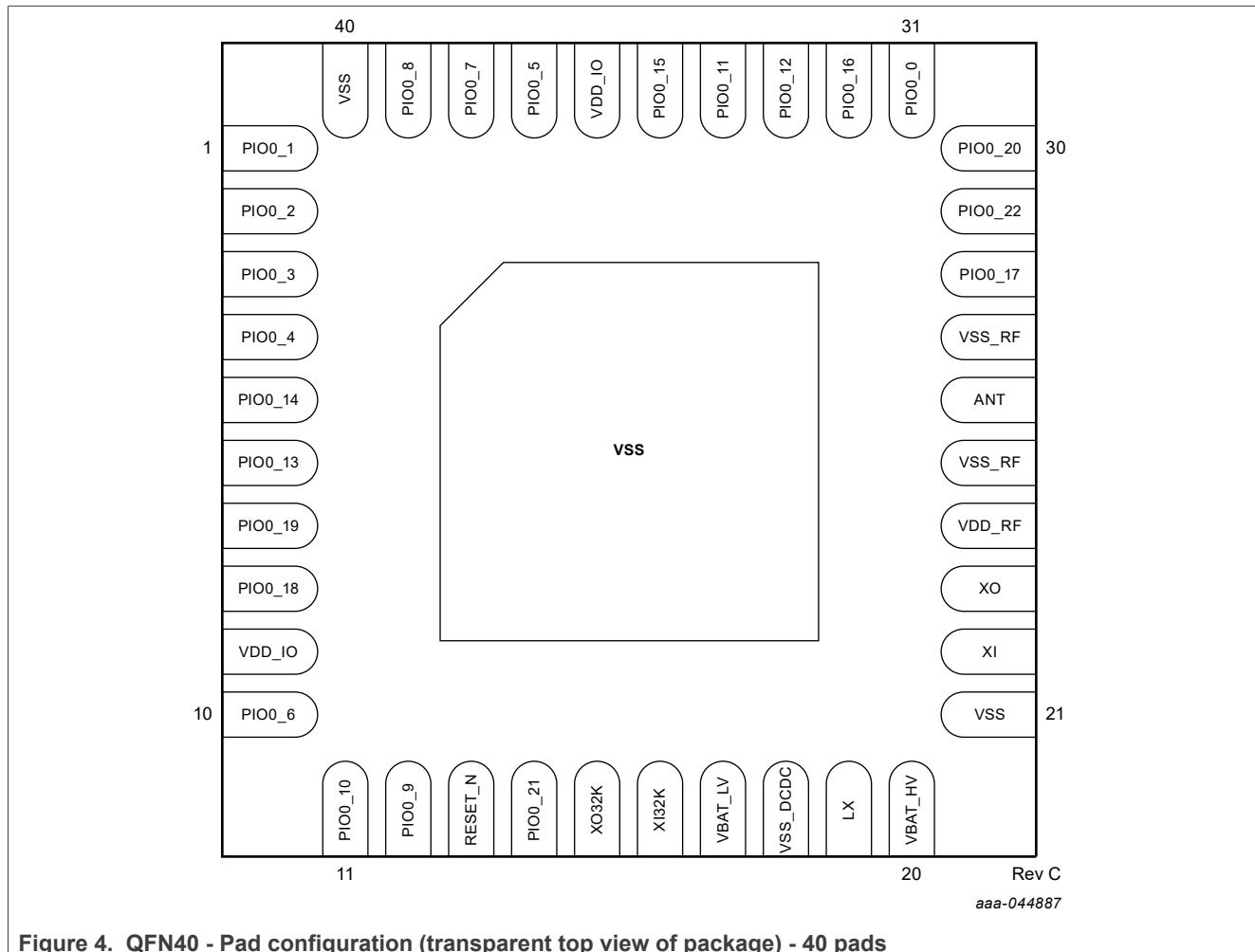

- QFN package: 5 mm × 5 mm with 40 pins

- Easy development:

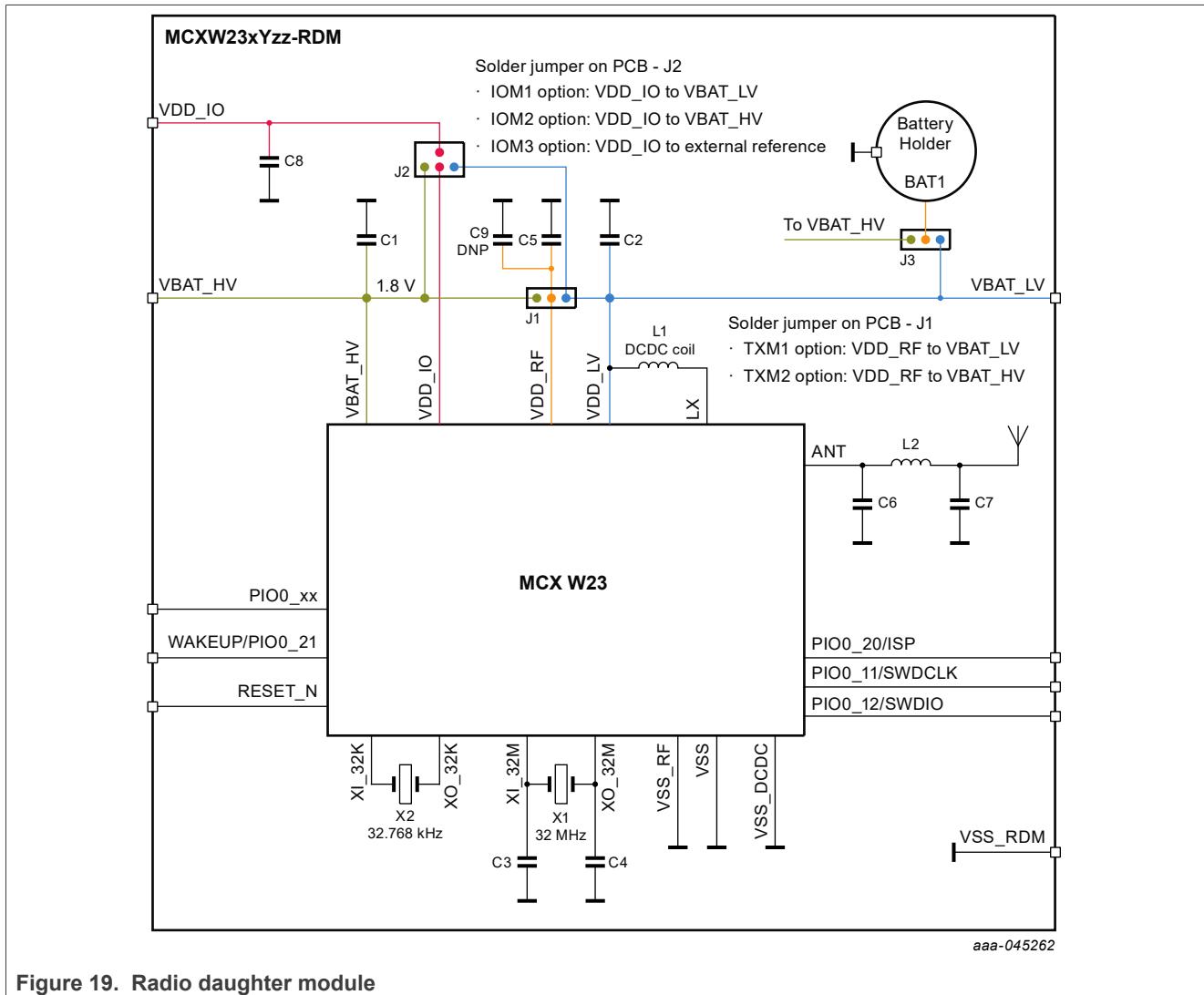

- EVK board containing MCX W23 with support interfaces for SW development

- MCUXpresso integrated development environment (IDE) brings developers an easy-to-use Eclipse-based development environment

- Source code for the peripheral drivers

- Bluetooth Low Energy host stack

- Low number of external passive components

- Operating temperature:  $-40^{\circ}C$  to  $+85^{\circ}C$

- Pb-free and compliant with RoHS Directive EU 2015/863 (RoHS 3)

### 3 Applications

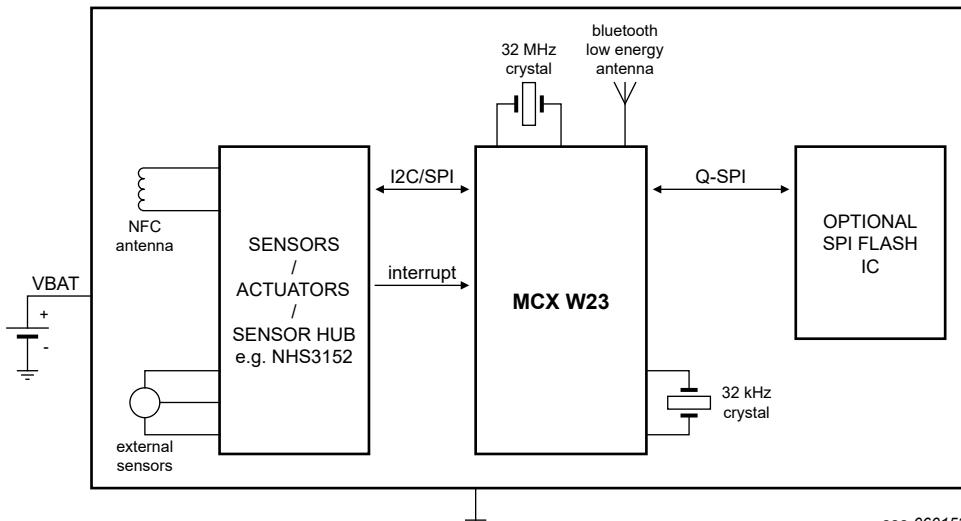

The main application targets of the MCX W23 are Internet of things (IoT) applications running directly from a coin battery in a small body-worn device.

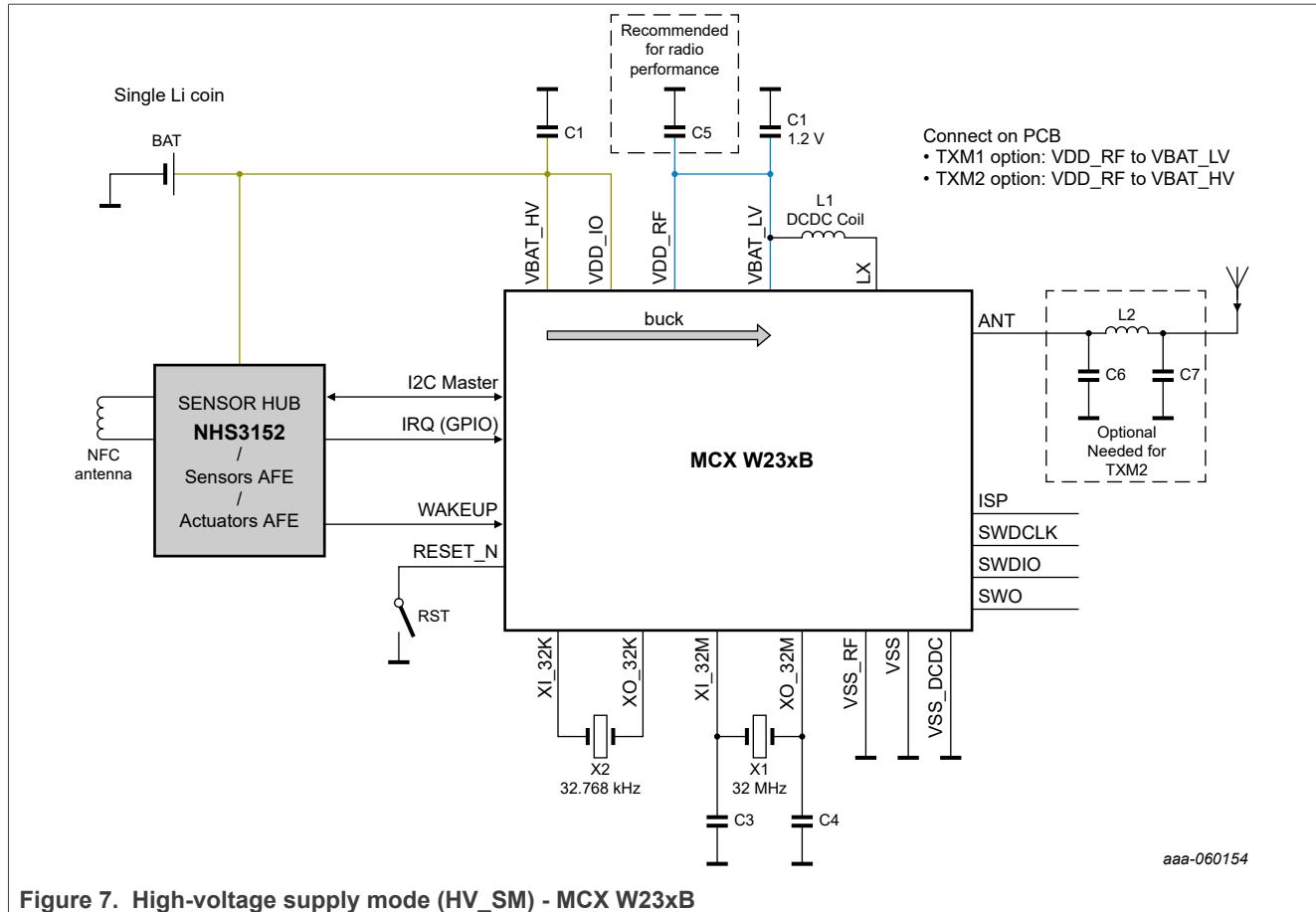

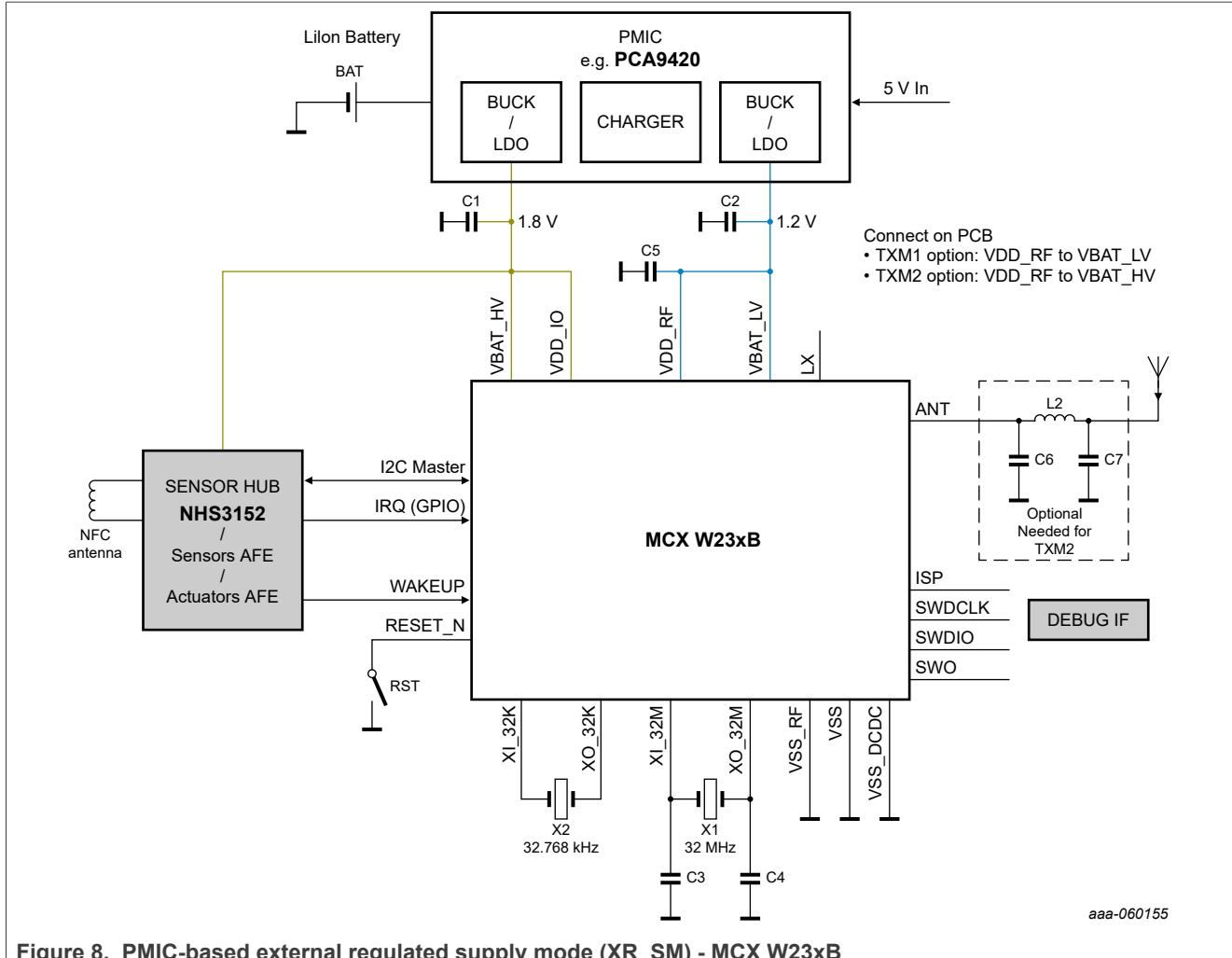

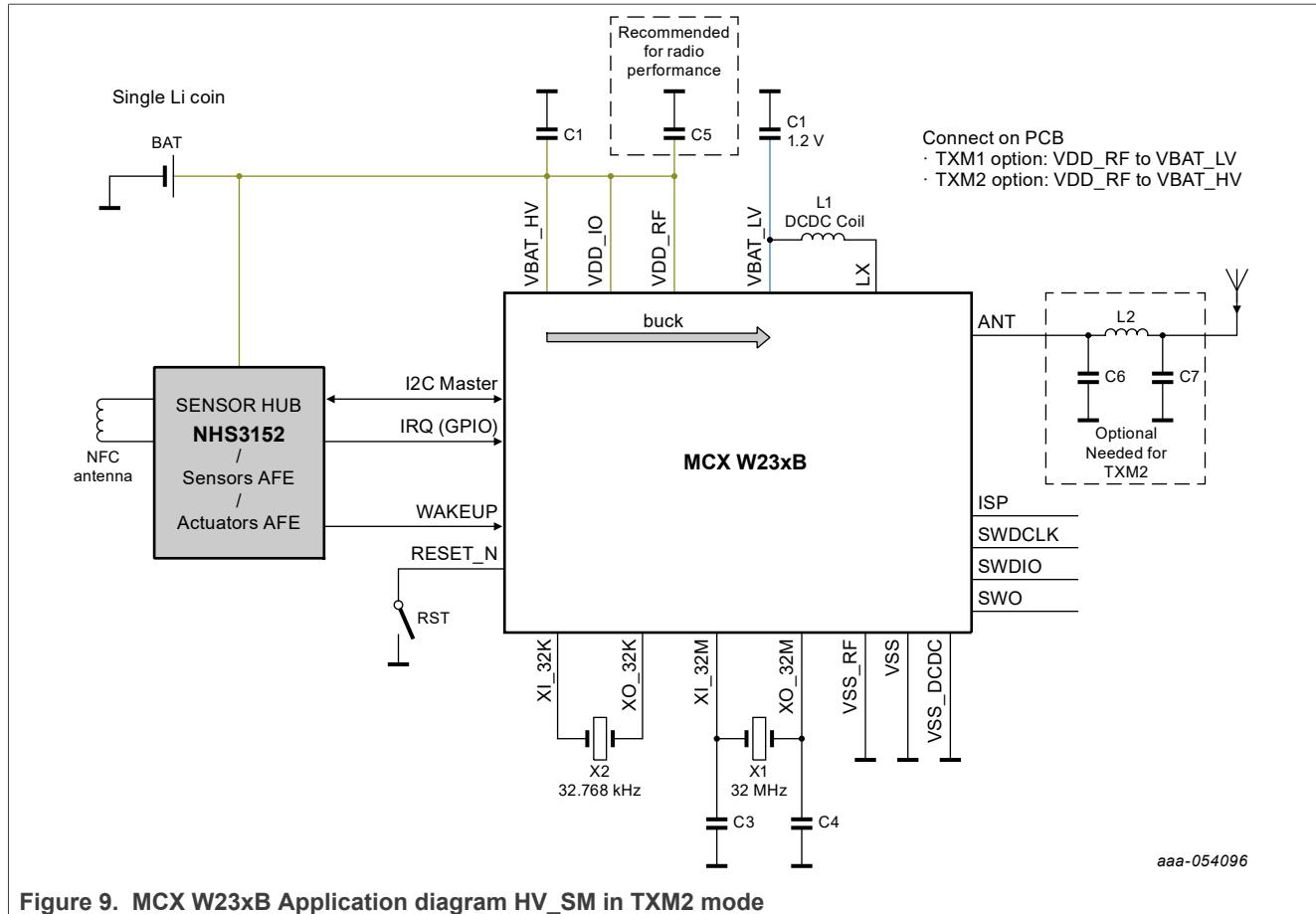

The MCX W23 family supports the following supply configurations:

- MCX W23xB is used with 3 V battery (for example, Li coincell) attached to the VBAT\_HV pin. The DC-DC converter gets configured as a buck converter and generates a 1.2 V output supply on VBAT\_LV pin for the internal logic, the external sensors, and the radio subsystem. This mode is called high-voltage supply mode (HV\_SM).

- MCX W23xB can also be used in a system with external PMIC. The integrated DC-DC converter can be disabled. To reduce system costs, no inductor is necessary. This mode is called external regulated supply mode (XR\_SM).

The integrated Arm Cortex-M33 provides a flexible, secure, and high-performance environment for developing sensor and actuator applications.

The system supports optional features, for example:

- An external SPI flash for data logging applications and execute-in-place (XIP)

Figure 1. Typical application diagram of the MCX W23

## 4 Ordering information

**Table 1. Ordering information**

| Type number   | Flash<br>(KB) | RAM<br>(KB) | DCDC                                        | Package | Package<br>Reference |

|---------------|---------------|-------------|---------------------------------------------|---------|----------------------|

| MCXW236BIUKAR | 1024          | 128         | Supports HV_SM (Buck) and XR_SM (PMIC) mode | WLCSP37 | SOT2173-1            |

| MCXW236BIHNAR | 1024          | 128         | Supports HV_SM (Buck) and XR_SM (PMIC) mode | HVQFN40 | SOT1369-5            |

| MCXW235BIUKAR | 640           | 96          | Supports HV_SM (Buck) and XR_SM (PMIC) mode | WLCSP37 | SOT2173-1            |

| MCXW235BIHNAR | 640           | 96          | Supports HV_SM (Buck) and XR_SM (PMIC) mode | HVQFN40 | SOT1369-5            |

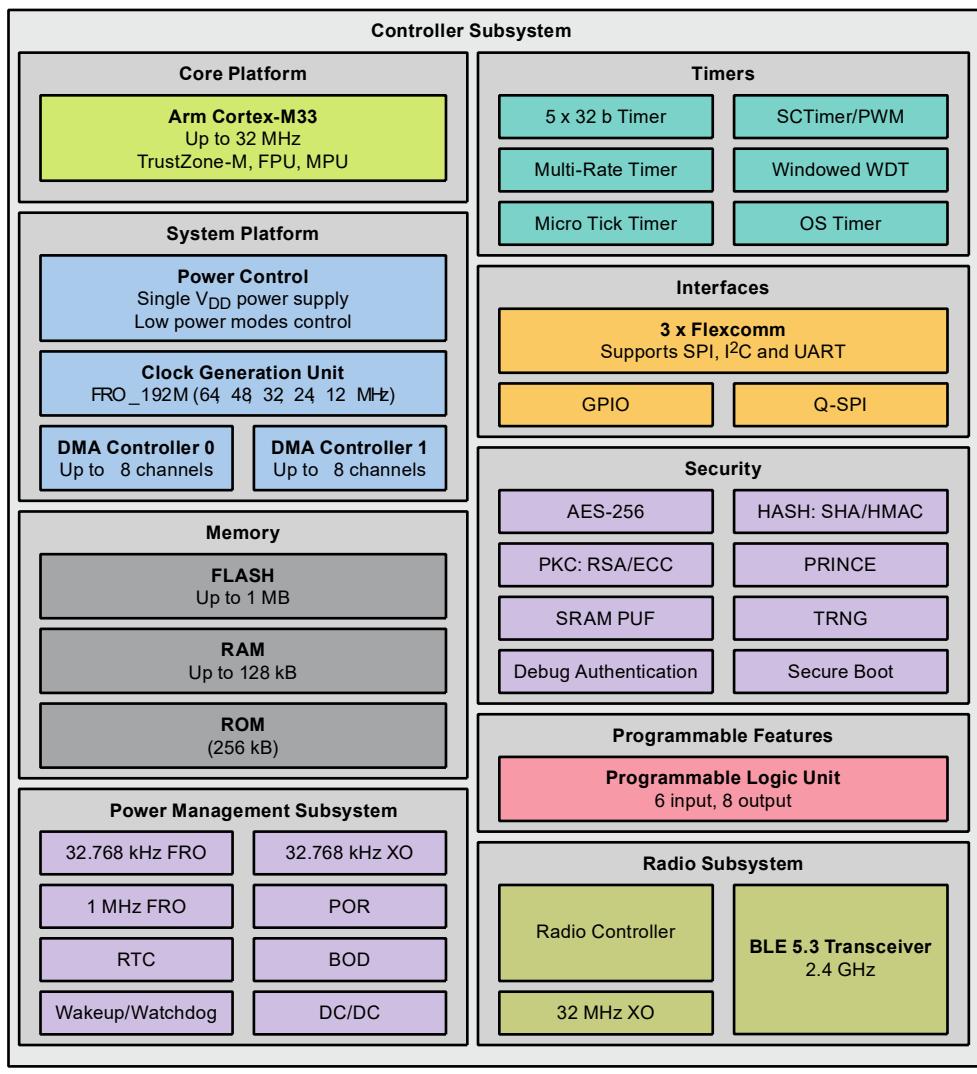

## 5 Block diagram

Figure 2. MCX W23 block diagram

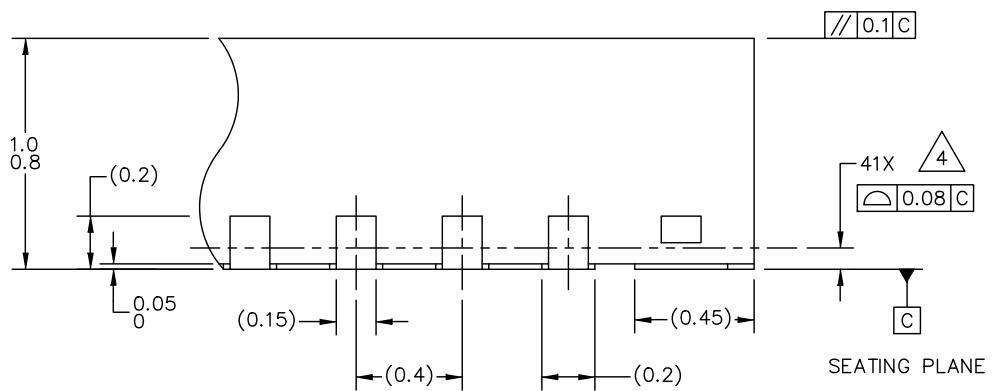

## 6 Package and pinning information

This section gives an overview of the package and pinning of the MCX W23.

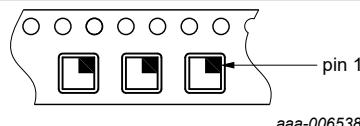

### 6.1 WLCSP package

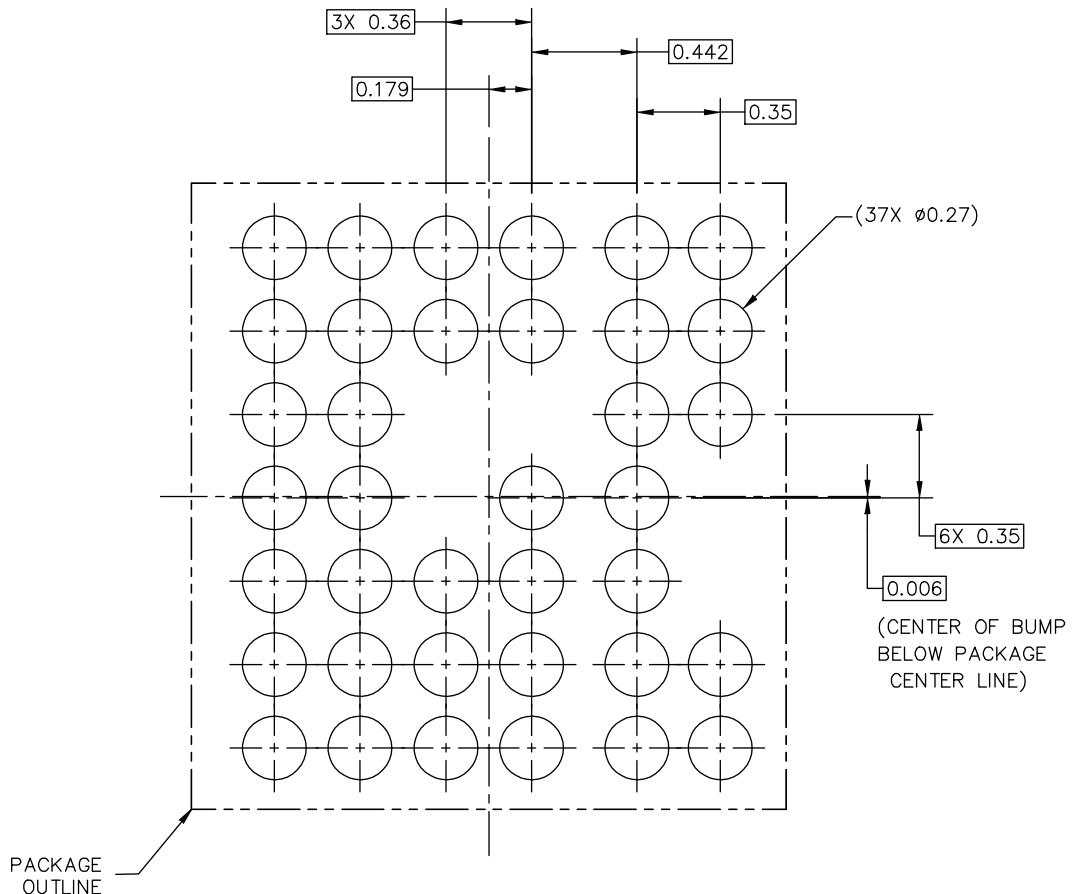

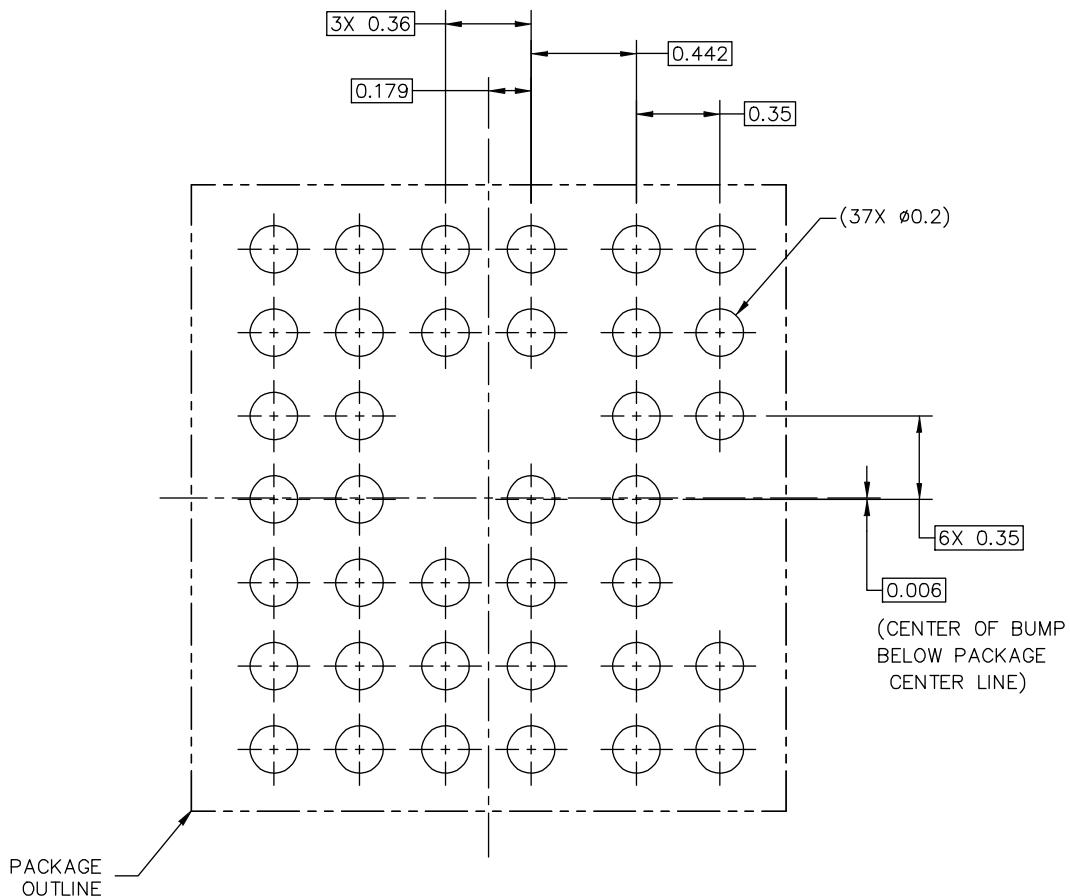

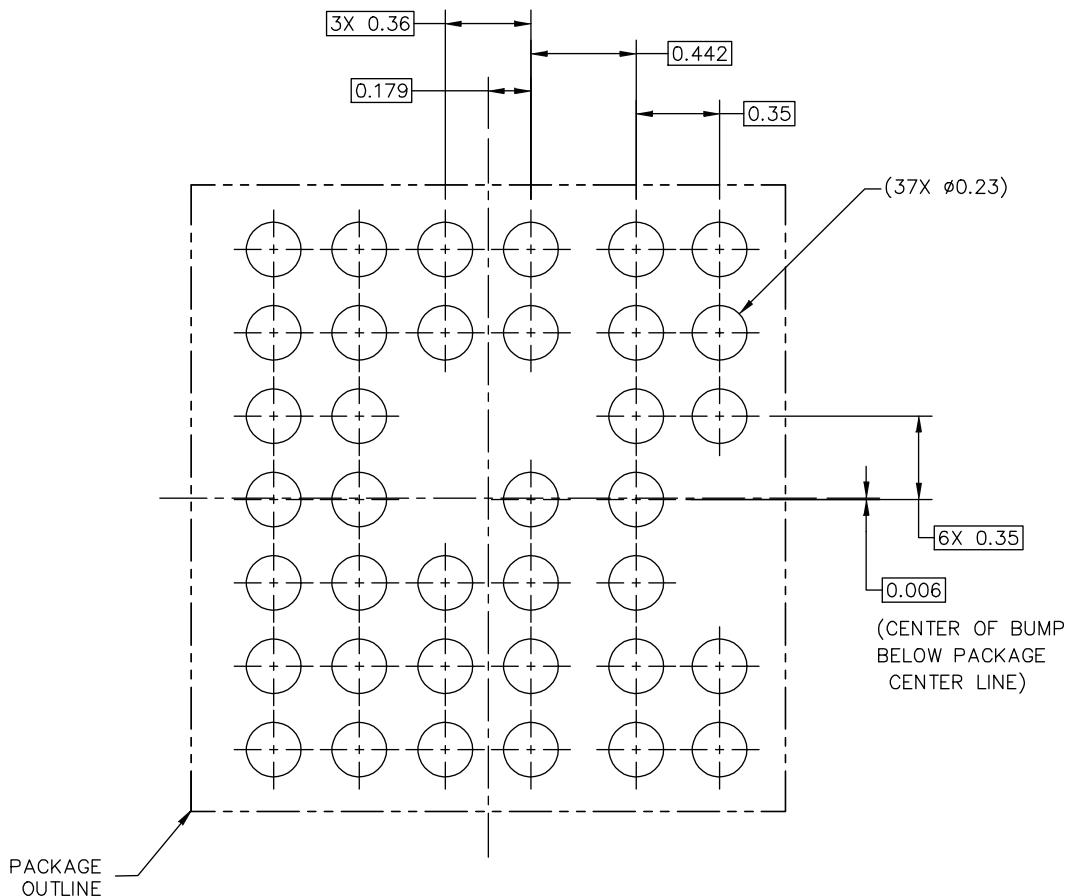

Figure 3. MCX W23 WLCSP - Bump configuration (bottom view of package) - 7 x 6 grid: 37 bumps

[Figure 3](#) show the MCX W23 WLCSP bump layout.

To optimize radio performance, bumps D6 and E6 are depopulated.

To provide space for vias, bumps D3, C3, and C4 are depopulated.

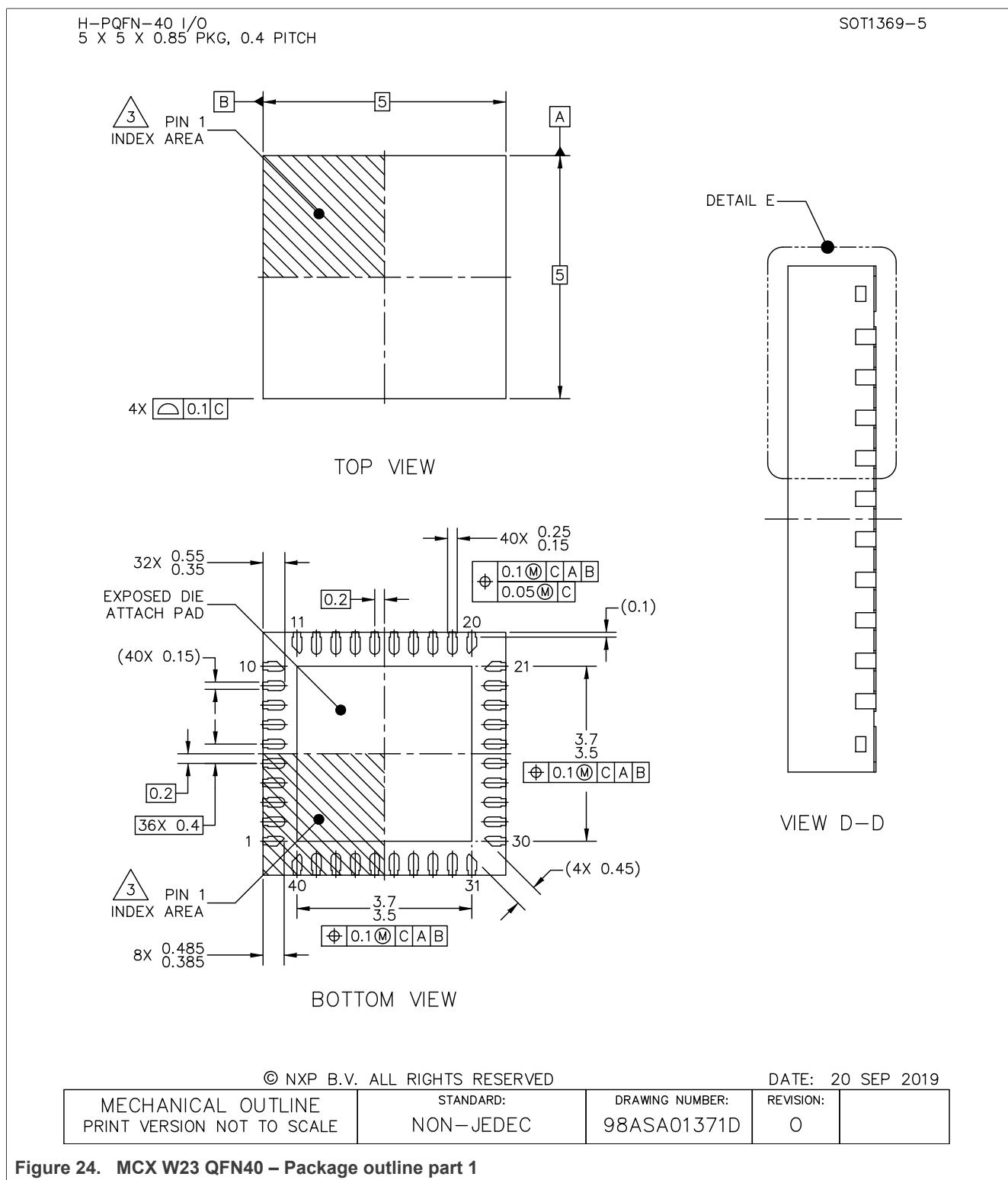

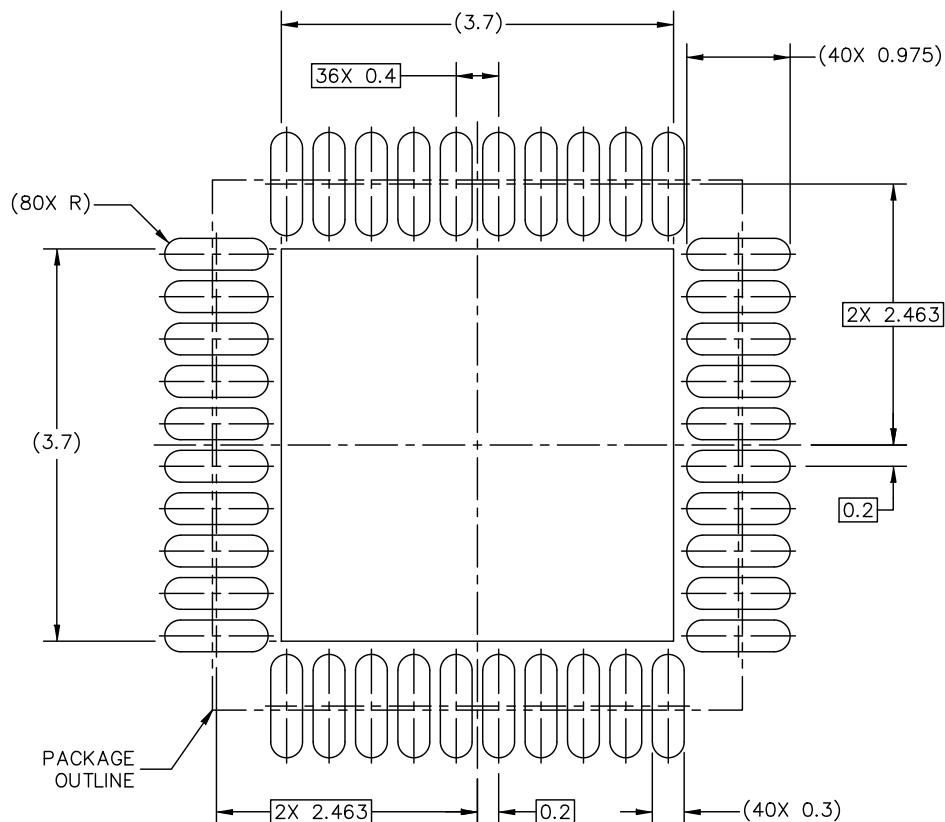

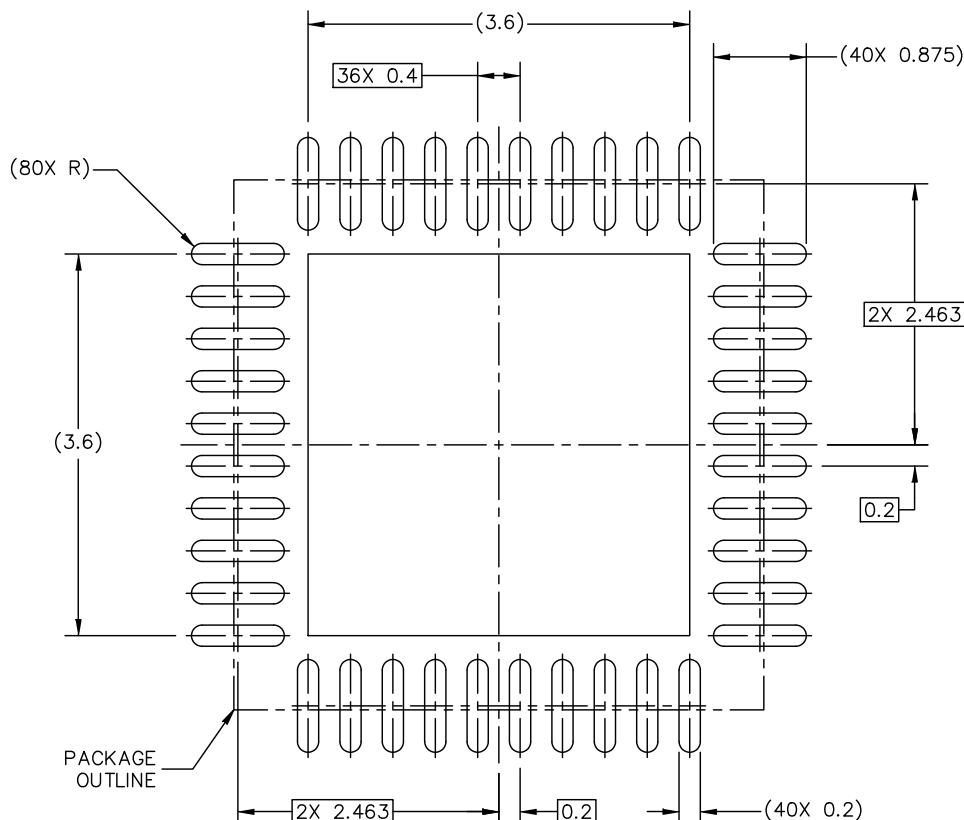

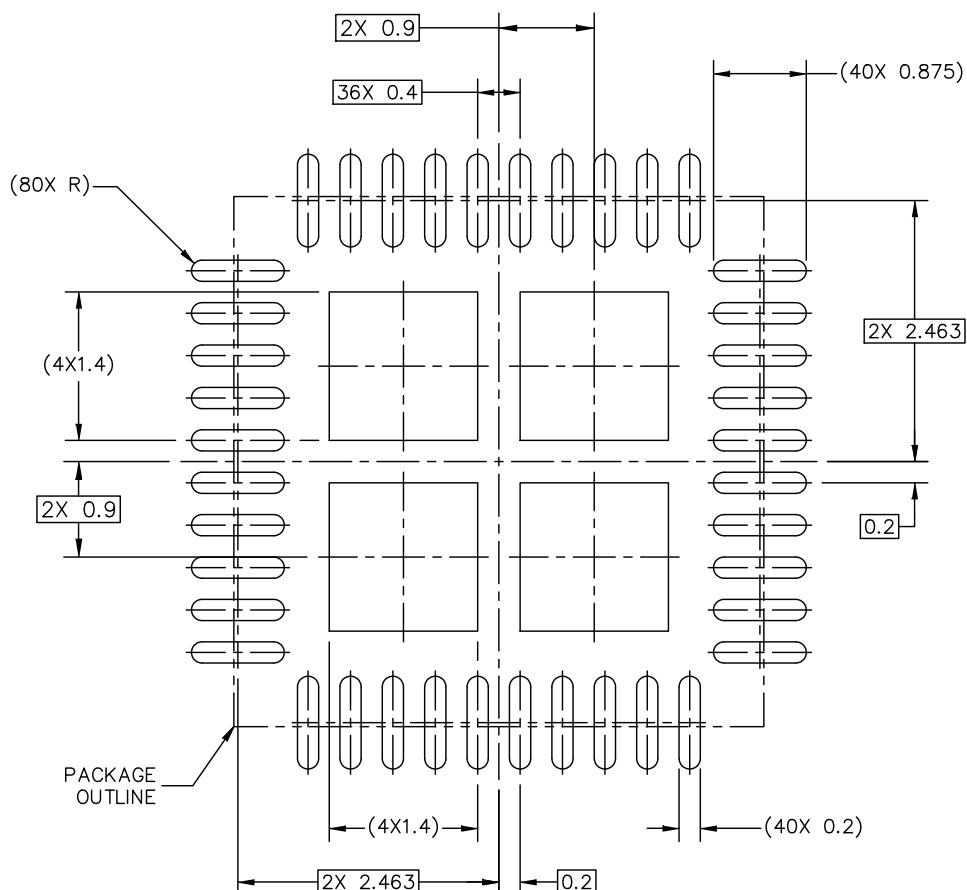

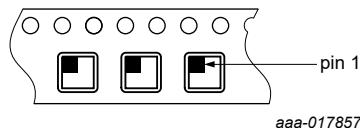

## 6.2 QFN package

Figure 4. QFN40 - Pad configuration (transparent top view of package) - 40 pads

## 6.3 Pin description

[Table 2](#) lists the description of all the pins of the MCX W23. It provides the assignment of these pins to the different supported packages and associated pin type.

The different types are:

- PWR: supply pin

- GND: ground pin

- RF: RF signal pin

- A: analog pin

- AI: analog input pin

- DIO: digital IO pin

When the part is in boundary scan mode, the hardware selects the JTAG functions, TCK functions, TMS functions, TDI functions, and TDO functions on pins PIO0\_14 to PIO0\_17.

Ultra-low power, small footprint Bluetooth Low Energy solution with integrated flash and security for IoT

Table 2. MCX W23 pin description

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol   | Type | Function # | Pin description                                                                                                                                                                                                                          |

|-------|-----------|----------------------------|----------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B6    | 20        | -                          | VBAT_HV  | PWR  |            | For MCX W23xB in high-voltage supply mode (HV_SM), input supply connected to 3 V battery (input to DC-DC converter in buck mode).<br>For MCX W23xB in external regulated supply mode (XR_SM), input supply for internal flash memory.    |

| B5    | 17        | -                          | VBAT_LV  | PWR  |            | For MCX W23xB in high-voltage supply mode (HV_SM), output connected to buffer capacitor (output of DC-DC converter buck mode)<br>For MCX W23xB in external regulated supply mode (XR_SM), input supply for analog and digital subsystem. |

| G3    | 9; 36     | -                          | VDD_IO   | PWR  |            | input supply for digital IO                                                                                                                                                                                                              |

| D5    | 24        | -                          | VDD_RF   | PWR  |            | input supply for RF subsystem                                                                                                                                                                                                            |

| E5    | 25; 27    | -                          | VSS_RF   | GND  |            | RF ground<br><b>Note:</b> In the HVQFN package these pins are shorted to the VSS pins inside the package                                                                                                                                 |

| A5    | 18        | -                          | VSS_DCDC | GND  |            | DC-DC converter ground                                                                                                                                                                                                                   |

| G2    | 21; 40    | -                          | VSS      | GND  |            | digital and IO ground<br><b>Note:</b> HVQFN exposed die attach pad is connected to pins 21 and 40 inside the HVQFN package. They must share ground plane on the PCB.                                                                     |

| A6    | 19        | -                          | LX       | PWR  |            | terminal for external inductor the integrated DC-DC converter uses<br>For the MCX W23 in XR_SM mode, this pin can be left open or connected through a resistor of at least 250 $\Omega$ to ground                                        |

| C5    | 22        | -                          | XI_32M   | AI   |            | 32 MHz crystal oscillator input                                                                                                                                                                                                          |

| C6    | 23        | -                          | XO_32M   | A    |            | 32 MHz crystal oscillator output                                                                                                                                                                                                         |

| B4    | 16        | -                          | XI_32K   | AI   |            | 32.768 kHz crystal oscillator input                                                                                                                                                                                                      |

| A4    | 15        | -                          | XO_32K   | A    |            | 32.768 kHz crystal oscillator output                                                                                                                                                                                                     |

| F6    | 26        | -                          | ANT      | RF   |            | antenna pin                                                                                                                                                                                                                              |

| A2    | 13        | PU                         | RESET_N  | AI   |            | External reset input<br>A LOW on this pin resets the device, causing I/O ports and peripherals to take on their default states, and the boot code to execute.<br>The pin is internally pulled up high on-chip to V <sub>DD_IO</sub> .    |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                | Type | Function # | Pin description                                                                                       |

|-------|-----------|----------------------------|-----------------------|------|------------|-------------------------------------------------------------------------------------------------------|

| E4    | 31        | Z                          | PIO0_0 <sup>[2]</sup> | DIO  | 0          | PIO0_0 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 1          | FC0_CTS_SDA_SSEL0 - Flexcomm 0 USART clear-to-send, I <sup>2</sup> C data I/O, SPI slave select 0     |

|       |           |                            |                       |      | 2          | FC1_RTS_SCL_SSEL1 - Flexcomm 1 USART request-to-send, I <sup>2</sup> C clock, SPI slave select 1      |

|       |           |                            |                       |      | 7          | SEC_PIO0_0 - secure GPIO pin                                                                          |

|       |           |                            |                       |      | 9          | CTIMER0_MAT0 - 32-bit CTIMER 0 match output 0                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP0 - capture input 0 to CTIMER input multiplexers                                            |

|       |           |                            |                       |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 0 SPI SSEL0 function.                       |

| E2    | 1         | Z                          | PIO0_1 <sup>[2]</sup> | DIO  | 0          | PIO0_1 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 1          | FC0_RTS_SCL_SSEL1 - Flexcomm 0 USART request-to-send, I <sup>2</sup> C clock, SPI slave select 1      |

|       |           |                            |                       |      | 2          | FC2_SCK - Flexcomm 2 USART, SPI, or I <sup>2</sup> C clock                                            |

|       |           |                            |                       |      | 6          | PLU_CLKIN - PLU clock input                                                                           |

|       |           |                            |                       |      | 7          | SEC_PIO0_1 - secure GPIO pin                                                                          |

|       |           |                            |                       |      | 9          | CTIMER0_MAT1 - 32-bit CTIMER 0 match output 1                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP1 - capture input 1 to CTIMER input multiplexers                                            |

| D2    | 2         | Z                          | PIO0_2 <sup>[2]</sup> | DIO  | 0          | PIO0_2 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 1          | FC0_RXD_SDA_MOSI - Flexcomm 0 USART receiver, I <sup>2</sup> C data I/O, SPI master-out/slave-in data |

|       |           |                            |                       |      | 3          | SCT_OUT9 - SCTimer/PWM output 9                                                                       |

|       |           |                            |                       |      | 7          | SEC_PIO0_2 - secure GPIO pin                                                                          |

|       |           |                            |                       |      | 9          | CTIMER0_MAT2 - 32-bit CTIMER 0 match output 2                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP2 - capture input 2 to CTIMER input multiplexers                                            |

|       |           |                            |                       |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 0 SPI MOSI function.                        |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                | Type | Function # | Pin description                                                                                       |

|-------|-----------|----------------------------|-----------------------|------|------------|-------------------------------------------------------------------------------------------------------|

| F1    | 3         | Z                          | PIO0_3 <sup>[2]</sup> | DIO  | 0          | PIO0_3 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 1          | FC0_TXD_SCL_MISO - Flexcomm 0 USART transmitter, I <sup>2</sup> C clock, SPI master-in/slave-out data |

|       |           |                            |                       |      | 3          | SCT_OUT8 - SCTimer/PWM output 8                                                                       |

|       |           |                            |                       |      | 4          | FREQME_GPIO_3 - frequency measure pin 3 clock input                                                   |

|       |           |                            |                       |      | 7          | SEC_PIO0_3 - secure GPIO pin                                                                          |

|       |           |                            |                       |      | 9          | CTIMER0_MAT3 - 32-bit CTIMER 0 match output 3                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP3 - capture input 3 to CTIMER input multiplexers                                            |

|       |           |                            |                       |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 0 SPI MISO function.                        |

| C2    | 4         | Z                          | PIO0_4 <sup>[2]</sup> | DIO  | 0          | PIO0_4 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 1          | FC0_SCK - Flexcomm 0 USART, SPI, or I <sup>2</sup> C clock                                            |

|       |           |                            |                       |      | 3          | SCT_OUT7 - SCTimer/PWM output 7                                                                       |

|       |           |                            |                       |      | 7          | SEC_PIO0_4 - secure GPIO pin                                                                          |

|       |           |                            |                       |      | 9          | CTIMER1_MAT0 - 32-bit CTIMER 1 match output 0                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP4 - capture input 4 to CTIMER input multiplexers                                            |

|       |           |                            |                       |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 0 SPI SCL function                          |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                | Type | Function # | Pin description                                                                                       |

|-------|-----------|----------------------------|-----------------------|------|------------|-------------------------------------------------------------------------------------------------------|

| F2    | 37        | Z                          | PIO0_5 <sup>[2]</sup> | DIO  | 0          | PIO0_5 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 2          | FC2_CTS_SDA_SSEL0 - Flexcomm 2 USART clear-to-send, I <sup>2</sup> C data I/O, SPI slave select 0     |

|       |           |                            |                       |      | 3          | SCT_OUT6 - SCTimer/PWM output 6                                                                       |

|       |           |                            |                       |      | 5          | UTICK_CAP0 - Microtick timer capture input 0                                                          |

|       |           |                            |                       |      | 6          | PLU_IN0 - PLU input 0                                                                                 |

|       |           |                            |                       |      | 7          | SEC_PIO0_5 - secure GPIO pin                                                                          |

|       |           |                            |                       |      | 8          | SPIFI_CSN - Quad-SPI chip select                                                                      |

|       |           |                            |                       |      | 9          | CTIMER1_MAT1 - 32-bit CTIMER 1 match output 1                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP5 - capture input 5 to CTIMER input multiplexers                                            |

|       |           |                            |                       |      |            |                                                                                                       |

| B2    | 10        | Z                          | PIO0_6 <sup>[2]</sup> | DIO  | 0          | PIO0_6 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 2          | FC2_RXD_SDA_MOSI - Flexcomm 2 USART receiver, I <sup>2</sup> C data I/O, SPI master-out/slave-in data |

|       |           |                            |                       |      | 3          | SCT_OUT5 - SCTimer/PWM output 5                                                                       |

|       |           |                            |                       |      | 5          | UTICK_CAP1 - microtick timer capture input 1                                                          |

|       |           |                            |                       |      | 6          | PLU_IN1 - PLU input 1                                                                                 |

|       |           |                            |                       |      | 7          | SEC_PIO0_6 - Secure GPIO pin                                                                          |

|       |           |                            |                       |      | 8          | SPIFI_IO0 - Quad-SPI data I/O 0                                                                       |

|       |           |                            |                       |      | 9          | CTIMER1_MAT2 - 32-bit CTIMER 1 match output 2                                                         |

|       |           |                            |                       |      | 10         | CTIMER_INP6 - Capture input 6 to CTIMER input multiplexers                                            |

|       |           |                            |                       |      |            |                                                                                                       |

| E3    | 38        | Z                          | PIO0_7 <sup>[2]</sup> | DIO  | 0          | PIO0_7 GPIO - general-purpose digital input/output pin                                                |

|       |           |                            |                       |      | 2          | FC2_TXD_SCL_MISO - Flexcomm 2 USART transmitter, I <sup>2</sup> C clock, SPI master-in/slave-out data |

|       |           |                            |                       |      | 3          | SCT_OUT4 - SCTimer/PWM output 4                                                                       |

|       |           |                            |                       |      | 5          | UTICK_CAP2 - microtick timer capture input 2                                                          |

|       |           |                            |                       |      | 6          | PLU_IN2 - PLU input 2                                                                                 |

|       |           |                            |                       |      | 7          | SEC_PIO0_7 - secure GPIO pin                                                                          |

|       |           |                            |                       |      |            |                                                                                                       |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                                  |

|-------|-----------|----------------------------|------------------------|------|------------|--------------------------------------------------------------------------------------------------|

|       |           |                            |                        |      | 8          | SPIFI_IO1 - quad-SPI data I/O 0                                                                  |

|       |           |                            |                        |      | 9          | CTIMER1_MAT3 - 32-bit CTIMER 1 match output 3                                                    |

|       |           |                            |                        |      | 10         | CTIMER_INP7 - capture input 7 to CTIMER input multiplexers                                       |

| G1    | 39        | Z                          | PIO0_8 <sup>[2]</sup>  | DIO  | 0          | PIO0_8 GPIO - general-purpose digital input/output pin                                           |

|       |           |                            |                        |      | 2          | FC2_RTS_SCL_SSEL1 - Flexcomm 2 USART request-to-send, I <sup>2</sup> C clock, SPI slave select 1 |

|       |           |                            |                        |      | 3          | SCT_GPI7 - pin input 7 to SCTimer/PWM                                                            |

|       |           |                            |                        |      | 5          | UTICK_CAP3 - microtick timer capture input 3                                                     |

|       |           |                            |                        |      | 6          | PLU_IN3 - PLU input 3                                                                            |

|       |           |                            |                        |      | 7          | SEC_PIO0_8 - secure GPIO pin                                                                     |

|       |           |                            |                        |      | 8          | SPIFI_IO2 - quad-SPI data I/O 2                                                                  |

|       |           |                            |                        |      | 9          | CTIMER2_MAT0 - 32-bit CTIMER 2-match output 0                                                    |

|       |           |                            |                        |      | 10         | CTIMER_INP8 - capture input 8 to CTIMER input multiplexers                                       |

|       |           |                            |                        |      |            |                                                                                                  |

| B3    | 12        | Z                          | PIO0_9 <sup>[2]</sup>  | DIO  | 0          | PIO0_9 GPIO - general-purpose digital input/output pin                                           |

|       |           |                            |                        |      | 3          | SCT_GPI6 - pin input 6 to SCTimer/PWM                                                            |

|       |           |                            |                        |      | 4          | CLKOUT - output of the CLKOUT function                                                           |

|       |           |                            |                        |      | 6          | PLU_IN4 - PLU input 4                                                                            |

|       |           |                            |                        |      | 7          | SEC_PIO0_9 - secure GPIO pin                                                                     |

|       |           |                            |                        |      | 8          | SPIFI_IO3 - quad-SPI data I/O 3                                                                  |

|       |           |                            |                        |      | 9          | CTIMER2_MAT1 - 32-bit CTIMER 2-match output 1                                                    |

|       |           |                            |                        |      | 10         | CTIMER_INP9 - capture input 9 to CTIMER input multiplexers                                       |

|       |           |                            |                        |      |            |                                                                                                  |

|       |           |                            |                        |      |            |                                                                                                  |

| A1    | 11        | Z                          | PIO0_10 <sup>[2]</sup> | DIO  | 0          | PIO0_10 GPIO - general-purpose digital input/output pin                                          |

|       |           |                            |                        |      | 2          | FC2_SCK - Flexcomm 2 USART, SPI, or I <sup>2</sup> C clock                                       |

|       |           |                            |                        |      | 3          | SCT_GPI5 - pin input 5 to SCTimer/PWM                                                            |

|       |           |                            |                        |      | 6          | PLU_IN5 - PLU input 5                                                                            |

|       |           |                            |                        |      | 7          | SEC_PIO0_10 - secure GPIO pin                                                                    |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                                   |

|-------|-----------|----------------------------|------------------------|------|------------|---------------------------------------------------------------------------------------------------|

|       |           |                            |                        |      | 8          | SPIFI_CLK - quad-SPI clock                                                                        |

|       |           |                            |                        |      | 9          | CTIMER2_MAT2 - 32-bit CTIMER 2-match output 2                                                     |

|       |           |                            |                        |      | 10         | CTIMER_INP10 - capture input 10 to CTIMER input multiplexers                                      |

| G4    | 34        | PD                         | PIO0_11 <sup>[2]</sup> | DIO  | 0          | PIO0_11 GPIO - general-purpose digital input/output pin                                           |

|       |           |                            |                        |      | 1          | SWCLK - serial wire debug (SWD) clock. The default function after booting                         |

|       |           |                            |                        |      | 2          | FC1_CTS_SDA_SSEL0 - Flexcomm 1 USART clear-to-send, I <sup>2</sup> C data I/O, SPI slave select 0 |

|       |           |                            |                        |      | 3          | SCT_GPI4 - pin input 4 to SCTimer/PWM                                                             |

|       |           |                            |                        |      | 4          | FREQME_GPIO_11 - frequency measure pin 11 clock input                                             |

|       |           |                            |                        |      | 5          | UTICK_CAP0 - microtick timer capture input 0                                                      |

|       |           |                            |                        |      | 6          | PLU_CLKIN - PLU clock input                                                                       |

|       |           |                            |                        |      | 7          | CTIMER2_MAT3 - 32-bit CTIMER 2-match output 3                                                     |

|       |           |                            |                        |      | 9          | CTIMER_INP11 - capture input 11 to CTIMER input multiplexers                                      |

|       |           |                            |                        |      | 10         | SEC_PIO0_11 - secure GPIO pin                                                                     |

|       |           |                            |                        |      |            | <b>Note:</b> To enter the boundary scan mode, this pin must be pulled high at start-up.           |

| G5    | 33        | PU                         | PIO0_12 <sup>[2]</sup> | DIO  | 0          | PIO0_12 GPIO - general-purpose digital input/output pin                                           |

|       |           |                            |                        |      | 1          | SWDIO - serial wire debug (SWD) I/O. The default function after booting                           |

|       |           |                            |                        |      | 2          | FC1_RTS_SCL_SSEL1 - Flexcomm 1 USART request-to-send, I <sup>2</sup> C clock, SPI slave select 1  |

|       |           |                            |                        |      | 3          | SCT_OUT3 - SCTimer/PWM output 3                                                                   |

|       |           |                            |                        |      | 4          | FREQME_GPIO_12 - frequency measure pin 12 clock input                                             |

|       |           |                            |                        |      | 5          | UTICK_CAP1 - microtick timer capture input 1                                                      |

|       |           |                            |                        |      | 6          | PLU_OUT0 - PLU output 0                                                                           |

|       |           |                            |                        |      | 7          | SEC_PIO0_12 - secure GPIO pin                                                                     |

|       |           |                            |                        |      | 9          | CTIMER3_MAT0 - 32-bit CTIMER 3-match output 0                                                     |

Ultra-low power, small footprint Bluetooth Low Energy solution with integrated flash and security for IoT

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                                       |

|-------|-----------|----------------------------|------------------------|------|------------|-------------------------------------------------------------------------------------------------------|

|       |           |                            |                        |      | 10         | CTIMER_INP12 - capture input 12 to CTIMER input multiplexers                                          |

| D1    | 6         | Z                          | PIO0_13 <sup>[3]</sup> | DIO  | 0          | PIO0_13 GPIO - general-purpose digital input/output pin                                               |

|       |           |                            |                        |      | 1          | FC1_RXD_SDA_MOSI - Flexcomm 1 USART receiver, I <sup>2</sup> C data I/O, SPI master-out/slave-in data |

|       |           |                            |                        |      | 2          | FC2_CTS_SDA_SSEL0 - Flexcomm 2 USART clear-to-send, I <sup>2</sup> C data I/O, SPI slave select 0     |

|       |           |                            |                        |      | 3          | SCT_OUT2 - SCTimer/PWM output 2                                                                       |

|       |           |                            |                        |      | 5          | UTICK_CAP2 - microtick timer capture input 2                                                          |

|       |           |                            |                        |      | 6          | PLU_OUT1 - PLU output 1                                                                               |

|       |           |                            |                        |      | 7          | SEC_PIO0_13 - secure GPIO pin                                                                         |

|       |           |                            |                        |      | 9          | CTIMER3_MAT1 - 32-bit CTIMER 3-match output 1                                                         |

|       |           |                            |                        |      | 10         | CTIMER_INP13 - capture input 13 to CTIMER input multiplexers                                          |

|       |           |                            |                        |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 1 SDA function.                             |

| E1    | 5         | Z                          | PIO0_14 <sup>[3]</sup> | DIO  | 0          | PIO0_14 GPIO - general-purpose digital input/output pin                                               |

|       |           |                            |                        |      | 1          | FC1_TXD_SCL_MISO - Flexcomm 1 USART transmitter, I <sup>2</sup> C clock, SPI master-in/slave-out data |

|       |           |                            |                        |      | 2          | FC2_RTS_SCL_SSEL1 - Flexcomm 2 USART request-to-send, I <sup>2</sup> C clock, SPI slave select 1      |

|       |           |                            |                        |      | 3          | SCT_OUT1 - SCTimer/PWM output 1                                                                       |

|       |           |                            |                        |      | 4          | FREQME_GPIO_14 - frequency measure pin 14 clock input                                                 |

|       |           |                            |                        |      | 5          | UTICK_CAP3 - microtick timer capture input 3                                                          |

|       |           |                            |                        |      | 6          | PLU_OUT2 - PLU output 2                                                                               |

|       |           |                            |                        |      | 7          | SEC_PIO0_14 - secure GPIO pin                                                                         |

|       |           |                            |                        |      | 9          | CTIMER3_MAT2 - 32-bit CTIMER 3-match output 2                                                         |

|       |           |                            |                        |      | 10         | CTIMER_INP14 - capture input 14 to CTIMER input multiplexers                                          |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                                                                                      |

|-------|-----------|----------------------------|------------------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |           |                            |                        |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 1 SCL CLK function.<br><b>Note:</b> In boundary scan mode, this pin is test-data-in (TDI). |

| F3    | 35        | Z                          | PIO0_15 <sup>[2]</sup> | DIO  | 0          | PIO0_15 GPIO - general-purpose digital input/output pin                                                                                              |

|       |           |                            |                        |      | 1          | SWO - serial wire debug (SWD) trace output                                                                                                           |

|       |           |                            |                        |      | 2          | FC1_CTS_SDA_SSEL0 - Flexcomm 1 USART clear-to-send, I <sup>2</sup> C data I/O, SPI slave select 0                                                    |

|       |           |                            |                        |      | 3          | SCT_OUT0 - SCTimer/PWM output 0                                                                                                                      |

|       |           |                            |                        |      | 6          | PLU_OUT3 - PLU output 3                                                                                                                              |

|       |           |                            |                        |      | 7          | SEC_PIO0_15 - secure GPIO pin                                                                                                                        |

|       |           |                            |                        |      | 9          | CTIMER3_MAT3 - 32-bit CTIMER 3-match output 3                                                                                                        |

|       |           |                            |                        |      | 10         | CTIMER_INP15 - capture input 15 to CTIMER input multiplexers                                                                                         |

|       |           |                            |                        |      |            | <b>Note:</b> In boundary scan mode, this pin is test mode select (TMS).                                                                              |

|       |           |                            |                        |      |            |                                                                                                                                                      |

| F4    | 32        | Z                          | PIO0_16 <sup>[2]</sup> | DIO  | 0          | PIO0_16 GPIO - general-purpose digital input/output pin                                                                                              |

|       |           |                            |                        |      | 2          | FC1_SCK - Flexcomm 1 USART, SPI, or I <sup>2</sup> C clock                                                                                           |

|       |           |                            |                        |      | 3          | SCT_GPI3 - SCTimer/PWM input 3                                                                                                                       |

|       |           |                            |                        |      | 6          | PLU_OUT4 - PLU output 4                                                                                                                              |

|       |           |                            |                        |      | 7          | SEC_PIO0_16 - secure GPIO pin                                                                                                                        |

|       |           |                            |                        |      | 9          | CTIMER4_MAT0 - 32-bit CTIMER 4-match output 0                                                                                                        |

|       |           |                            |                        |      | 10         | CTIMER_INP16 - capture input 16 to CTIMER input multiplexers                                                                                         |

|       |           |                            |                        |      |            | <b>Note:</b> In boundary scan mode, this pin is test-clock-in (TCK)                                                                                  |

|       |           |                            |                        |      |            |                                                                                                                                                      |

|       |           |                            |                        |      |            |                                                                                                                                                      |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                                       |

|-------|-----------|----------------------------|------------------------|------|------------|-------------------------------------------------------------------------------------------------------|

| D4    | 28        | Z                          | PIO0_17 <sup>[2]</sup> | DIO  | 0          | PIO0_17 GPIO - general-purpose digital input/output pin                                               |

|       |           |                            |                        |      | 1          | SWO - serial wire debug (SWD) trace output                                                            |

|       |           |                            |                        |      | 2          | FC0_CTS_SDA_SSEL0 - Flexcomm 0 USART clear-to-send, I <sup>2</sup> C data I/O, SPI slave select 0     |

|       |           |                            |                        |      | 3          | SCT_GPI2 - SCTimer/PWM input 2                                                                        |

|       |           |                            |                        |      | 6          | PLU_OUT5 - PLU output 5                                                                               |

|       |           |                            |                        |      | 7          | SEC_PIO0_17 - secure GPIO pin                                                                         |

|       |           |                            |                        |      | 9          | CTIMER4_MAT1 - 32-bit CTIMER 4-match output 1                                                         |

|       |           |                            |                        |      | 10         | CTIMER_INP17 - capture input 17 to CTIMER input multiplexers                                          |

|       |           |                            |                        |      |            | <b>Note:</b> In boundary scan mode, this pin is test-data-out (TDO).                                  |

|       |           |                            |                        |      |            |                                                                                                       |

| B1    | 8         | Z                          | PIO0_18 <sup>[4]</sup> | DIO  | 0          | PIO0_18 GPIO - general-purpose digital input/output pin                                               |

|       |           |                            |                        |      | 1          | FC2_RXD_SDA_MOSI - Flexcomm 2 USART receiver, I <sup>2</sup> C data I/O, SPI master-out/slave-in data |

|       |           |                            |                        |      | 3          | SCT_GPI1 - SCTimer/PWM input 1                                                                        |

|       |           |                            |                        |      | 4          | CLKOUT - output of the CLKOUT function                                                                |

|       |           |                            |                        |      | 6          | PLU_OUT6 - PLU output 6                                                                               |

|       |           |                            |                        |      | 7          | SEC_PIO0_18 - secure GPIO pin                                                                         |

|       |           |                            |                        |      | 9          | CTIMER4_MAT2 - 32-bit CTIMER 4-match output 2                                                         |

|       |           |                            |                        |      | 10         | CTIMER_INP18 - capture input 18 to CTIMER input multiplexers                                          |

|       |           |                            |                        |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 2 RXD function.                             |

|       |           |                            |                        |      |            |                                                                                                       |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                                                                                                                                                             |

|-------|-----------|----------------------------|------------------------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1    | 7         | Z                          | PIO0_19 <sup>[4]</sup> | DIO  | 0          | PIO0_19 GPIO - general-purpose digital input/output pin                                                                                                                                                                     |

|       |           |                            |                        |      | 1          | FC2_TXD_SCL_MISO - Flexcomm 2 USART transmitter, I <sup>2</sup> C clock, SPI master-in/slave-out data                                                                                                                       |

|       |           |                            |                        |      | 3          | SCT_GPIO - SCTimer/PWM input 0                                                                                                                                                                                              |

|       |           |                            |                        |      | 6          | PLU_OUT7 - PLU output 7                                                                                                                                                                                                     |

|       |           |                            |                        |      | 7          | SEC_PIO0_19 - secure GPIO pin                                                                                                                                                                                               |

|       |           |                            |                        |      | 9          | CTIMER4_MAT3 - 32-bit CTIMER 4-match output 3                                                                                                                                                                               |

|       |           |                            |                        |      | 10         | CTIMER_INP19 - capture input 19 to CTIMER input multiplexers                                                                                                                                                                |

|       |           |                            |                        |      |            | <b>Note:</b> In ISP mode, this pin is set to the Flexcomm 2 TXD function.                                                                                                                                                   |

| G6    | 30        | PU                         | PIO0_20 <sup>[2]</sup> | DIO  | 0          | PIO0_20 GPIO - general-purpose digital input/output pin                                                                                                                                                                     |

|       |           |                            |                        |      | 7          | SEC_PIO0_20 - secure GPIO pin                                                                                                                                                                                               |

|       |           |                            |                        |      | 10         | CTIMER_INP20 - capture input 20 to CTIMER input multiplexers                                                                                                                                                                |

|       |           |                            |                        |      |            | <b>Note:</b> The state of this pin at reset determines the boot mode for the part. If it is pulled down, the ISP mode is invoked.<br><b>Note:</b> To enter the boundary scan mode, this pin must be pulled low at start-up. |

| A3    | 14        | Z                          | PIO0_21 <sup>[2]</sup> | DIO  | 0          | PIO0_21 GPIO - general-purpose digital input/output pin                                                                                                                                                                     |

|       |           |                            |                        |      | 1          | WAKEUP_INTERRUPT<br>The WAKEUP pin can be configured with a PU or PD level. This pin can trigger a wake-up from low-power modes.                                                                                            |

|       |           |                            |                        |      | 7          | SEC_PIO0_21 - secure GPIO pin                                                                                                                                                                                               |

|       |           |                            |                        |      | 10         | CTIMER_INP21 - capture input 21 to CTIMER input multiplexers                                                                                                                                                                |

Table 2. MCX W23 pin description...continued

| WLCSP | QFN40 pin | Reset state <sup>[1]</sup> | Symbol                 | Type | Function # | Pin description                                                                         |

|-------|-----------|----------------------------|------------------------|------|------------|-----------------------------------------------------------------------------------------|

| F5    | 29        | PD                         | PIO0_22 <sup>[2]</sup> | DIO  | 0          | PIO0_22 GPIO - general-purpose digital input/output pin                                 |

|       |           |                            |                        |      | 7          | SEC_PIO0_22 - secure GPIO pin                                                           |

|       |           |                            |                        |      | 10         | CTIMER_INP22 - capture input 22 to CTIMER input multiplexers                            |

|       |           |                            |                        |      |            | <b>Note:</b> To enter the boundary scan mode, this pin must be pulled high at start-up. |

[1] PU = input mode, pull-up enabled (pull-up resistor pulls up pin toward VDD). PD = input mode, pull-down enabled (pull-down resistor pulls down pin toward VSS). Z = high impedance; pull-up, pull-down, and input disabled. AI = analog input. I = input. O = output. I/O = input/output. Reset state reflects the pin state at reset without boot code operation.

[2] Pad with programmable glitch filter; provides digital I/O functions with TTL levels and hysteresis; normal drive strength. Pulse width of spikes or glitches suppressed by an input filter is from 3 ns to 16 ns (simulated value).

[3] True open-drain pin. I<sup>2</sup>C-bus pins compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode, I<sup>2</sup>C fast mode, and I<sup>2</sup>C fast mode plus. To provide output functionality, the pin requires an external pull-up. When power is switched off, this pin is floating and does not disturb the I<sup>2</sup>C lines. Open-drain configuration applies to all functions on this pin.

[4] Pin providing standard digital I/O functions with configurable modes, configurable hysteresis, and analog input. When configured as an analog input, the digital section of the pin is disabled.

## 7 Functional description

### 7.1 Controller subsystem

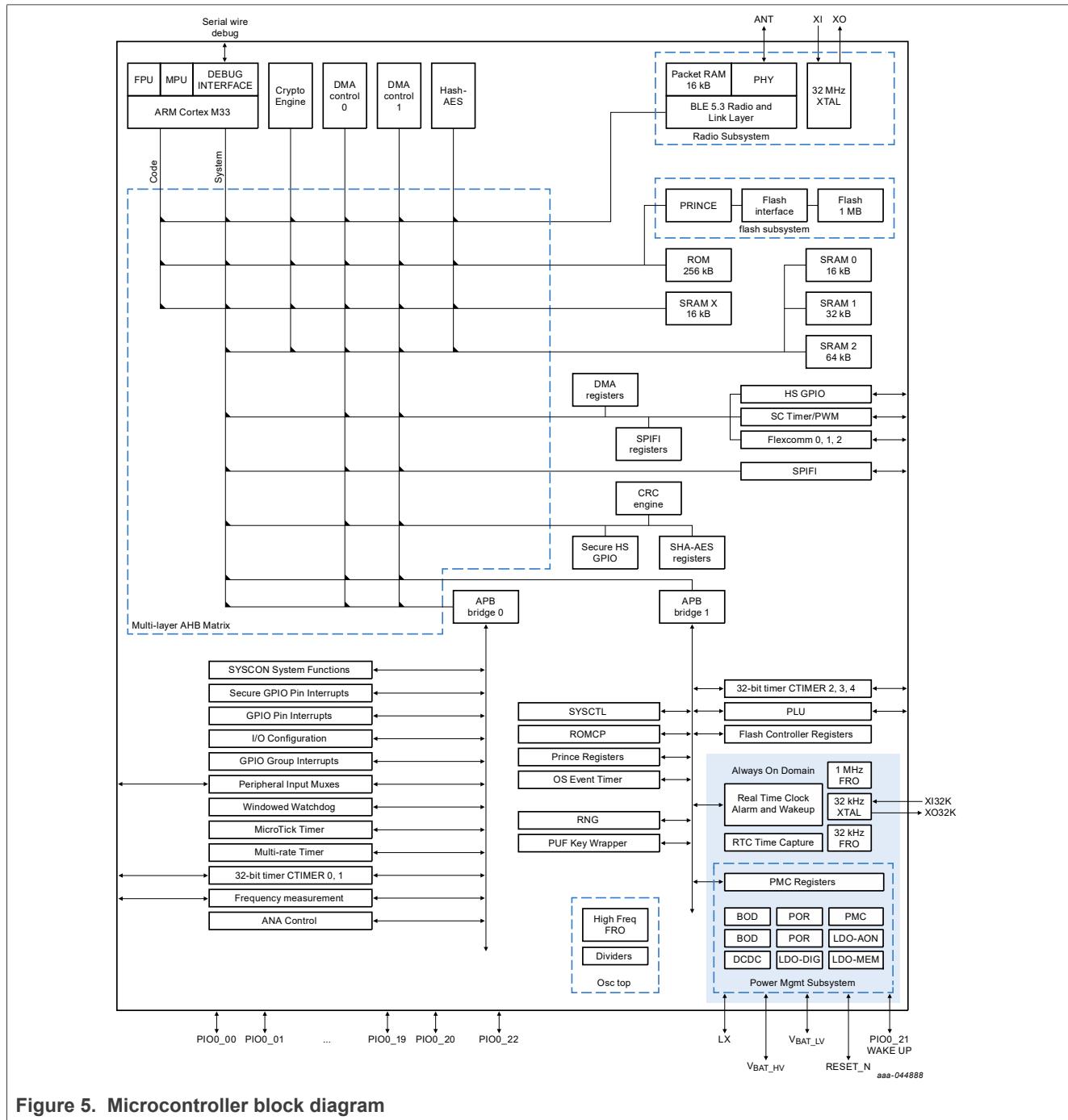

Figure 5 shows the block diagram of the microcontroller subsystem.

Figure 5. Microcontroller block diagram

Some main components are described in the subsequent subsections.

### 7.1.1 Architectural overview

The Arm Cortex M33 includes two AHB-Lite buses, one system bus, and one code bus. The code-AHB (C-AHB) interface is used for any instruction fetch and data access to the code region of the ARMv8-M memory map ([0x00000000 to 0x1FFFFFFF]). The system-AHB (S-AHB) interface is used for instruction fetch and data access to all other regions of the ARMv8-M memory map ([0x20000000 to 0xFFFFFFFF]).

To connect the Arm Cortex-M33 buses and other bus masters to peripherals in a flexible manner, the MCX W23 uses a multilayer AHB matrix. It optimizes performance by allowing peripherals that are on different slave ports of the matrix to be accessed simultaneously by different bus masters. [Figure 5](#) shows the available matrix connections.

### 7.1.2 Arm Cortex-M33 processor

The Arm Cortex-M33 is a general-purpose, 32-bit microprocessor, which offers high performance and very low power consumption. The Arm Cortex M33 offers many features, including:

- A Thumb-2 instruction set

- Low interrupt latency

- Hardware multiply and divide

- Interruptable/continuable multiple load and store instructions

- Automatic state save and restore for interrupts

- Tightly integrated interrupt controller with wake-up interrupt controller

- Multiple core buses capable of simultaneous accesses

A 3-stage pipeline is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is executed, its successor is decoded, and a third instruction is fetched from memory.

The Arm Cortex-M33 provides a security foundation, offering isolation to protect valuable IP and data with TrustZone technology. It simplifies the design and software development of digital signal control systems with the integrated digital signal processing (DSP) instructions.

The Arm Cortex-M33 core includes a SysTick timer that is intended to generate a dedicated SYSTICK exception.

On the MCX W23, the Cortex-M33 is augmented with a hardware public key coprocessor (PKC) providing accelerated support for cryptography.

### 7.1.3 Arm Cortex-M33 integrated floating-point unit

The floating-point unit (FPU) fully supports single-precision add, subtract, multiply, divide, multiply and accumulate, and square root operations. It also provides conversions between fixed-point and floating-point data formats and floating-point constant instructions.

The FPU provides floating-point computation functionality that is compliant with the ANSI/IEEE Std 754-2008, IEEE Standard for Binary Floating-Point Arithmetic, referred to as the IEEE 754 standard.

## 7.1.4 Memories

### 7.1.4.1 On-chip flash

Support for up to 1 MB (main flash array) + 32 KB (information flash region) of on-chip flash memory. Each 16-byte phrase in flash is protected by a 9-bit error correction code, which allows the correction of single-bit faults and detects double bit faults.

The protected flash region (PFR) is 40 KB. It is mapped on the information flash region (32 KB) and the last sector (8 KB) of the main flash array.

The protected flash region is available to configure secure boot, debug authentication, read UUID, store PUF in a key store area, and user-defined fields available for specific data storage.

### 7.1.4.2 On-chip static RAM

The on-chip static RAM supports up to 128 KB SRAM (divided into 4 physical blocks) with a separate bus master access for higher throughput and individual power control for low-power operation. The 16 KB SRAM is on the Arm C-bus (SRAMX). The remaining 112 KB is on the Arm S-bus split into 3 physical blocks (1 block of 16 KB - SRAM0, 1 block of 32 KB -SRAM1, and 1 block of 64 KB - SRAM2).

SRAM memory is also dedicated for the Bluetooth Low Energy radio. The Bluetooth Low Energy radio has 16 KB data SRAM and 512 bytes sequencer SRAM.

### 7.1.4.3 On-chip ROM

The on-chip ROM contains the bootloader and the following features:

- Booting of images from the on-chip flash

- Supports CRC32 image integrity checking

- Supports flash programming through in-system programming (ISP) commands over the following interfaces: UART interface (Flexcomm 2) with autobaud, SPI slave interfaces (Flexcomm 0) using mode 3 (CPOL = 1 and CPHA = 1), and I<sup>2</sup>C slave interface (Flexcomm 1)

- ROM API functions: Flash programming API, the power control API, and the secure firmware update API using NXP Secure Boot file format, version 2.1 (SB2 files)

- Supports booting of images from PRINCE encrypted flash region

- Supports NXP Debug Authentication Protocol version 1.0 (RSA-2048) and 1.1 (RSA-4096)

- Supports setting a sealed part to fault analysis mode via debug authentication

- Supports recovery boot from external flash using Flexcomm 2

The on-chip ROM supports a secure boot based on the RSA public key signature.

- Uses RSASSA-PKCS1-v1\_5 signature of SHA256 digest as cryptographic signature verification.

- Supports RSA-2048 bit public keys (2048-bit modulus, 32-bit exponent).

- Supports RSA-4096 bit public keys (4096-bit modulus, 32-bit exponent).

- Uses x509 certificate format to validate image public keys.

- Supports up to four revocable root of trust (RoT) or certificate authority keys. Root of trust establishment by storing the SHA-256 hash digest of the SHA-256 hashes of four RoT public keys in the protected flash region (PFR).

- Supports an antirollback feature using image key revocation and supports up to 16 image key certificate revocations using a serial number field in an x509 certificate.

### 7.1.5 DMA controller

The DMA controller allows peripheral-to-memory, memory-to-peripheral, and memory-to-memory transactions. Each DMA stream provides unidirectional DMA transfers for a single source and destination.

Two DMA controllers are included, for a secure DMA or a non-secure DMA.

#### 7.1.5.1 Features

- The DMA controller has two instances. DMA0 is intended for non-secure use. DMA1 is intended for secure use.

- DMA0: 8 channels. They come from the Flexcomm interfaces (0, 1, and 2), the SPIFI interface, AES, and the SHA interfaces. 21 trigger sources are available.

- DMA1: 8 channels. They come from the Flexcomm Interfaces (0, 1, and 2), the SPIFI interface, AES, and the SHA interfaces. 15 trigger sources are available.

- On-chip or off-chip events can trigger DMA operations.

- Priority is user-selectable for each channel (up to eight priority levels).

- Continuous priority arbitration.

- Address cache with four entries.

- Efficient use of data bus.

- Supports single transfers up to 1,024 words.

- Address increment options allow packing and/or unpacking data.

### 7.1.6 Flexcomm serial communication interface

A Flexcomm interface provides a choice of serial communication peripheral functions, one of which the user must choose before the function can be configured and used.

Supported functions:

- USART with asynchronous operation or synchronous master or slave operation

- SPI master or slave with up to 2 slave selects

- I<sup>2</sup>C, including separate master, slave, and monitor functions

The MCX W23 contains three independent Flexcomm interfaces.

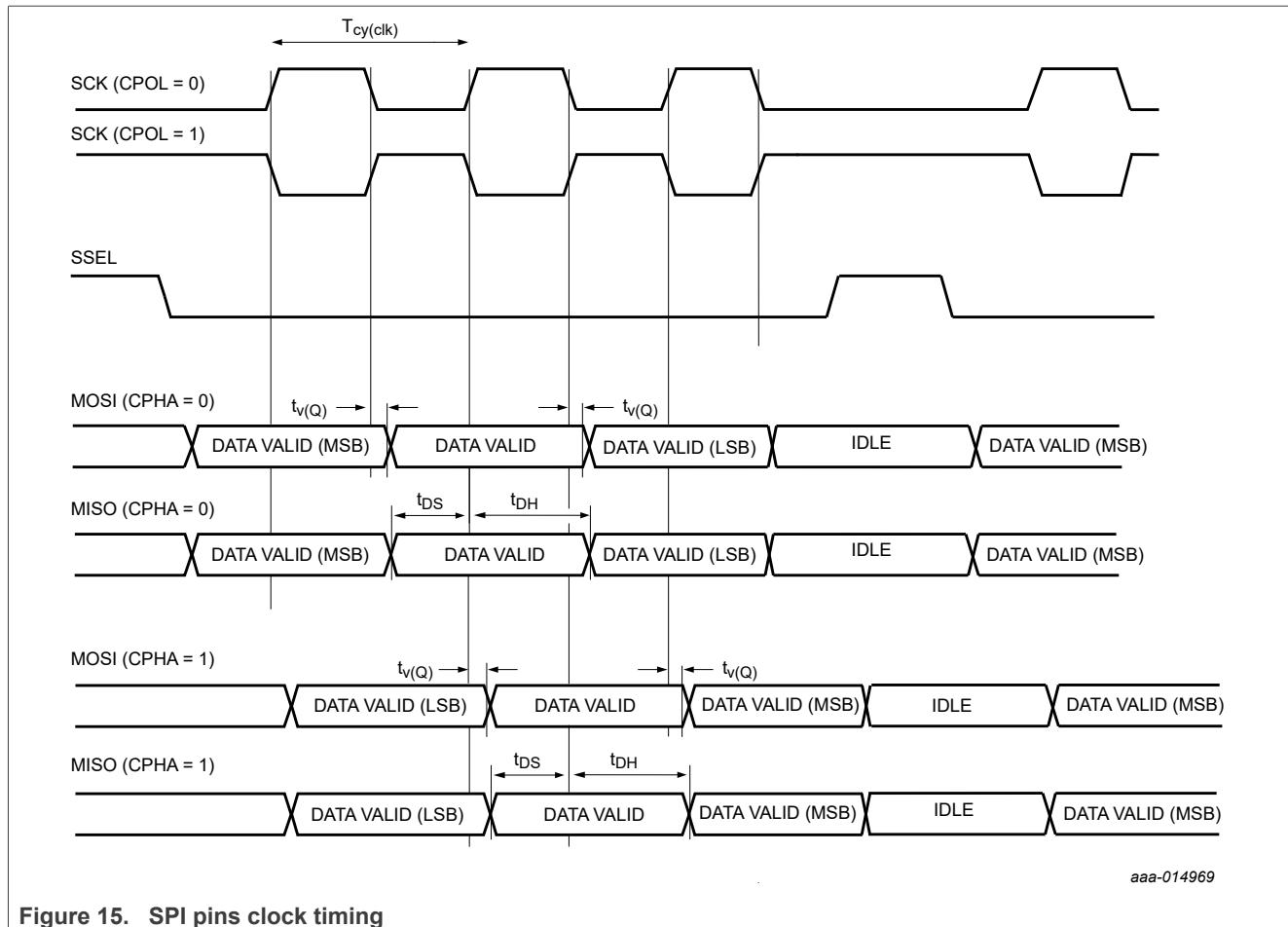

#### 7.1.6.1 Flexcomm SPI

##### Features

- The maximum supported bit rate for SPI master and slave (transmit/receive) mode is 18 Mbit/s over the full VDD<sub>IO</sub> range (VBAT<sub>LV</sub> supply range). If VDD<sub>IO</sub> exceeds 1.7 V (VBAT<sub>HV</sub> supply range), the maximum supported bit rate for SPI slave mode can be increased up to 24 Mbit/s.

- Master and slave operation.

- Data frames of 4 bits to 16 bits supported directly. Software supports larger frames.

- The SPI function supports separate transmit and receive FIFOs with eight entries each.

- Supports DMA transfers: SPI transmit and receive functions can be operated with the system DMA controller.

- Data can be transmitted to a slave without the necessity to read incoming data, which can be useful while setting up an SPI memory.

- Up to two slave-select input/outputs with selectable polarity and flexible usage.

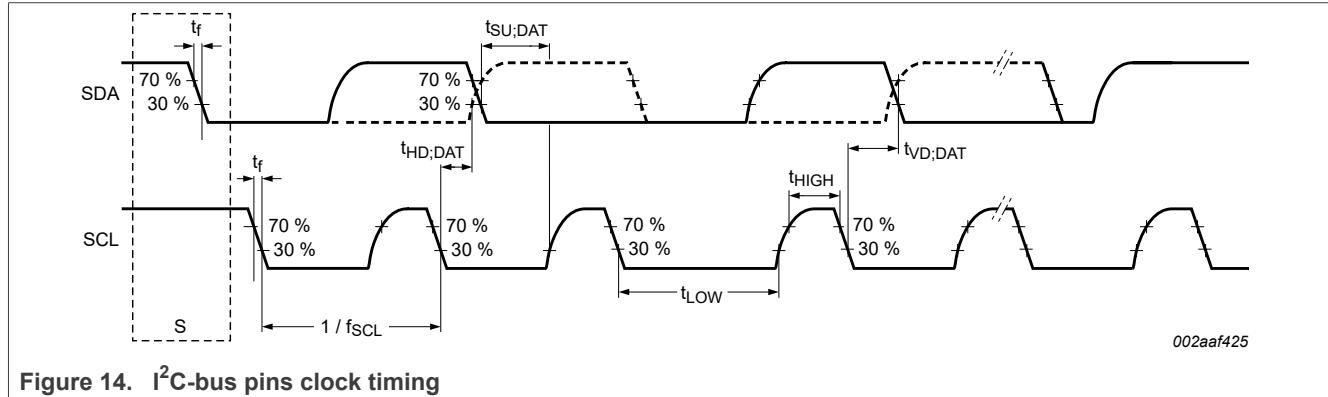

### 7.1.6.2 Flexcomm I<sup>2</sup>C

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a serial clock line (SCL) and a serial data line (SDA). Each device is recognized by a unique address and can operate as a receiver-only device (for example, an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in master mode or slave mode, depending on if the chip must initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multimaster bus. More than one bus master connected to it can control it.

#### Features

- Supports standard (100 kbps), fast mode (400 kbps), and fast mode Plus (specific I<sup>2</sup>C pins) with data rates of up to 1 Mbit/s.

- Supports high-speed mode with data rates up to 3.4 Mbit/s (specific I<sup>2</sup>C pins when VDD<sub>IO</sub> at 1.8 V or higher).

- Independent master, slave, and monitor functions.

- Supports multimaster and multimaster with slave functions.

- Multiple I<sup>2</sup>C slave addresses supported in hardware.

- To respond to multiple I<sup>2</sup>C-bus addresses, one slave address can be selectively qualified with a bit mask or an address range.

- 10-bit addressing supported with software assist.

- Supports SMBus.

- Separate DMA requests for master, slave, and monitor functions.

- No chip clocks are required to receive and compare an address as a slave. So, this event can wake up the device from deep-sleep mode.

- Automatic modes optionally allow less software overhead for some use cases.

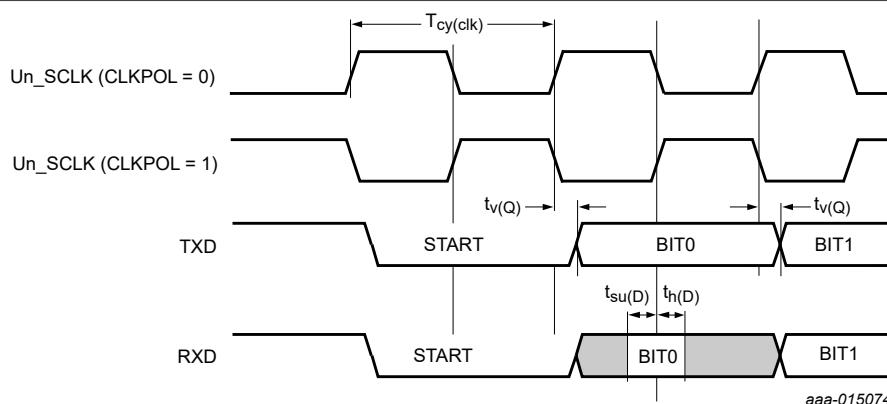

### 7.1.6.3 Flexcomm UART

#### Features

- Maximum bit rates of 6.25 Mbit/s in asynchronous mode and 10 Mbit/s in synchronous mode for USART functions.

- 7, 8, or 9 data bits and 1 or 2 stop bits.