# FXLS8964AF

## 3-Axis Low-g Accelerometer

Rev. 3.3 — 22 October 2021

Preliminary data sheet

## 1 General description

FXLS8964AF is a compact 3-axis MEMS accelerometer designed for use in automotive remote keyless entry (key fob) applications that require ultra-low-power wake-up on motion. The part supports both high-performance and low-power operating modes, allowing maximum flexibility to meet the resolution and power needs for various use case implementations. A number of advanced, integrated digital features enable designers to reduce the overall system power consumption and simplify host data collection.

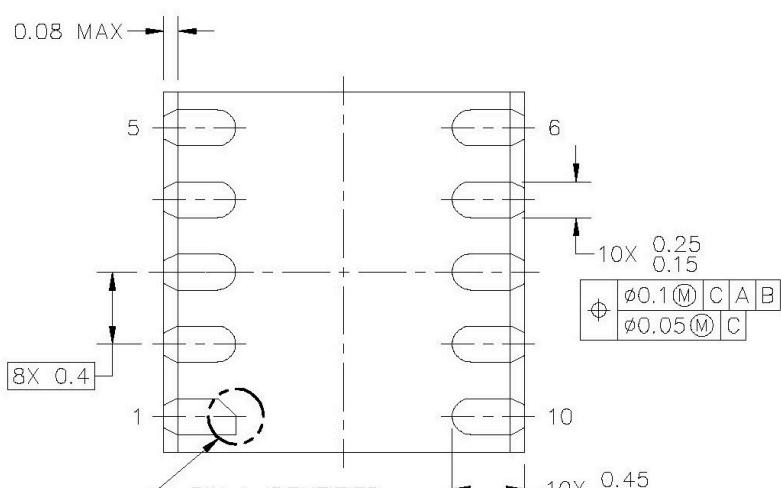

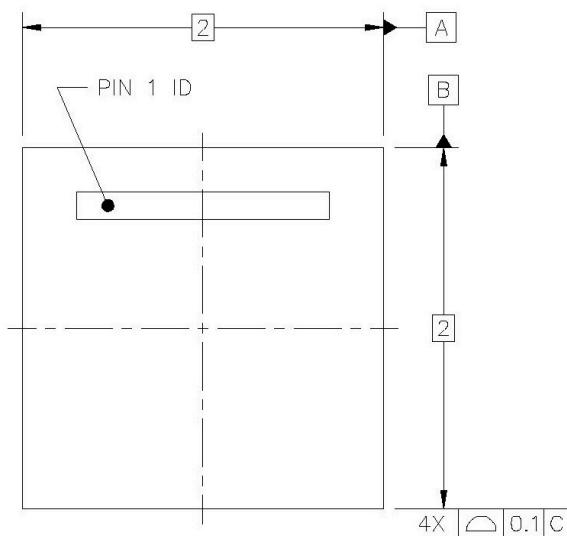

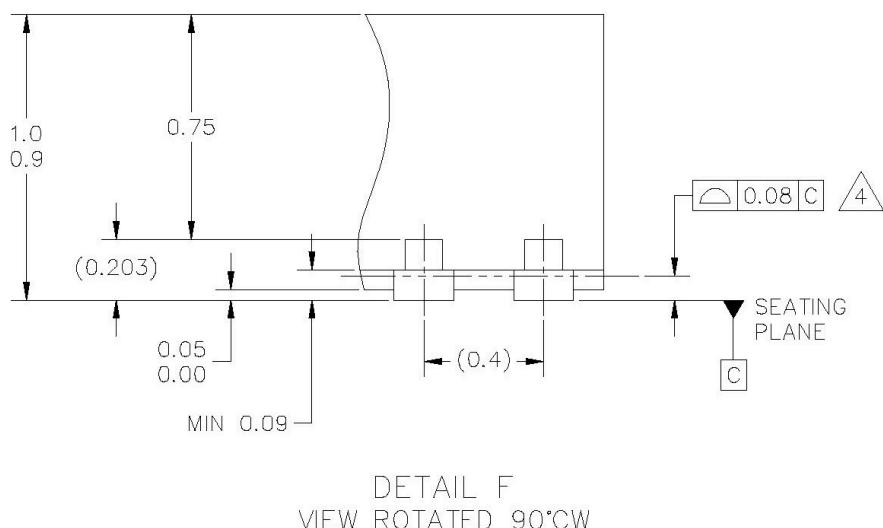

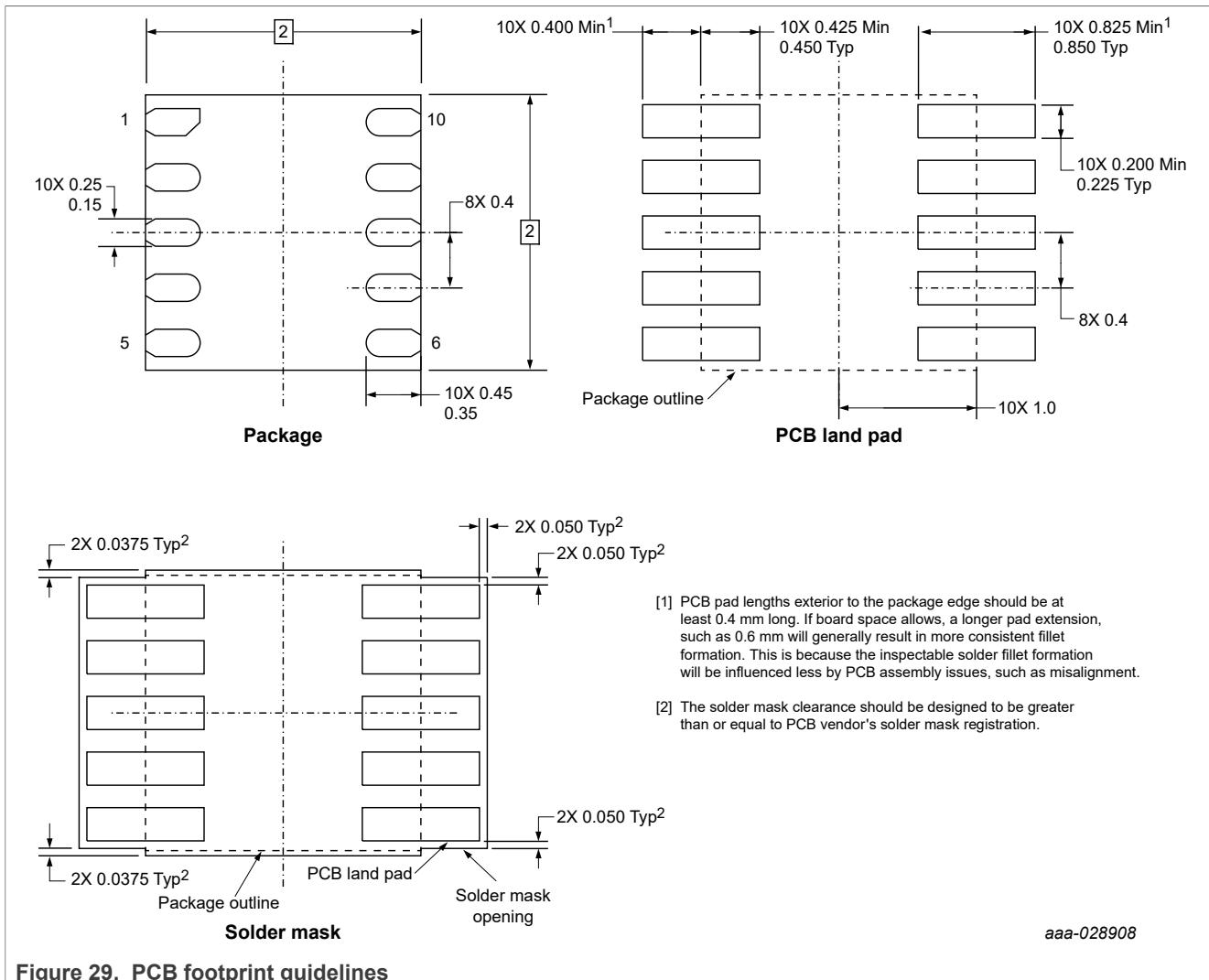

FXLS8964AF is available in a 2 mm x 2 mm x 0.95 mm 10-pin DFN package with 0.4 mm pitch and wettable flanks. The device is qualified to AEC-Q100 and operates over the extended  $-40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$  temperature range. The combination of sensor performance, system power-saving features, and extended over-temperature-range performance makes FXLS8964AF an ideal accelerometer for automotive security and convenience applications.

## 2 Features and benefits

- $\pm 2/4/8/16\text{ g}$  user-selectable, full-scale measurement ranges

- 12-bit acceleration data

- 8-bit temperature sensor data

- Low noise:  $280\text{ }\mu\text{g}/\sqrt{\text{Hz}}$  in high performance mode

- Low-power capability:

- $\leq 1\text{ }\mu\text{A }I_{\text{DD}}$  for ODRs up to 6.25 Hz

- $< 4\text{ }\mu\text{A }I_{\text{DD}}$  for ODRs up to 50 Hz

- Selectable ODRs up to 3200 Hz; Flexible Performance mode allows for custom ODRs with programmable decimation (resolution) and idle-time settings

- 144 byte output data buffer (FIFO/LIFO) capable of storing up to 32 12-bit X/Y/Z data triplets

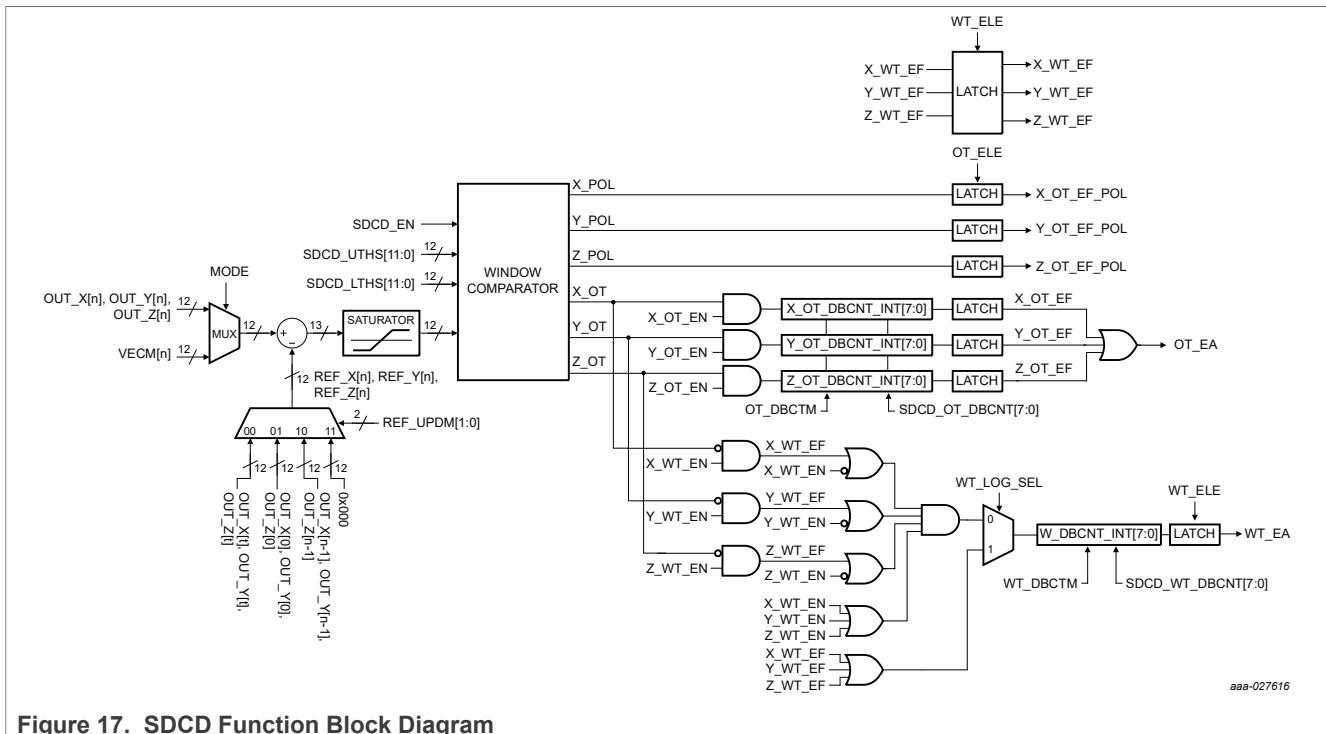

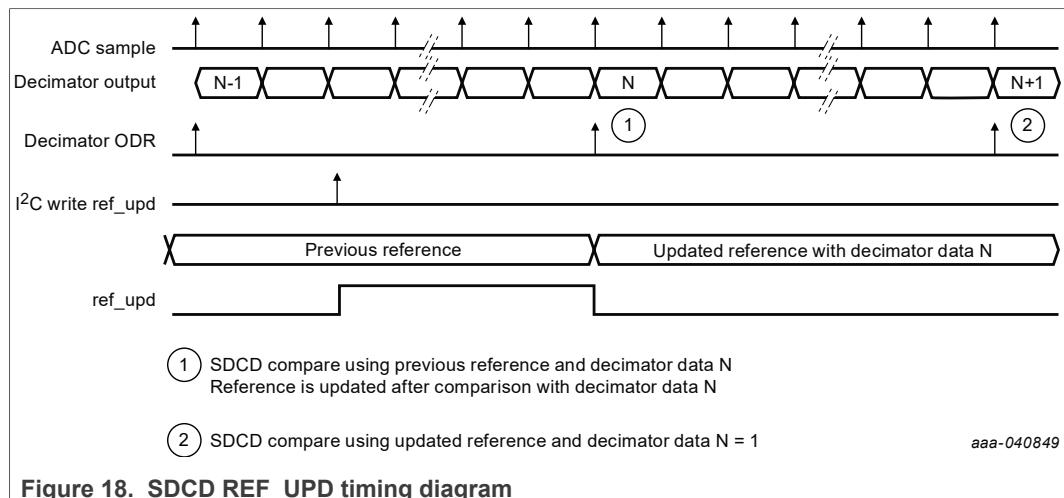

- Flexible Sensor Data Change Detection (SDCD) function for realizing motion or no motion, high-*g*/low-*g*, freefall, and other inertial events

- Autonomous orientation detection function (Portrait/Landscape/Up/Down)

- Dedicated low-power motion-detection mode with one wire interface option

- 12-bit vector magnitude calculation

- Trigger input for synchronizing data collection with an external system

- I<sup>2</sup>C interface frequencies up to 1 MHz; 3- and 4-wire SPI interface with clock frequencies up to 4 MHz

- Bidirectional self-test diagnostic: Device motion or orientation does not impact the result.

## 3 Applications

### 3.1 Automotive security and convenience

- Key fob motion wake-up

## 4 Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                                            |           |

|-------------|---------|------------------------------------------------------------------------------------------------------------|-----------|

|             | Name    | Description                                                                                                | Version   |

| FXLS8964AF  | VSON10  | Plastic, very thin small outline package, no leads; 10 terminals; 0.4 mm pitch; 2 mm x 2 mm x 0.95 mm body | SOT1615-3 |

### 4.1 Ordering options

Table 2. Ordering options

| Part number  | Temperature range | Package description | Shipping      |

|--------------|-------------------|---------------------|---------------|

| FXLS8964AFR3 | –40 °C to +105 °C | DFN-10              | Tape and reel |

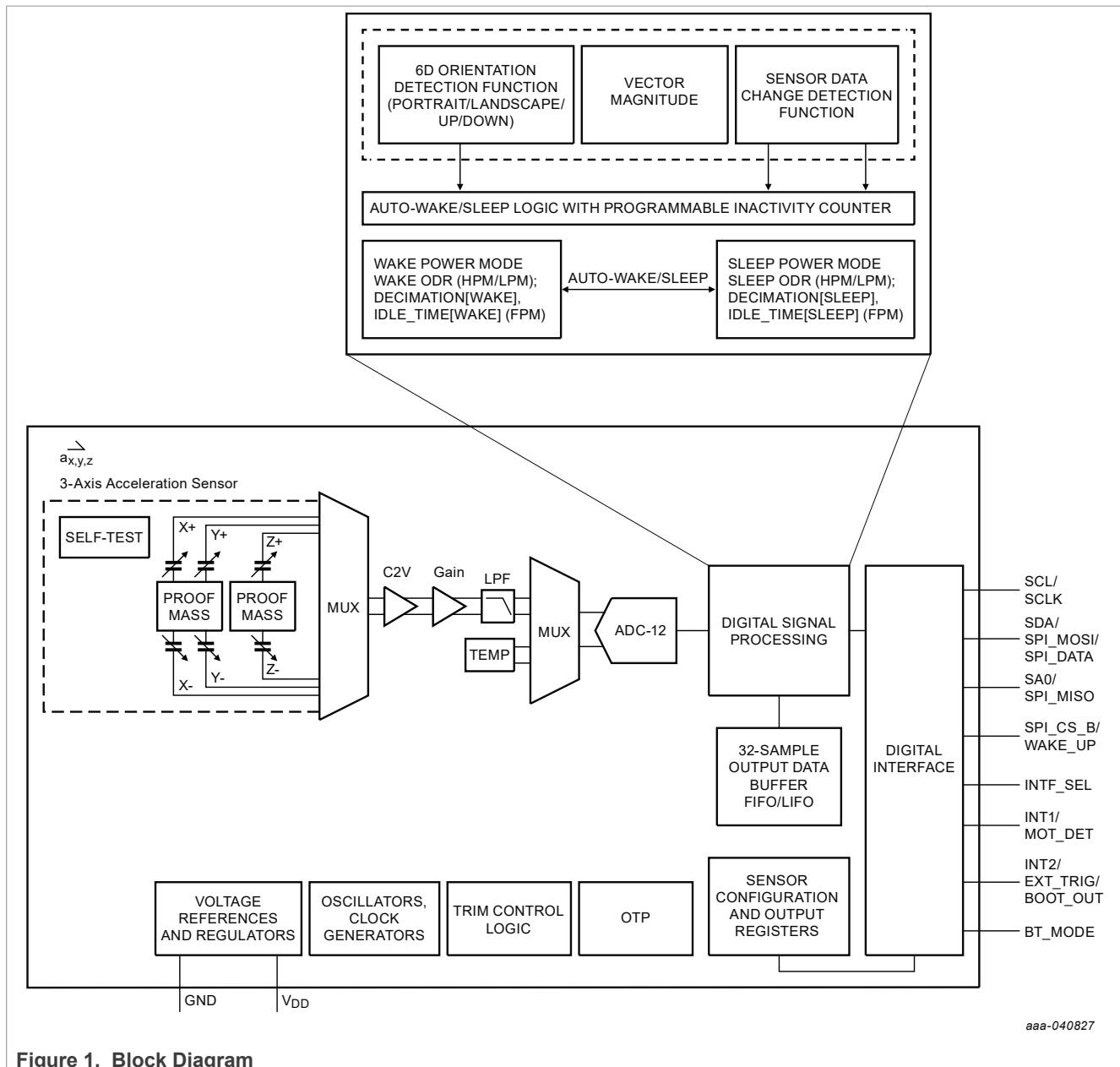

## 5 Block diagram

Figure 1. Block Diagram

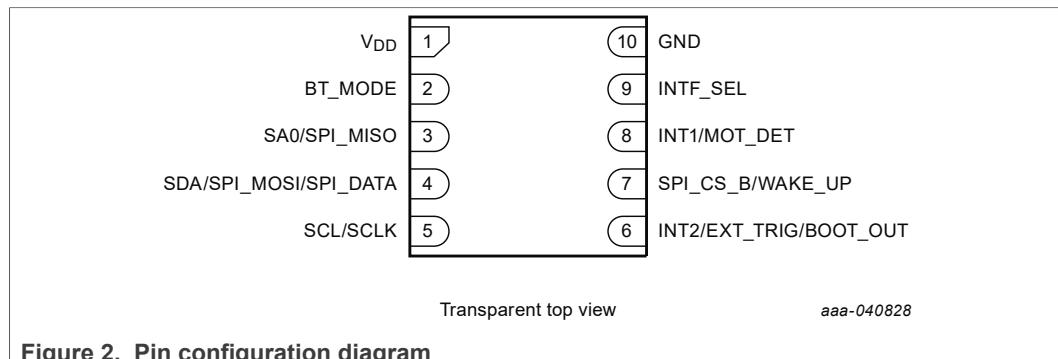

## 6 Pinning information

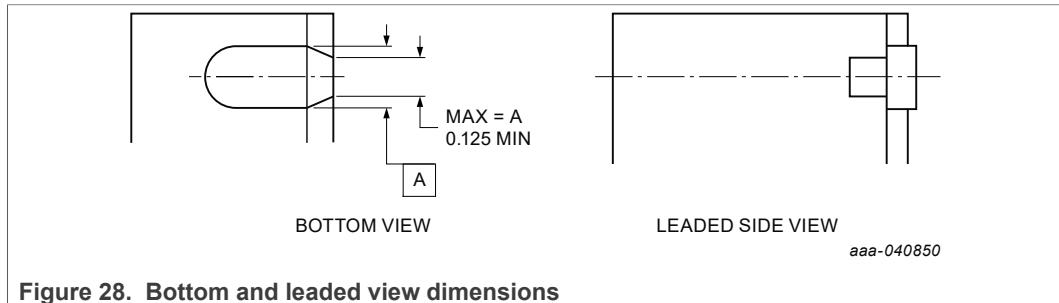

### 6.1 Pinning

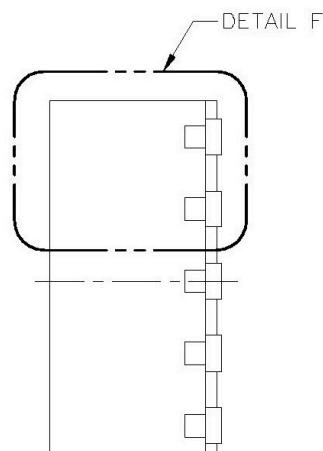

Figure 2. Pin configuration diagram

### 6.2 Pinning description

Table 3. Pin descriptions

| Symbol                    | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>           | 1   | Sensor and digital interface supply voltage: 1.71 VDC to 3.6 VDC.                                                                                                                                                                                                                                                                                                                                                                                                                         |

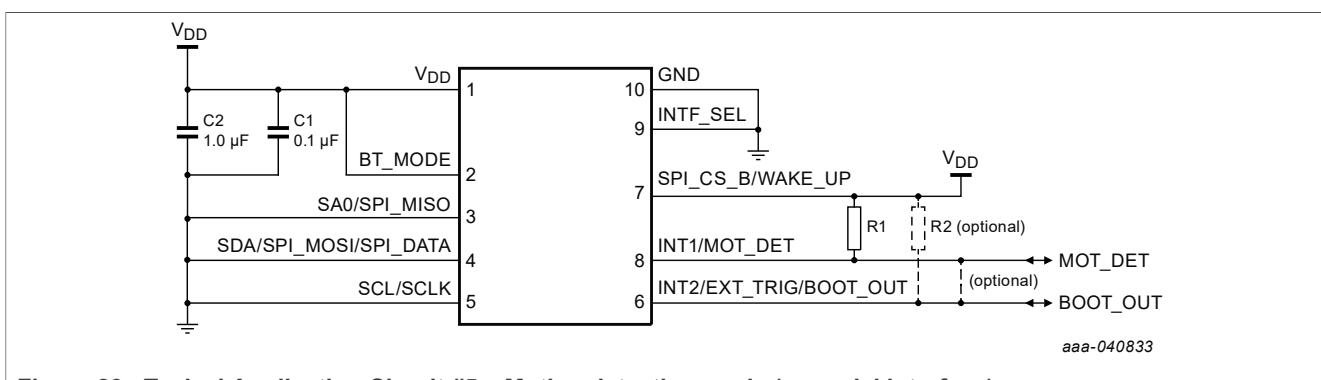

| BT_MODE                   | 2   | Device boot mode selection. <sup>[1]</sup><br>GND: Default operating mode enabled<br>V <sub>DD</sub> : Motion Detection mode enabled                                                                                                                                                                                                                                                                                                                                                      |

| SA0 / SPI_MISO            | 3   | Mode-dependent Multifunction serial interface pin. <sup>[2]</sup><br>INTF_SEL = V <sub>DD</sub> : <ul style="list-style-type: none"><li>SPI_MISO: In 4-wire SPI mode this pin functions as the serial data output.</li><li>SA0: This pin selects the least significant bit of the device I<sup>2</sup>C <a href="#">secondary</a> address.</li></ul>                                                                                                                                      |

| SDA / SPI_MOSI / SPI_DATA | 4   | Mode-dependent Multifunction serial interface pin. <sup>[2]</sup><br>INTF_SEL = V <sub>DD</sub> : <ul style="list-style-type: none"><li>SPI_MOSI: In 4-wire SPI mode this pin functions as the serial data input.</li><li>SPI_DATA<sup>[3]</sup>: In 3-wire SPI mode, this pin functions as the bidirectional serial data input/output.</li></ul> INTF_SEL = GND: <ul style="list-style-type: none"><li>SDA: This pin functions as the I<sup>2</sup>C Serial Data input/output.</li></ul> |

| SCL / SCLK                | 5   | Mode-dependent Multifunction serial interface pin. <sup>[2]</sup><br>INTF_SEL = V <sub>DD</sub> : <ul style="list-style-type: none"><li>SPI serial clock input (3- and 4-wire modes)</li></ul> INTF_SEL = GND: <ul style="list-style-type: none"><li>I<sup>2</sup>C serial clock input</li></ul>                                                                                                                                                                                          |

Table 3. Pin descriptions...continued

| Symbol                        | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT2 / EXT_TRIG /<br>BOOT_OUT | 6   | Mode-dependent multifunction I/O pin 2. <sup>[2]</sup><br>BT_MODE = $V_{DD}$ : Open-drain <sup>[4]</sup> output signaling the device boot process has completed. This pin is typically connected to MOT_DET in a wired-AND configuration; a pull-up resistor is required.<br>BT_MODE = GND: Programmable interrupt output pin 2 <sup>[5]</sup> / External measurement trigger input. This pin should be left unconnected if unused in the application circuit.                                                                                                                                                                                                                          |

| SPI_CS_B / WAKE_UP            | 7   | SPI chip select input, active low / Hibernate mode wake-up pin. <sup>[6]</sup> The WAKE_UP function is only available when BT_MODE = GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT1 / MOT_DET                | 8   | Mode-dependent multifunction I/O pin 1. <sup>[7]</sup><br>BT_MODE = GND: Programmable interrupt output pin 1. <sup>[5]</sup> This pin should be left unconnected if unused in the application circuit.<br>BT_MODE = $V_{DD}$ : MOT_DET multifunction I/O. <sup>[4]</sup> The host MCU sets this pin high through a pull-up resistor to enable motion detection, and drives it low for greater than $T_{MOT-HIB}$ ms to disable motion detection and enter Hibernate mode. FXLS8964AF will pulse the line low for $T_{PULSE-MOT}$ ms after motion is detected. This line may also be used to select the motion detection threshold. See <a href="#">Section 14</a> for more information. |

| INTF_SEL                      | 9   | Device interface mode selection pin.<br>$V_{DD}$ : SPI interface mode <sup>[3]</sup><br>GND: I <sup>2</sup> C interface mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GND                           | 10  | Supply return connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

[1] BT\_MODE state is latched after POR.

[2] Under Hibernate mode, pin configuration is High Impedance.

[3] 3-wire SPI mode may be selected in **SENS\_CONFIG1[SPI\_M]**; 3-wire operation is also possible by directly connecting the SPI\_MISO and SPI\_MOSI pins together on the PCB.

[4] An external pull-up resistor is required on this pin when BT\_MODE =  $V_{DD}$ .

[5] This pin is configurable as either an input or output (push-pull or open-drain/open-source output type), but defaults to a push-pull output after POR, or after exiting Hibernate mode.

[6] Under Hibernate mode, pin configuration is High Impedance (when BT\_MODE =  $V_{DD}$ ) and CMOS Input (when BT\_MODE = GND).

[7] Under Hibernate mode, pin configuration is High Impedance (when BT\_MODE = GND) and CMOS Input (when BT\_MODE =  $V_{DD}$ ).

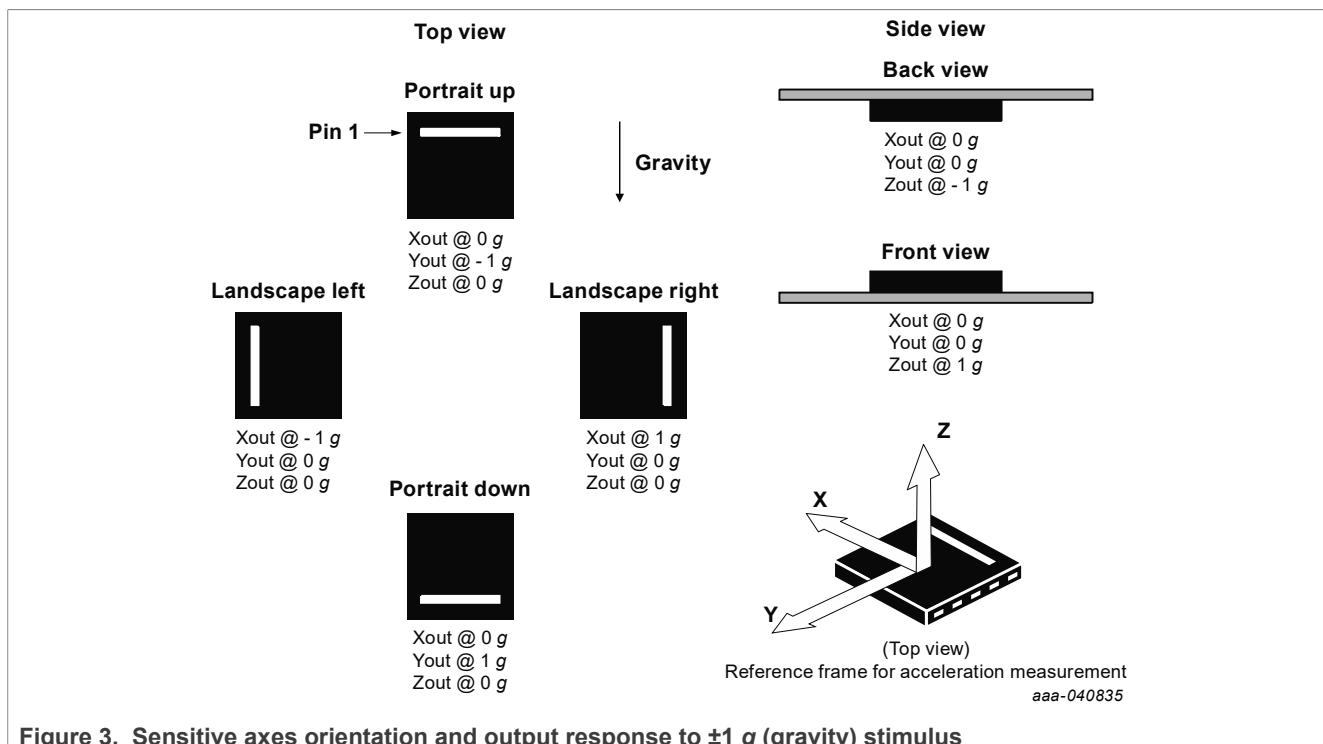

### 6.3 Orientation

Figure 3. Sensitive axes orientation and output response to ±1 g (gravity) stimulus

## 7 Limiting values

The limiting values are the absolute maximum ratings the device can be exposed to without damage. Functional operation at absolute maximum rating is not guaranteed.

Although this device contains circuitry to protect against damage due to high static voltage or electrostatic fields, it is advised that normal precautions be taken to avoid application of any voltage higher than the maximum-rated voltage.

Table 4. Device absolute maximum ratings

| Symbol                 | Rating                                         | Min  | Max     | Unit |

|------------------------|------------------------------------------------|------|---------|------|

| ACC <sub>max-2k</sub>  | Maximum applied acceleration, 0.5 ms duration  | —    | 2,000   | g    |

| ACC <sub>max-10k</sub> | Maximum applied acceleration, 0.1 ms duration  | —    | 10,000  | g    |

| VDD <sub>MAX</sub>     | Maximum sensor supply voltage                  | 0    | +3.6    | V    |

| VIN <sub>MAX</sub>     | Maximum voltage level applied to any input pin | -0.3 | VDD+0.3 | V    |

| T <sub>OP</sub>        | Operating temperature range                    | -40  | +105    | °C   |

| T <sub>STG</sub>       | Storage temperature range                      | -40  | +125    | °C   |

Table 5. ESD and latch-up-protection characteristics

| Symbol    | Rating                                                          | Min        | Unit |

|-----------|-----------------------------------------------------------------|------------|------|

| $V_{HBM}$ | Human Body Model                                                | $\pm 2000$ | V    |

| $V_{CDM}$ | Charged Device Model                                            | $\pm 500$  | V    |

| $I_{LU}$  | Latch-up current at $T = +105^\circ\text{C}$ (per AEC-Q100-004) | $\pm 100$  | mA   |

## CAUTION

This device is sensitive to mechanical shock. Improper handling can cause permanent damage to the part or cause the part to otherwise fail.

## CAUTION

This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices.

Such precautions are described in the *ANSI/ESD S20.20*, *IEC/ST 61340-5*, *JESD625-A* or equivalent standards.

## 8 Recommended operating conditions

Table 6. Nominal operating conditions

| Symbol   | Parameter                   | Min  | Typ | Max  | Unit             |

|----------|-----------------------------|------|-----|------|------------------|

| $V_{DD}$ | Supply voltage              | 1.71 | 3.0 | 3.6  | V                |

| Top      | Operating temperature range | -40  | +25 | +105 | $^\circ\text{C}$ |

## 9 Mechanical characteristics

Table 7. Accelerometer sensor performance parameters

$V_{DD} = 1.8\text{ V to }3.0\text{ V}$ ,  $T = -40\text{ }^\circ\text{C to }105\text{ }^\circ\text{C}$ , unless otherwise noted.

Typical values represent mean or mean  $\pm 1\sigma$  values, depending on the specific parameter.

| Symbol    | Parameter                    | Conditions             | Min | Typ      | Max | Unit       |

|-----------|------------------------------|------------------------|-----|----------|-----|------------|

| $n_{ACC}$ | Output data width            | —                      | —   | 12       | —   | bits       |

| FSR       | Full-scale measurement range | $\pm 2\text{ g}$ mode  | —   | $\pm 2$  | —   | $\text{g}$ |

|           |                              | $\pm 4\text{ g}$ mode  | —   | $\pm 4$  | —   |            |

|           |                              | $\pm 8\text{ g}$ mode  | —   | $\pm 8$  | —   |            |

|           |                              | $\pm 16\text{ g}$ mode | —   | $\pm 16$ | —   |            |

Table 7. Accelerometer sensor performance parameters...continued

$V_{DD} = 1.8 \text{ V to } 3.0 \text{ V}$ ,  $T = -40 \text{ }^{\circ}\text{C to } 105 \text{ }^{\circ}\text{C}$ , unless otherwise noted.Typical values represent mean or mean  $\pm 1 \sigma$  values, depending on the specific parameter.

| Symbol               | Parameter                                                              | Conditions                                                                     | Min   | Typ         | Max     | Unit                           |

|----------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|-------------|---------|--------------------------------|

| SEN                  | Nominal sensitivity                                                    | $\pm 2 \text{ g}$ mode                                                         | 0.87  | 0.98        | 1.12    | mg/LSB                         |

|                      |                                                                        | $\pm 4 \text{ g}$ mode                                                         | 1.74  | 1.95        | 2.23    |                                |

|                      |                                                                        | $\pm 8 \text{ g}$ mode                                                         | 3.47  | 3.91        | 4.46    |                                |

|                      |                                                                        | $\pm 16 \text{ g}$ mode                                                        | 6.94  | 7.81        | 8.93    |                                |

|                      |                                                                        | $\pm 2 \text{ g}$ mode                                                         | 896   | 1024        | 1152    | LSB/g                          |

|                      |                                                                        | $\pm 4 \text{ g}$ mode                                                         | 448   | 512         | 576     |                                |

|                      |                                                                        | $\pm 8 \text{ g}$ mode                                                         | 224   | 256         | 288     |                                |

|                      |                                                                        | $\pm 16 \text{ g}$ mode                                                        | 112   | 128         | 144     |                                |

| SEN <sub>TOL</sub>   | Sensitivity tolerance <sup>[1]</sup>                                   | —                                                                              | —     | $\pm 2.5$   | —       | %SEN                           |

| TCS                  | Temperature coefficient of sensitivity <sup>[1]</sup>                  | $-40 \text{ }^{\circ}\text{C to } +105 \text{ }^{\circ}\text{C}$               | —     | $\pm 0.01$  | —       | %/ $^{\circ}\text{C}$          |

| OFF <sub>PBM</sub>   | Zero-g offset, post-board mount <sup>[1][2]</sup>                      | —                                                                              | -550  | $\pm 250$   | 550     | mg                             |

| TCO <sub>PBM</sub>   | Zero-g offset temperature coefficient, post-board mount <sup>[1]</sup> | $-40 \text{ }^{\circ}\text{C to } +105 \text{ }^{\circ}\text{C}$               | —     | $\pm 1$     | —       | mg/ $^{\circ}\text{C}$         |

| CAS                  | Cross-axis sensitivity <sup>[3]</sup>                                  | $\pm 2/4 \text{ g}$ mode                                                       | —     | $\pm 0.5$   | —       | %                              |

| STOC                 | Self-test output change <sup>[4]</sup>                                 | $\pm 4 \text{ g}$ mode, X axis                                                 | -206  | -139        | -81     | LSB                            |

|                      |                                                                        | $\pm 4 \text{ g}$ mode, Y axis                                                 | 78    | 137         | 207     |                                |

|                      |                                                                        | $\pm 4 \text{ g}$ mode, Z axis                                                 | -727  | -448        | -120    |                                |

|                      |                                                                        | $\pm 8 \text{ g}$ mode, X axis                                                 | -103  | -69         | -40     |                                |

|                      |                                                                        | $\pm 8 \text{ g}$ mode, Y axis                                                 | 38    | 68          | 103     |                                |

|                      |                                                                        | $\pm 8 \text{ g}$ mode, Z axis                                                 | -355  | -223        | -71     |                                |

|                      |                                                                        | $\pm 16 \text{ g}$ mode, X axis                                                | -52   | -35         | -19     |                                |

|                      |                                                                        | $\pm 16 \text{ g}$ mode, Y axis                                                | 19    | 34          | 52      |                                |

|                      |                                                                        | $\pm 16 \text{ g}$ mode, Z axis                                                | -178  | -112        | -35     |                                |

| STOF                 | Self-test offset <sup>[4]</sup>                                        | $\pm 4 \text{ g}$ mode                                                         | -1600 | —           | $+1600$ | LSB                            |

|                      |                                                                        | $\pm 8 \text{ g}$ mode                                                         | -800  | —           | $+800$  |                                |

|                      |                                                                        | $\pm 16 \text{ g}$ mode                                                        | -400  | —           | $+400$  |                                |

| BW <sub>MAX</sub>    | Maximum signal bandwidth                                               | ODR = 3200 Hz                                                                  | —     | 1600        | —       | Hz                             |

| ODR <sub>MAX</sub>   | Maximum ODR                                                            | —                                                                              | —     | 3200        | —       | Hz                             |

| NSD <sub>HPM</sub>   | Noise spectral density, high performance mode                          | $\pm 2 \text{ g}$ mode                                                         | —     | 280         | —       | $\mu\text{g}/\sqrt{\text{Hz}}$ |

| NSD <sub>LPM-1</sub> | Noise spectral density, low-power mode, high-ODR range <sup>[5]</sup>  | $200 \text{ Hz} \leq \text{ODR} \leq 3200 \text{ Hz}$ , $\pm 2 \text{ g}$ mode | —     | 1120 to 280 | —       | $\mu\text{g}/\sqrt{\text{Hz}}$ |

| NSD <sub>LPM-2</sub> | Noise spectral density, low-power mode, low-ODR range <sup>[5]</sup>   | $0.781 \text{ Hz} \leq \text{ODR} < 200 \text{ Hz}$ , $\pm 2 \text{ g}$ mode   | —     | 16.8 to 1.1 | —       | $\text{mg}/\sqrt{\text{Hz}}$   |

[1] Determined with post board mount data using a standard lead-free reflow profile and NXP recommended landing pattern on a 2-layer FR4 PCB with 1.2 mm (47 mil) overall thickness.

[2] Based on characterization data on limited number of parts from 3 lots

[3] See [Cross-axis sensitivity](#) in [Section 20 "Glossary"](#).

[4] See Self-Test in [Section 20 "Glossary"](#)

[5] In low-power mode, higher ODR settings result in a lower noise density figure.

## 10 Electrical characteristics

**Table 8. Electrical characteristics**

$V_{DD}$  = 1.8 V to 3.0 V,  $T$  = –40 °C to 105 °C, unless otherwise noted.

Typical values represent mean or mean  $\pm 1\sigma$  values, depending on the specific parameter.

| Symbol       | Parameter                                     | Conditions                   | Min  | Typ  | Max | Unit |

|--------------|-----------------------------------------------|------------------------------|------|------|-----|------|

| $V_{DD}$     | Supply voltage                                | —                            | 1.71 | 3.0  | 3.6 | V    |

| $IDD_{HPM}$  | Average current draw in High Performance mode | ODR independent, $T$ = 25 °C | —    | 150  | 200 | μA   |

| $IDD_{LPM}$  | Average current draw in low-power mode        | ODR = 3200 Hz, $T$ = 25 °C   | —    | 150  | 200 | μA   |

|              |                                               | ODR = 1600 Hz, $T$ = 25 °C   | —    | 75   | 100 |      |

|              |                                               | ODR = 800 Hz, $T$ = 25 °C    | —    | 38   | 53  |      |

|              |                                               | ODR = 400 Hz, $T$ = 25 °C    | —    | 20   | 30  |      |

|              |                                               | ODR = 200 Hz, $T$ = 25 °C    | —    | 11   | 20  |      |

|              |                                               | ODR = 100 Hz, $T$ = 25 °C    | —    | 5.3  | 10  |      |

|              |                                               | ODR = 50 Hz, $T$ = 25 °C     | —    | 3.1  | 7   |      |

|              |                                               | ODR = 25 Hz, $T$ = 25 °C     | —    | 1.8  | 4   |      |

|              |                                               | ODR = 12.5 Hz, $T$ = 25 °C   | —    | 1.4  | 2.5 |      |

|              |                                               | ODR = 6.25 Hz, $T$ = 25 °C   | —    | 1.0  | 2.0 |      |

|              |                                               | ODR = 3.125 Hz, $T$ = 25 °C  | —    | 0.80 | 1.5 |      |

|              |                                               | ODR = 1.563 Hz, $T$ = 25 °C  | —    | 0.70 | 1.5 |      |

|              |                                               | ODR = 0.781 Hz, $T$ = 25 °C  | —    | 0.65 | 1.5 |      |

| $IDD_{STBY}$ | Supply current draw in Standby mode           | $T$ = 25 °C                  | —    | 0.60 | 1.5 | μA   |

| $IDD_{HIB}$  | Supply current draw in Hibernate mode         | $T$ = 25 °C                  | —    | 15   | 100 | nA   |

Table 8. Electrical characteristics...continued

$V_{DD} = 1.8 \text{ V to } 3.0 \text{ V}$ ,  $T = -40 \text{ }^{\circ}\text{C to } 105 \text{ }^{\circ}\text{C}$ , unless otherwise noted.Typical values represent mean or mean  $\pm 1 \sigma$  values, depending on the specific parameter.

| Symbol                         | Parameter                                                                                                                      | Conditions                                                          | Min            | Typ | Max            | Unit          |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------|-----|----------------|---------------|

| $\text{IDD}_{\text{HPM}}$      | Average current draw in High Performance mode                                                                                  | ODR independent                                                     | —              | —   | 200            | $\mu\text{A}$ |

| $\text{IDD}_{\text{LPM}}$      | Average current draw in low-power mode                                                                                         | ODR = 3200 Hz                                                       | —              | —   | 200            | $\mu\text{A}$ |

|                                |                                                                                                                                | ODR = 1600 Hz                                                       | —              | —   | 100            |               |

|                                |                                                                                                                                | ODR = 800 Hz                                                        | —              | —   | 53             |               |

|                                |                                                                                                                                | ODR = 400 Hz                                                        | —              | —   | 30             |               |

|                                |                                                                                                                                | ODR = 200 Hz                                                        | —              | —   | 25             |               |

|                                |                                                                                                                                | ODR = 100 Hz                                                        | —              | —   | 13             |               |

|                                |                                                                                                                                | ODR = 50 Hz                                                         | —              | —   | 10             |               |

|                                |                                                                                                                                | ODR = 25 Hz                                                         | —              | —   | 8              |               |

|                                |                                                                                                                                | ODR = 12.5 Hz                                                       | —              | —   | 4              |               |

|                                |                                                                                                                                | ODR = 6.25 Hz                                                       | —              | —   | 4              |               |

| $\text{IDD}_{\text{STBY}}$     | Supply current draw in Standby mode                                                                                            | —                                                                   | —              | —   | 4              | $\mu\text{A}$ |

|                                |                                                                                                                                | $T = -40 \text{ }^{\circ}\text{C to } +85 \text{ }^{\circ}\text{C}$ | —              | —   | 300            |               |

| $\text{IDD}_{\text{HIB}}$      | Supply current draw in Hibernate mode                                                                                          |                                                                     |                |     |                | nA            |

| $\text{VIH}$                   | High-level input voltage:<br>SCL/SCLK, SDA/SPI_MOSI/SPI_DATA, SA0, INTF_SEL, BT_MODE, SPI_CS_B/WAKE_UP, MOT_DET, EXT_TRIG pins | —                                                                   | $0.7 * V_{DD}$ | —   | —              | V             |

| $\text{VIL}$                   | Low-level input voltage:<br>SCL/SCLK, SDA/SPI_MOSI/SPI_DATA, SA0, INTF_SEL, BT_MODE, SPI_CS_B/WAKE_UP, MOT_DET, EXT_TRIG pins  | —                                                                   | —              | —   | $0.3 * V_{DD}$ | V             |

| $\text{VOH}$                   | High-level output voltage: INT1/MOT_DET, INT2/BOOT_OUT, SPI_MISO, SPI_DATA pins                                                | $\text{Io} = 500 \mu\text{A}$                                       | $0.9 * V_{DD}$ | —   | —              | V             |

| $\text{VOL}$                   | Low-level output voltage: INT1/MOT_DET, INT2/BOOT_OUT, SPI_MISO, SPI_DATA pins                                                 | $\text{Io} = 500 \mu\text{A}$                                       | —              | —   | $0.1 * V_{DD}$ | V             |

| $\text{VOL}_{\text{SDA, SCL}}$ | Low-level output voltage on SDA and SCL pins                                                                                   | $\text{Io} = 5 \text{ mA}$                                          | —              | —   | 0.4            | V             |

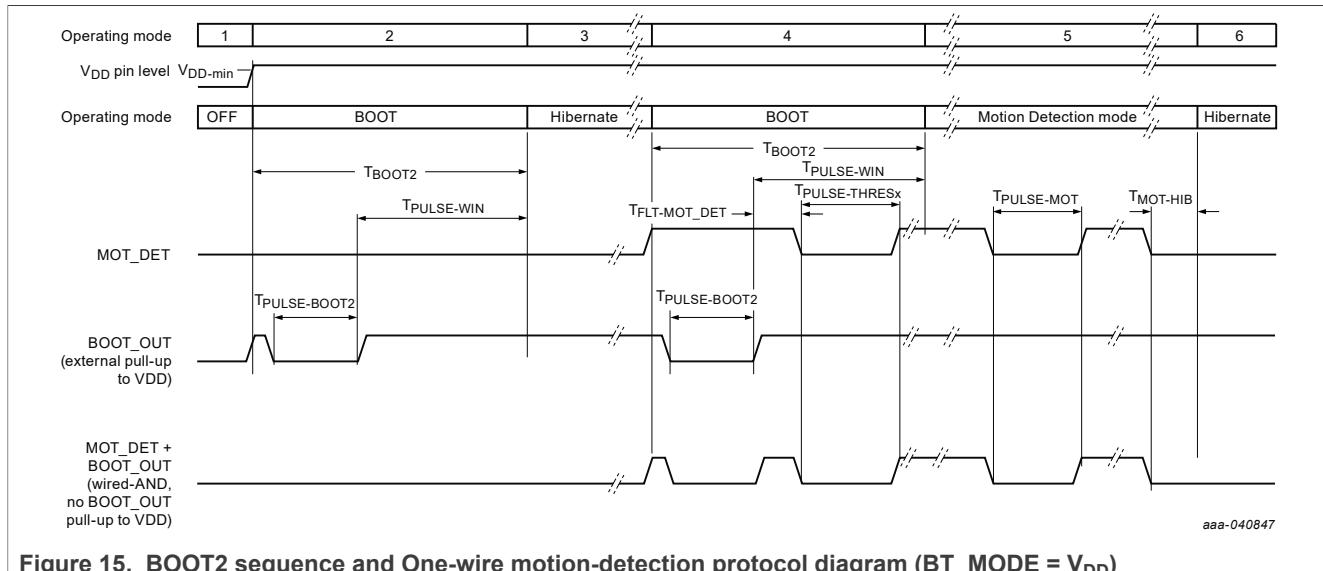

| $\text{T}_{\text{PULSE-MOT}}$  | Motion detected interrupt pulse width                                                                                          | $\text{BT\_MODE} = V_{DD}$                                          | 4.55           | 5   | 5.56           | ms            |

| $\text{T}_{\text{MOT-HIB}}$    | MOT_DET pin low time before entering Hibernate mode <sup>[1]</sup>                                                             | $\text{BT\_MODE} = V_{DD}$                                          | 0.91           | 1   | 6.8            | ms            |

Table 8. Electrical characteristics...continued

$V_{DD} = 1.8 \text{ V to } 3.0 \text{ V}$ ,  $T = -40 \text{ }^{\circ}\text{C to } 105 \text{ }^{\circ}\text{C}$ , unless otherwise noted.Typical values represent mean or mean  $\pm 1 \sigma$  values, depending on the specific parameter.

| Symbol             | Parameter                                                                    | Conditions                                                                                                           | Min   | Typ                                                                   | Max  | Unit               |

|--------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------|------|--------------------|

| $T_{PULSE-WIN}$    | Motion detection threshold setting pulse window                              | $BT\_MODE = V_{DD}$ , $MOT\_DET = \text{HIGH}$                                                                       | 4.55  | 5                                                                     | 5.56 | ms                 |

| $T_{PULSE-THRES1}$ | Motion detection threshold selection 1 – Pulse width range                   | $BT\_MODE = V_{DD}$                                                                                                  | 562.5 | 625                                                                   | 883  | $\mu\text{s}$      |

| $T_{PULSE-THRES2}$ | Motion detection threshold selection 2 – Pulse width range                   | $BT\_MODE = V_{DD}$                                                                                                  | 1125  | 1250                                                                  | 1570 | $\mu\text{s}$      |

| $T_{PULSE-THRES3}$ | Motion detection threshold selection 3 – Pulse width range                   | $BT\_MODE = V_{DD}$                                                                                                  | 2250  | 2500                                                                  | 2950 | $\mu\text{s}$      |

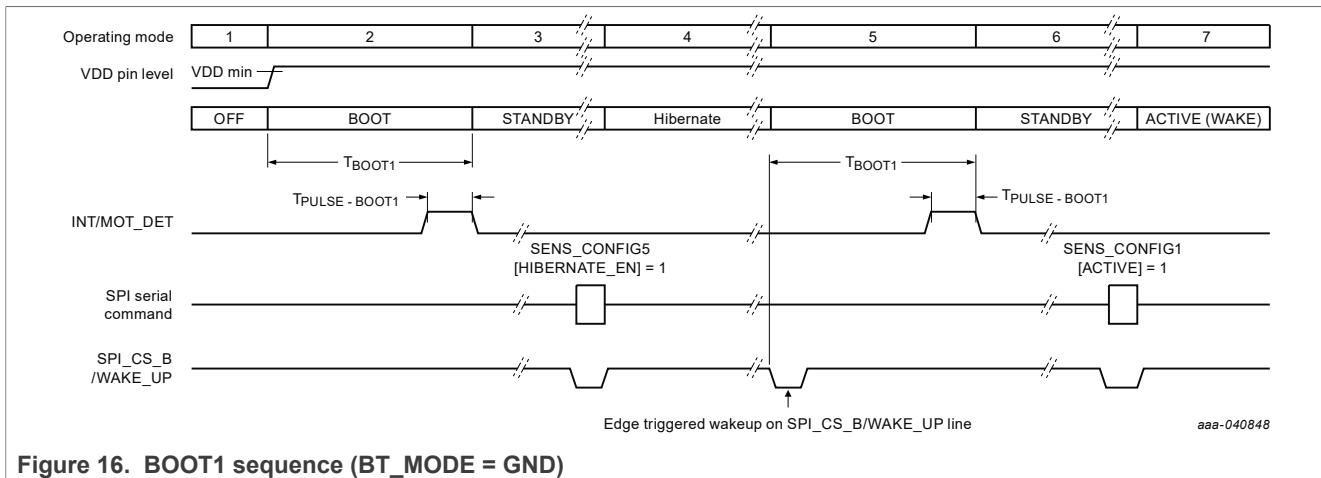

| $T_{PULSE-DRDY}$   | DRDY interrupt output pulse width                                            | $BT\_MODE = \text{GND}$                                                                                              | 29    | 32                                                                    | 35.6 | $\mu\text{s}$      |

| $T_{PULSE-BOOT1}$  | BOOT interrupt output pulse width                                            | $BT\_MODE = \text{GND}$                                                                                              | 58    | 64                                                                    | 71.2 | $\mu\text{s}$      |

| $T_{PULSE-BOOT2}$  |                                                                              | $BT\_MODE = V_{DD}$                                                                                                  | 9     | 10                                                                    | 11.2 | ms                 |

| $ODR_{TOL}$        | Output Data Rate frequency tolerance                                         | —                                                                                                                    | -10   | $\pm 2.5$                                                             | 10   | %ODR               |

| $T_{FLT-MOT_DET}$  | MOT_DET pin deglitch filter time                                             | $BT\_MODE = V_{DD}$                                                                                                  | —     | 10                                                                    | —    | $\mu\text{s}$      |

| $T_{FLT-WAKE_UP}$  | MOT_DET, WAKE_UP pin deglitch filter time (transition out of Hibernate mode) | $BT\_MODE = \text{GND}$ , $SPI\_CS\_B$ / WAKE_UP pin                                                                 | —     | 400                                                                   | —    | ns                 |

|                    |                                                                              | $BT\_MODE = V_{DD}$ , MOT_DET pin                                                                                    | —     | 850                                                                   | —    |                    |

| $T_{BOOT1}$        | Time needed to enter Standby mode after POR or soft reset                    | $BT\_MODE = \text{GND}$                                                                                              | —     | —                                                                     | 1    | ms                 |

| $T_{BOOT2}$        | Time needed to enter Motion Detection mode after POR or soft reset           | $BT\_MODE = V_{DD}$ , MOT_DET = 1                                                                                    | —     | —                                                                     | 17.7 | ms                 |

| $IDD_{BOOT}$       | Boot sequence peak current draw                                              | $T = -40 \text{ }^{\circ}\text{C to } +105 \text{ }^{\circ}\text{C}$ ; with no decoupling capacitors on $V_{DD}$ pin | —     | —                                                                     | 5    | mA                 |

| $T_{ON}$           | Transition time (Standby mode to Active mode with valid data output)         | —                                                                                                                    | —     | $528.5 \mu\text{s}$<br>+ $0.9984 * (DEC - 1) * (1/(ODR * DEC))^{[2]}$ | —    | s                  |

| $T_{OP}$           | Operating temperature range                                                  | —                                                                                                                    | -40   | —                                                                     | +105 | $^{\circ}\text{C}$ |

[1] Max spec covers the situation where an interrupt pulse is issued by the sensor at the same time the host MCU drives MOT\_DET low to signal a hibernate command. In that case, their durations add up.

[2] DEC = decimation factor. The selected ODR and operating mode determines the decimation factor. See [Section 15.13](#) for more information on setting or determining the measurement decimation factor. In LPM, the DEC factor is fixed at 1, making the time to first sample output fixed at  $528.5 \mu\text{s}$  (typ), independent of the selected ODR.

## 11 Temperature sensor characteristics

**Table 9.** Temperature sensor performance parameters

$V_{DD} = 1.8 \text{ V to } 3.0 \text{ V}$ ,  $T = -40 \text{ }^{\circ}\text{C to } 105 \text{ }^{\circ}\text{C}$ , unless otherwise noted.

Typical values represent mean or mean  $\pm 1 \sigma$  values, depending on the specific parameter.

| Symbol           | Parameter                  | Conditions        | Min | Typ         | Max | Unit                          |

|------------------|----------------------------|-------------------|-----|-------------|-----|-------------------------------|

| $n_{TEMP}$       | Output data width          | —                 | —   | 8           | —   | bits                          |

| $FSR_{TEMP}$     | Measurement range          | —                 | —   | -40 to +105 | —   | $^{\circ}\text{C}$            |

| $SEN_{TEMP}$     | Sensitivity                | —                 | —   | 1           | —   | $^{\circ}\text{C}/\text{LSB}$ |

| $SEN_{TOL-TEMP}$ | Sensitivity tolerance      | —                 | —   | $\pm 2.5$   | —   | %                             |

| $OFF_{TEMP}$     | Nominal zero-output offset | Output Code = 00h | —   | 25          | —   | $^{\circ}\text{C}$            |

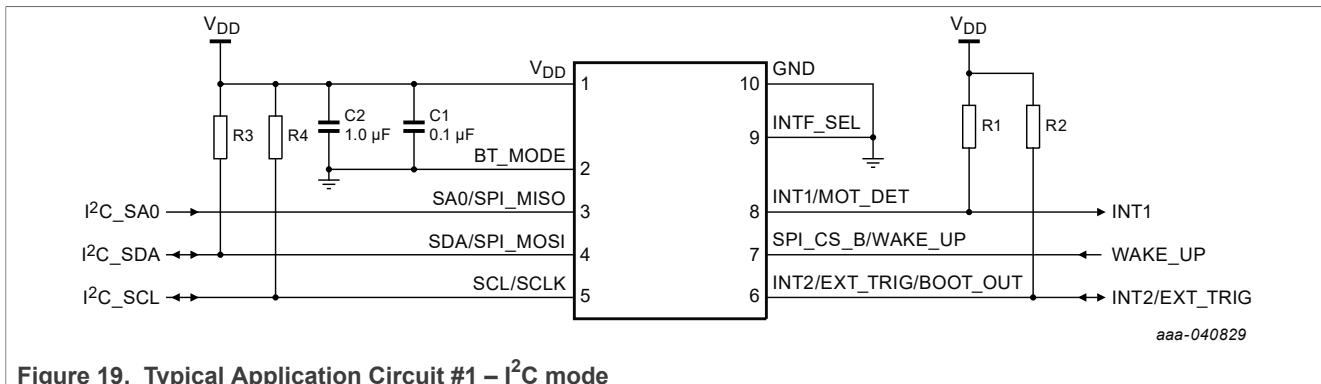

## 12 I<sup>2</sup>C digital interface

The registers embedded within FXLS8964AF may be accessed using an I<sup>2</sup>C interface when the INTF\_SEL pin is tied to GND. If the  $V_{DD}$  supply is not present, the device is in shutdown mode and any communications on the interface are ignored. When the device is on a common I<sup>2</sup>C-bus with other secondary devices, the  $V_{DD}$  supply pin must be left unconnected (high-impedance) when the device supply is turned off to ensure that the internal ESD protection diodes do not become forward biased and prevent the bus from functioning normally (clamping).

The I<sup>2</sup>C secondary interface port of FXLS8964AF is compliant with the following three operating modes as defined in UM10204<sup>[3]</sup>:

- Fast-mode Plus (Fm+) at 1000 kHz

- Fast-mode (Fm) at 400 kHz

- Standard-mode (Sm) at 100 kHz

**Table 10.** I<sup>2</sup>C serial interface pin description

| Pin Name | Pin Description                                              |

|----------|--------------------------------------------------------------|

| SCL      | I <sup>2</sup> C serial clock (pull-up resistor is required) |

| SDA      | I <sup>2</sup> C serial data (pull-up resistor is required)  |

### 12.1 I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C secondary address (7-bit format) is set to 18h when SA0 = 0, and 19h when SA0 = 1.

**Table 11.** FXLS8964AF I<sup>2</sup>C read and write addresses

| SA0 | I <sup>2</sup> C write address | I <sup>2</sup> C read address |

|-----|--------------------------------|-------------------------------|

| 0   | 30h (0011 0000b)               | 31h (0011 0001b)              |

| 1   | 32h (0011 0010b)               | 33h (0011 0011b)              |

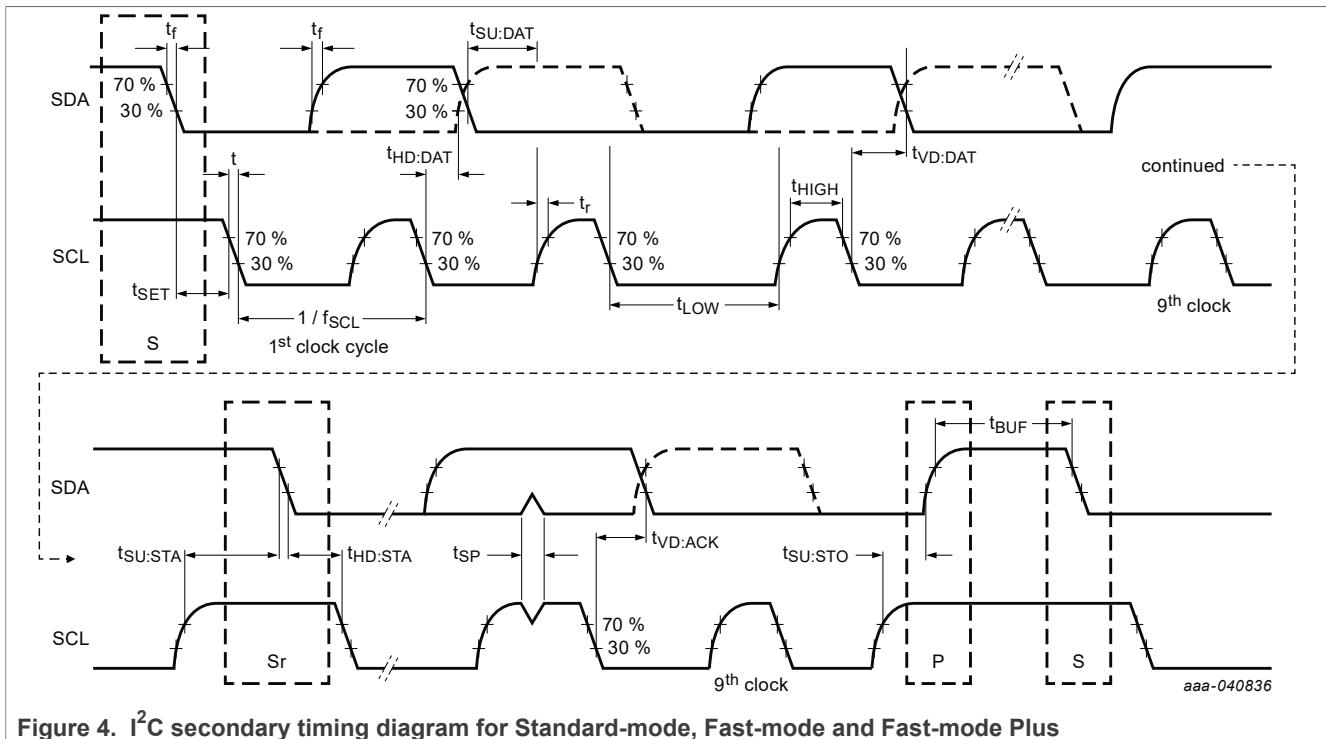

**Table 12. I<sup>2</sup>C secondary timing values for Standard-mode (Sm), Fast-mode (Fm), and Fast-mode Plus (Fm+)**

| Parameter                                                             | Symbol              | I <sup>2</sup> C Standard-mode <sup>[1]</sup> |                     | I <sup>2</sup> C Fast-mode <sup>[1]</sup> |                    | I <sup>2</sup> C Fast-mode Plus <sup>[2]</sup> |                     | Unit |

|-----------------------------------------------------------------------|---------------------|-----------------------------------------------|---------------------|-------------------------------------------|--------------------|------------------------------------------------|---------------------|------|

|                                                                       |                     | Min                                           | Max                 | Min                                       | Max                | Min                                            | Max                 |      |

| SCL clock frequency                                                   | f <sub>SCL</sub>    | 0                                             | 100                 | 0                                         | 400                | 0                                              | 1000                | kHz  |

| Bus free time between STOP and START conditions                       | t <sub>BUF</sub>    | 4.7                                           | —                   | 1.3                                       | —                  | 0.5                                            | —                   | μs   |

| Repeated START hold time                                              | t <sub>HD;STA</sub> | 4                                             | —                   | 0.6                                       | —                  | 0.26                                           | —                   | μs   |

| Repeated START setup time                                             | t <sub>SU;STA</sub> | 4.7                                           | —                   | 0.6                                       | —                  | 0.26                                           | —                   | μs   |

| STOP condition setup time                                             | t <sub>SU;STO</sub> | 4                                             | —                   | 0.6                                       | —                  | 0.26                                           | —                   | μs   |

| SDA valid time <sup>[3]</sup>                                         | t <sub>VD;DAT</sub> | —                                             | 3.45 <sup>[4]</sup> | —                                         | 0.9 <sup>[4]</sup> | —                                              | 0.45 <sup>[4]</sup> | μs   |

| SDA valid acknowledge time <sup>[5]</sup>                             | t <sub>VD;ACK</sub> | —                                             | 3.45 <sup>[4]</sup> | —                                         | 0.9 <sup>[4]</sup> | —                                              | 0.45 <sup>[4]</sup> | μs   |

| SDA setup time                                                        | t <sub>SU;DAT</sub> | 250                                           | —                   | 100 <sup>[6]</sup>                        | —                  | 50                                             | —                   | ns   |

| SCL clock low time                                                    | t <sub>LOW</sub>    | 4.7                                           | —                   | 1.3                                       | —                  | 0.50                                           | —                   | μs   |

| SCL clock high time                                                   | t <sub>HIGH</sub>   | 4.0                                           | —                   | 0.6                                       | —                  | 0.26                                           | —                   | μs   |

| SDA and SCL risetime                                                  | t <sub>r</sub>      | —                                             | 1000                | 20                                        | 300                | —                                              | 120                 | ns   |

| SDA and SCL fall time <sup>[7][8]</sup>                               | t <sub>f</sub>      | —                                             | 300                 | —                                         | 300                | —                                              | 120                 | ns   |

| Pulse width of spikes on SDA and SCL (suppressed by the input filter) | t <sub>SP</sub>     | 0                                             | 50                  | 0                                         | 50                 | 0                                              | 50                  | ns   |

[1] All values referred to VIH(min) and VIL(max) levels.

[2] Should be backward compatible with Fast mode.

[3] t<sub>VD;DAT</sub> referred to the time for data signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

[4] The maximum t<sub>HD;DAT</sub> could be 3.45 μs and 0.9 μs for Standard-mode and Fast-mode respectively, but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time.

[5] t<sub>VD;ACK</sub> = time for ACK signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

[6] A Fast-mode I<sup>2</sup>C device can be used in a Standard mode I<sup>2</sup>C system, but the requirement t<sub>SU;DAT</sub> 250 ns must then be met. Also the acknowledge timing must meet this set-up time.

[7] The maximum t<sub>r</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. The maximum fall time allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

[8] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this specified fall time when considering bus timing.

Figure 4. I<sup>2</sup>C secondary timing diagram for Standard-mode, Fast-mode and Fast-mode Plus

### 12.1.1 General I<sup>2</sup>C operation

There are two signals associated with the I<sup>2</sup>C-bus: the Serial Clock Line (SCL) and the Serial Data line (SDA). SDA is a bidirectional signal used for sending and receiving the data to/from the interface. External pull-up resistors connected to V<sub>DD</sub> are required for SDA and SCL. When the I<sup>2</sup>C-bus is free, SCL and SDA are high.

The maximum practical operating frequency for I<sup>2</sup>C in a given system implementation depends on several factors including the pull-up resistor and voltage values and total bus capacitance (PCB trace + parasitic device capacitances).

The [primary](#) starts a transaction on the bus through a start condition (ST) signal, which is defined as a HIGH-to-LOW transition on SDA line while the SCL line is held HIGH. After the primary transmits the ST signal, the bus is considered busy. The next byte of data transmitted contains the secondary address in the first seven bits, and the eighth bit, the read/write bit, indicates whether the primary is receiving data from the secondary or transmitting data to the secondary. When an address is sent, each device in the system compares the first seven bits after the ST condition with its own address. If they match, the device considers itself addressed by the primary. The ninth clock pulse, following the secondary address byte (and each subsequent byte) is the acknowledge (ACK). The transmitter must release the SDA line during the ACK period. The receiver must then pull the data line low so that it remains stable low during the high period of the acknowledge clock period.

The number of bytes per transfer is unlimited. If a receiver cannot receive another complete byte of data until it has performed some other function, it can hold the SCL line low to force the transmitter into a wait state. Data transfer only continues when the receiver is ready for another byte and releases the clock line. This delay action is called clock stretching. Not all primary devices support clock stretching. This device implements clock stretching—the SCL line may be stretched (pulled low) for up to 1  $\mu$ s when needed.

during a read operation. When applied, clock stretching occurs after the ACK issued by the I<sup>2</sup>C bus primary.

A LOW-to-HIGH transition on the SDA line while the SCL line is high is defined as a stop condition (SP) signal. The primary issuing the SP signal always terminates a write or burst write. A primary should properly terminate a read by not acknowledging a byte at the appropriate time in the protocol, followed by the SP signal. A primary may also issue a repeated start signal (SR) during a transfer.

### 12.1.2 I<sup>2</sup>C read/write operations

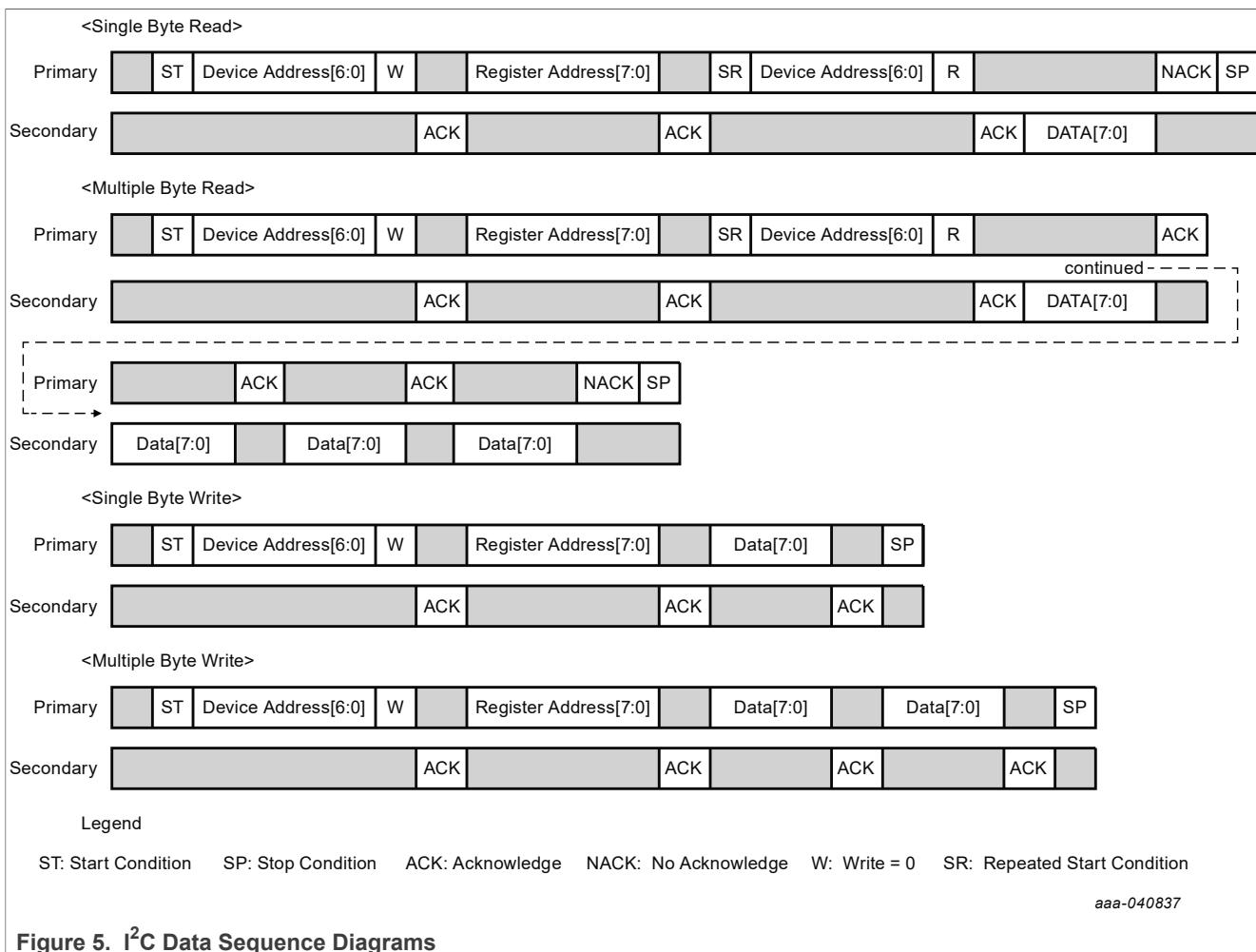

#### 12.1.2.1 Single-byte read

The primary transmits a start condition (ST) to FXLS8964AF, followed by the secondary address, with the R/W bit set to '0' for a write, and the FXLS8964AF sends an acknowledgment. Then the primary transmits the address of the register to read and the FXLS8964AF sends an acknowledgment. The primary transmits a repeated start condition (SR), followed by the secondary address with the R/W bit set to '1' for a read from the previously selected register. The FXLS8964AF then acknowledges and transmits the data from the requested register. The primary does not acknowledge (NAK) the transmitted data and then transmits a stop condition to end the data transfer.

#### 12.1.2.2 Multiple-byte read

When performing a multi-byte or *burst* read, FXLS8964AF automatically increments the register read address pointer after a read command is received. Therefore, after following the steps of a single-byte read, multiple bytes of data can be read from sequential register addresses after each FXLS8964AF acknowledgment (ACK) is received. Data can be read until the primary issues a no acknowledge (NAK), followed by a stop condition (SP) signaling the end of the transfer.

#### 12.1.2.3 Single-byte write

To start a write command, the primary transmits a start condition (ST) to the FXLS8964AF, followed by the secondary address with the R/W bit set to '0' for a write, and the FXLS8964AF sends an acknowledgment. Then the primary transmits the address of the register to write to, and the FXLS8964AF sends an acknowledgment. Then the primary transmits the 8-bit data to write to the designated register and the FXLS8964AF sends an acknowledgment signaling it has received the data. Since this transmission is complete, the primary transmits a stop condition (SP) to end the data transfer. The data sent to the FXLS8964AF is now stored in the appropriate register.

#### 12.1.2.4 Multiple-byte write

FXLS8964AF automatically increments the register address write pointer after a write command is received. Therefore, after following the steps of a single-byte write, multiple bytes of data can be written to sequential registers after each acknowledgment (ACK) is received.

### 12.1.2.5 I<sup>2</sup>C data sequence diagrams

Figure 5. I<sup>2</sup>C Data Sequence Diagrams

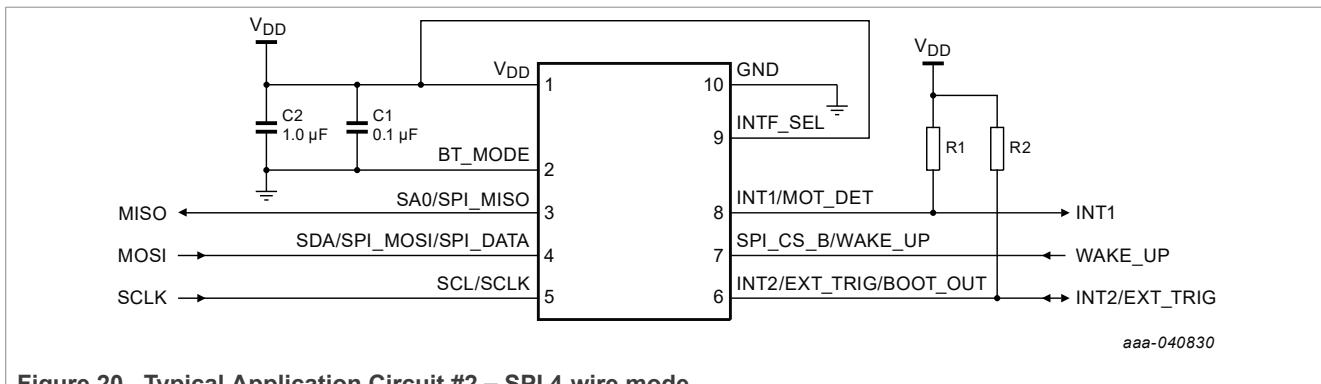

## 13 SPI interface

The SPI interface is a classic primary/secondary serial port. FXLS8964AF is always considered to be the secondary device and therefore never initiates communication with the host processor.

The SPI interface of FXLS8964AF is compatible with interface mode 00, corresponding to CPOL = 0 and CPHA = 0.

For CPOL = 0, the idle value of the clock is zero, and the active value of the clock is 1. For CPHA = 0, data is captured on the rising edge (low to high transition) of the clock, and data is propagated on the falling edge (high to low transition) of the clock.

### 13.1 General SPI operation

The SPI\_CS\_B pin is driven low at the start of a transaction, held low during the transfer, and then driven high again after the transaction is completed. During a transaction, the primary toggles the clock (SCLK). The SCLK polarity is defined as having an idle value that is low, and an active phase that is high (CPOL = 0). Serial input and output data is captured on the rising edge of the clock and propagated on the falling edge (CPHA = 1).

0). Single-byte read and single-byte write operations are completed in 24 SCLK cycles; multiple-byte reads and writes are completed in additional multiples of 8 SCLK cycles per read or written byte. The first SCLK cycle latches the R/W (Read/Write) bit to select whether the desired operation is a read (R/W = 1) or a write (R/W = 0). The following seven SCLK cycles are used to latch the register read or write address.

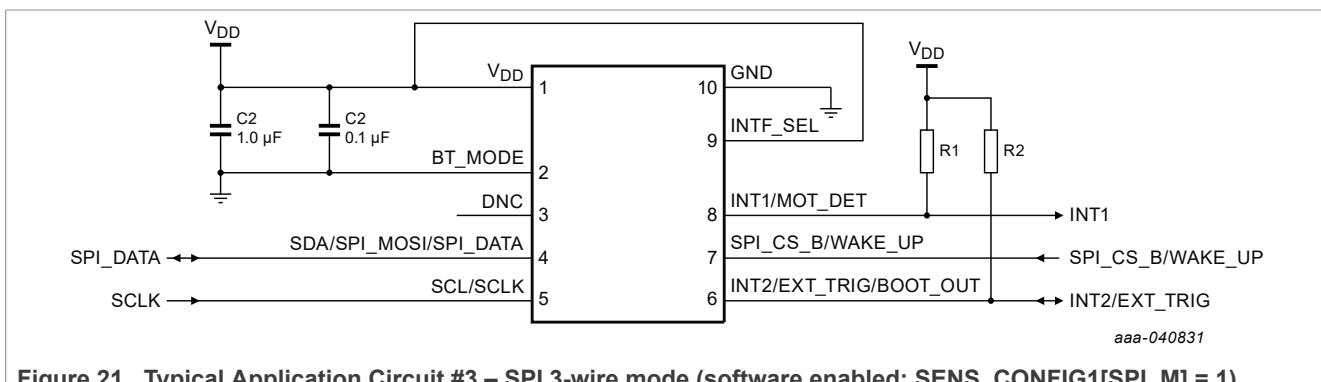

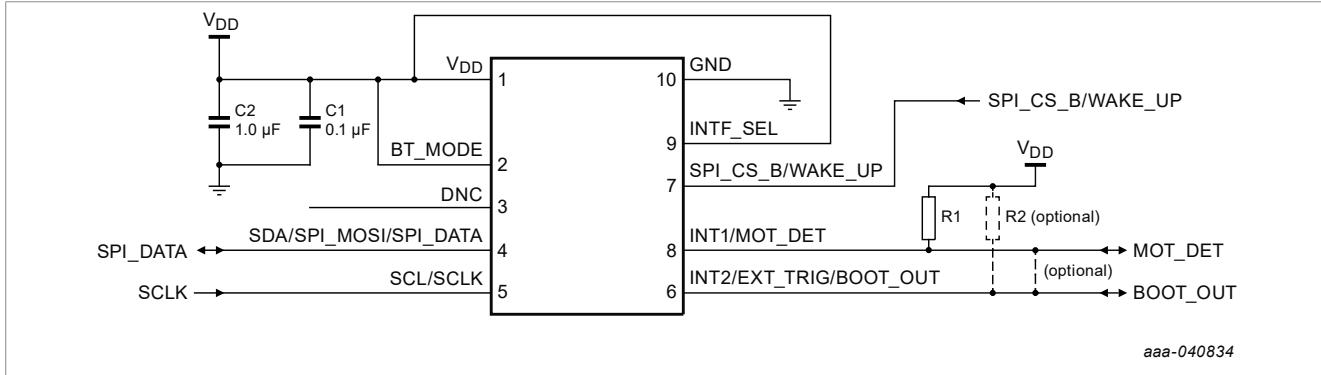

**Note:** 4-wire SPI interface mode is the default out of POR or after a soft reset. In order to select 3-wire SPI interface mode, set the **SENS\_CONFIG1[SPI\_M]** = 1.

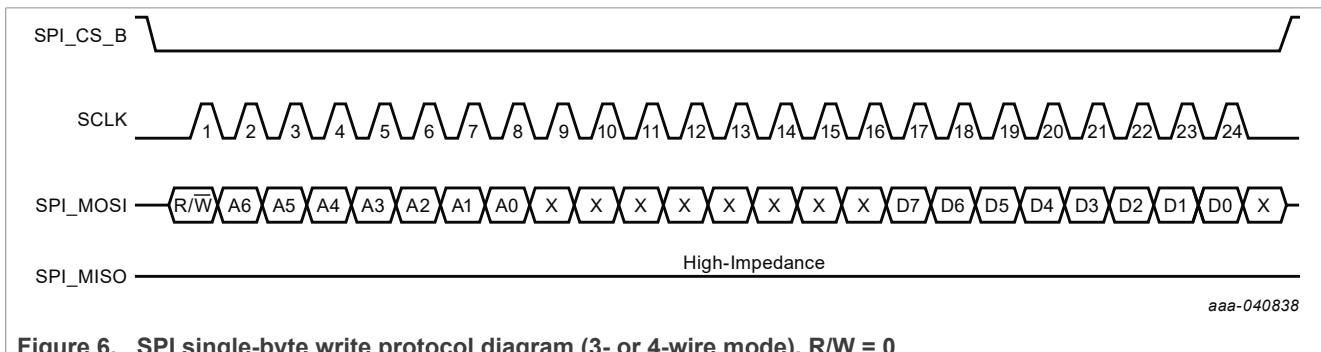

### 13.2 SPI write operations with 3- or 4-wire mode

A write operation is initiated by transmitting a 0 for the R/W bit. Then, the 7-bit register write address, A[6:0], is transmitted in MSB first order. Following this first byte, a second byte of 0s or 1s (don't care condition) transfers, followed by the actual data to write in the third group of 8 SCLK cycles (clock pulses 17 through 24) in MSB first order. [Figure 6](#) shows the bus protocol for a single-byte register write operation in either 3- or 4-wire SPI mode.

Figure 6. SPI single-byte write protocol diagram (3- or 4-wire mode), R/W = 0

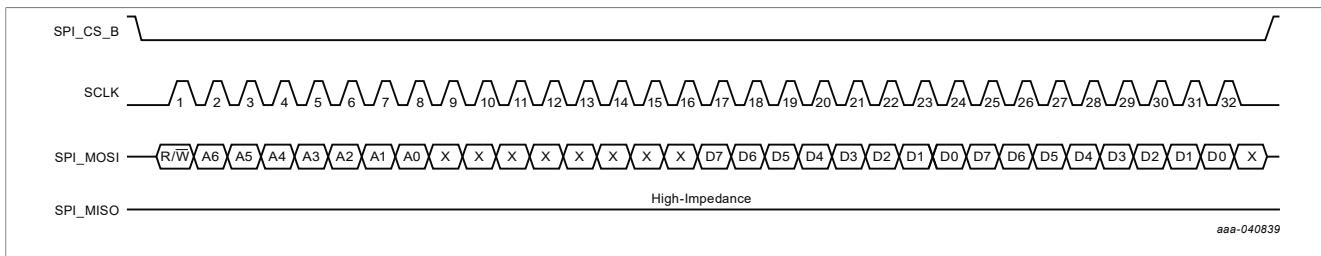

Multiple-byte write operations are performed similarly to the single-byte write sequence, but with additional data bytes transferred over additional 8 SCLK cycle periods. FXLS8964AF auto-increments the register write address so that every eighth clock edge latches the address for the next register write address. When the desired number of bytes has been written, a rising edge on the SPI\_CS\_B pin terminates the transaction. [Figure 7](#) shows the bus protocol for multiple-byte register write operations in either 3- or 4-wire SPI mode.

Figure 7. SPI multiple-byte write protocol diagram (3- or 4-wire mode), R/W = 0

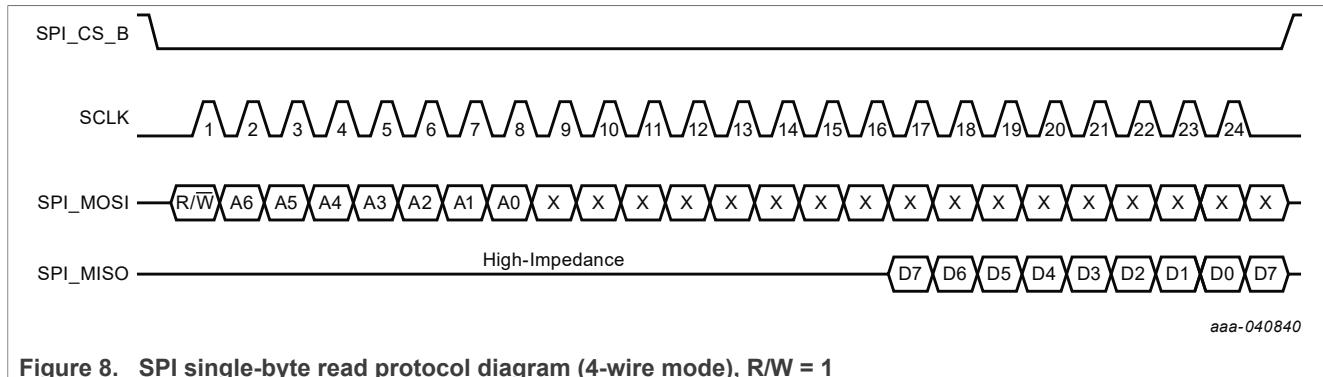

### 13.3 SPI read operations with 4-wire mode

A register read operation is initiated by transmitting a 1 for the R/W bit. Then, the 7-bit register read address, A[6:0] is encoded in the first byte. Following this first byte, a second byte of 0s or 1s (don't care condition) transfers. After this transfer completes, the next 8 SCLK cycles (pulses 17 through 24) output the selected register content on the

SPI\_MISO line in MSB first order. [Figure 8](#) shows the bus protocol for a single-byte read operation.

Figure 8. SPI single-byte read protocol diagram (4-wire mode), R/W = 1

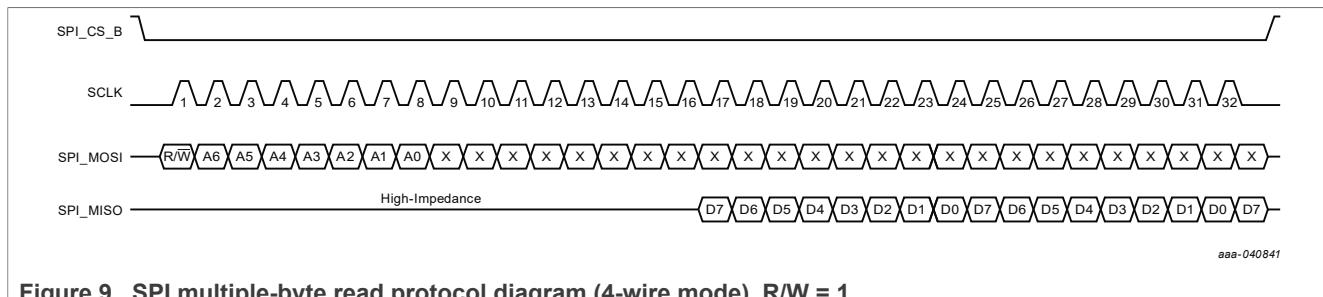

Multiple-byte read operations are performed similarly to single-byte reads with additional bytes read out in multiples of eight SCLK cycles. FXLS8964AF auto-increments the register read address so that every eighth clock edge latches the address of the next sequential register read address. When the desired number of bytes has been read, a rising edge on SPI\_CS\_B terminates the transaction.

Figure 9. SPI multiple-byte read protocol diagram (4-wire mode), R/W = 1

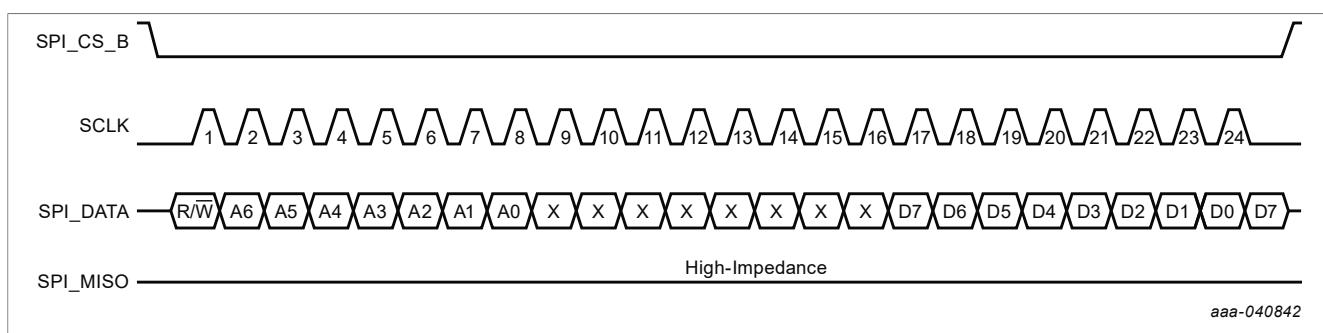

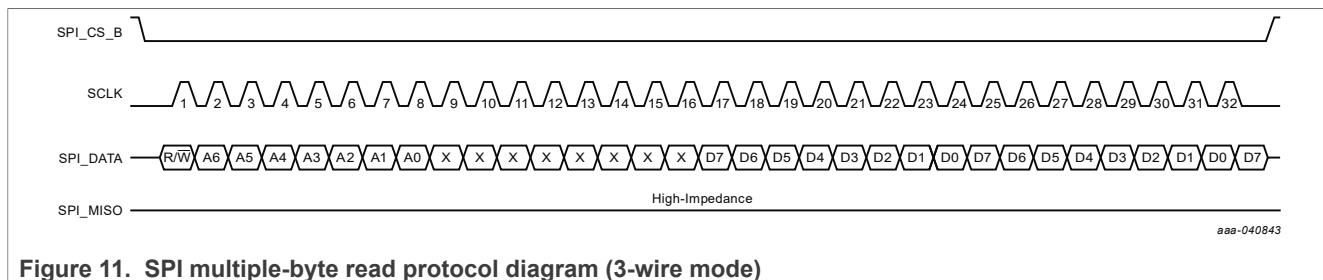

### 13.4 SPI read operations with 3-wire mode

FXLS8964AF can be configured to operate in 3-wire software enabled SPI mode. In this mode, the SPI\_MISO pin is left unconnected and the SPI\_MOSI pin becomes a bidirectional input/output pin (SPI\_DATA). Read operations in 3-wire mode are the same as write operations in 3- and 4-wire modes, except that at the end of the address cycle (falling edge of clock pulse 16), the SPI\_DATA pin automatically switches from an input to an output and with bit D7 as the current output state.

Figure 10. SPI single-byte read protocol diagram (3-wire mode)

Figure 11. SPI multiple-byte read protocol diagram (3-wire mode)

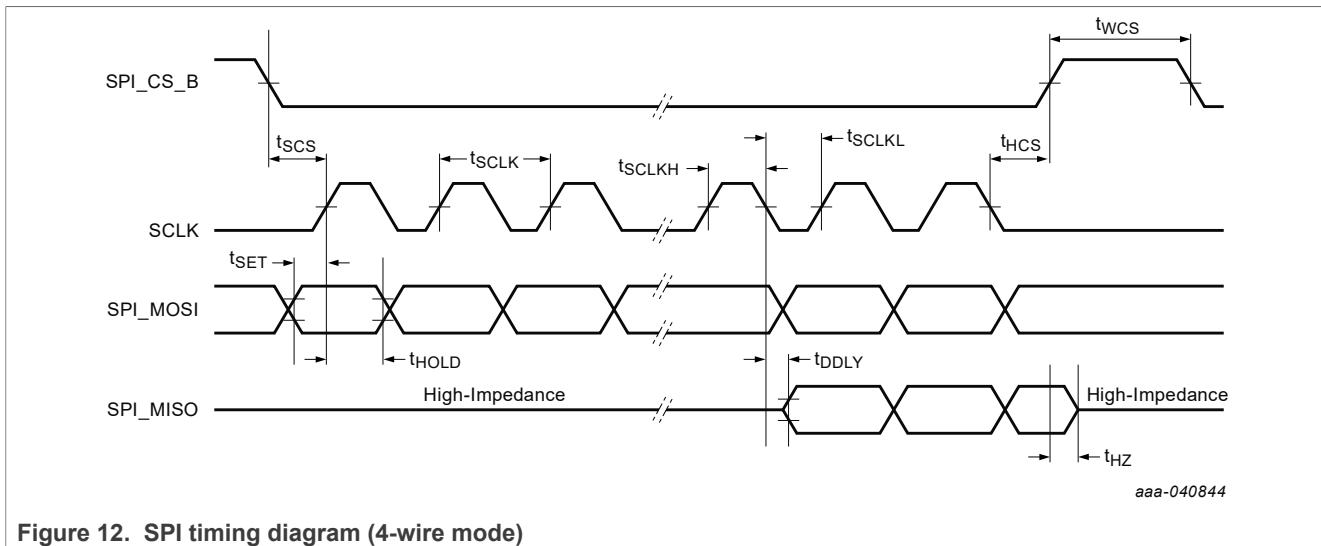

### 13.5 SPI timing specifications (4-wire mode and 3-wire hardwired modes)

[Table 13](#) and [Figure 12](#) specify and illustrate the minimum and maximum timing parameter values for correct SPI interface functionality when FXLS8964AF is operated in 4-wire and 3-wire hardwired SPI modes. FXLS8964AF only supports SPI mode 00, corresponding to CPOL = 0, and CPHA = 0. In this mode, the active state of the clock is high and the idle state is low. Data is latched on the rising edge of the clock and propagated on the falling edge. All timing specifications shown in [Table 13](#) were determined under the following conditions: 10 pF capacitor and 1 kΩ pull-up resistor present on all SPI signals, 105 °C, 1.8 V.

Table 13. Secondary timing values

| Label  | Description                                                     | Specifications |      | Unit |

|--------|-----------------------------------------------------------------|----------------|------|------|

|        |                                                                 | Min.           | Max. |      |

| fSCLK  | SCLK frequency                                                  | 0              | 4    | MHz  |

| tSCLK  | SCLK Period                                                     | 250            | —    | ns   |

| tSCLKH | SCLK high time                                                  | 100            | —    | ns   |

| tSCLKL | SCLK low time                                                   | 100            | —    | ns   |

| tHZ    | Hold time for SPI_MISO signal (transition back to high-z state) | —              | 15   | ns   |

| tSCS   | Setup time for SPI_CS_B signal                                  | 125            | —    | ns   |

| tHCS   | Hold time for SPI_CS_B signal                                   | 240            | —    | ns   |

| tWCS   | Inactive time for SPI_CS_B signal                               | 600            | —    | ns   |

| tSET   | Data setup time for SPI_MOSI signal                             | 10             | —    | ns   |

| tHOLD  | Data hold time for SPI_MOSI signal                              | 10             | —    | ns   |

| tDDLY  | Setup time for SPI_MISO signal (transition out of high-z state) | —              | 50   | ns   |

Figure 12. SPI timing diagram (4-wire mode)

### 13.6 SPI timing specifications (software enabled 3-wire mode)

[Table 14](#) and [Figure 13](#) specify and illustrate the minimum and maximum timing parameter values for correct SPI interface functionality when FXLS8964AF is operated in 3-wire (software enabled) SPI mode. FXLS8964AF only supports SPI mode '00', corresponding to CPOL = 0, and CPHA = 0. In this mode, the active state of the clock is high and the idle state is low. Data is latched on the rising edge of the clock and propagated on the falling edge. All timing specifications shown in [Table 14](#) were determined under the following conditions: 10 pF capacitor and 1 kΩ pull-up resistor present on all SPI signals, 105 °C, 1.8 V.

**Note:** When FXLS8964AF is operated in 3-wire SPI mode - by setting **SENS\_CONFIG1[SPI\_M]** = 1 - the SA0/SPI\_MISO pin is always placed in a high impedance (high-z) state, with the SPI\_MISO pin output driver disabled (tri-stated).

Table 14. Secondary timing values

| Label  | Description                                                           | Specifications |      | Unit |

|--------|-----------------------------------------------------------------------|----------------|------|------|

|        |                                                                       | Min.           | Max. |      |

| fSCLK  | SCLK frequency                                                        | 0              | 4    | MHz  |

| tSCLK  | SCLK Period                                                           | 250            | —    | ns   |

| tSCLKH | SCLK high time                                                        | 100            | —    | ns   |

| tSCLKL | SCLK low time                                                         | 100            | —    | ns   |

| tSCS   | Setup time for SPI_CS_B signal                                        | 125            | —    | ns   |

| tHCS   | Hold time for SPI_CS_B signal                                         | 240            | —    | ns   |

| tHZ    | Hold time for SPI_DATA signal transition back to high-impedance state | —              | 25   | ns   |

| tWCS   | Inactive time for SPI_CS_B signal                                     | 600            | —    | ns   |

| tSET   | Data setup time for SPI_DATA signal                                   | 10             | —    | ns   |

| tHOLD  | Data hold time for SPI_DATA signal                                    | 10             | —    | ns   |

| tDDLY  | Data setup time for SPI_DATA signal (output phase)                    | —              | 50   | ns   |

Figure 13. SPI timing diagram (3-wire mode)

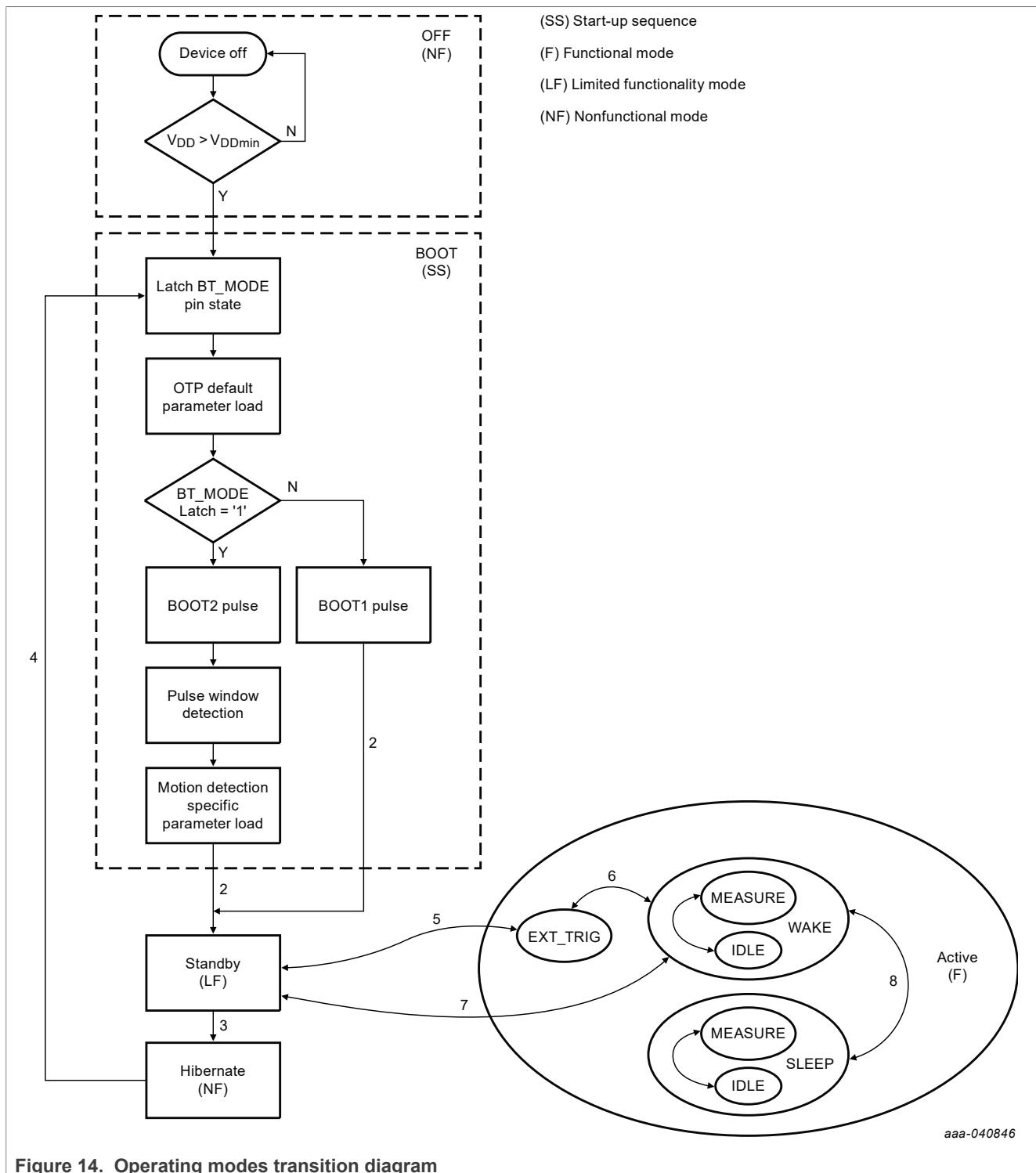

## 14 Operating modes

Table 15. FXLS8964AF operating modes descriptions

| Mode <sup>[1]</sup> | I <sup>2</sup> C/SPI bus state | V <sub>DD</sub> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|--------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF                 | Unavailable                    | < 1.71 V        | <p>Communication with FXLS8964AF is not possible, but communications with other devices on the same I<sup>2</sup>C/SPI bus is possible provided the V<sub>DD</sub> supply pin is left floating/unconnected and not connected to GND.</p> <p>If V<sub>DD</sub> is not left floating/unconnected, the ESD protection diodes on the interface pins could become forward biased and clamp the bus, preventing normal operation.</p> <p>As soon as the supply reaches 1.71 V, the device BOOT process begins.</p>                                                                                                                                                                                                                                                                                                                                                |

| BOOT                | Unavailable                    | ≥ 1.71 V        | <p><b>BT_MODE = GND:</b></p> <p>In this phase, the device is initialized and any default configuration parameters are loaded from OTP memory. When this phase is complete, the SRC_BOOT bit is set and a T<sub>PULSE-BOOT1</sub> <math>\mu</math>s pulse may be signaled on either one of the INT1/2 pins (defaults enabled on the INT1 pin after POR).</p> <p><b>BT_MODE = V<sub>DD</sub>:</b></p> <p>In this phase, the device is initialized and any default configuration parameters are loaded from OTP memory, along with any default Motion Detection function specific parameters. When the default configuration parameters are loaded from OTP memory, the SRC_BOOT bit is set and a boot pulse, T<sub>PULSE-BOOT2</sub>, can be signaled on the INT2 pin. By default, the boot pulse is routed to INT2 pin and cannot be routed to INT1 pin.</p> |

Table 15. FXLS8964AF operating modes descriptions...continued

| Mode <sup>[1]</sup>                    | I <sup>2</sup> C/SPI bus state | V <sub>DD</sub> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|--------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hibernate <sup>[2]</sup>               | Unavailable                    | ≥ 1.71 V        | <p>The wake-up detection circuit is active, but all other analog and digital blocks are disabled to minimize the current drawn on the V<sub>DD</sub> pin. I<sup>2</sup>C and SPI interfaces are not available, and all previously written register settings are lost.</p> <p><b>BT_MODE = GND:</b></p> <p>The host must toggle the SPI_CS_B / WAKE-UP pin (low-to-high or high-to-low) in order to initiate a transition back into Standby mode before attempting communications with the device. The host must wait T<sub>BOOT1</sub> ms for the boot process to complete.</p> <p><b>BT_MODE = V<sub>DD</sub>:</b></p> <p>The INT1/MOT_DET pin is set high (level sensitive) through an external pull-up resistor; the device then exits Hibernate mode and starts the BOOT process. The host must wait T<sub>BOOT2</sub> ms for the boot process to complete and the motion detection process to begin. Communication with the device over the I<sup>2</sup>C or SPI interfaces is possible after the BOOT process completes.</p> |

| Standby                                | Available                      | ≥ 1.71 V        | Sensor and analog blocks are disabled; I <sup>2</sup> C and SPI interfaces are available.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Active <sup>[3][4]</sup> (WAKE/ SLEEP) | Available                      | ≥ 1.71 V        | <p>Sensor and analog blocks are enabled when needed (power cycled). I<sup>2</sup>C and SPI interfaces are available.</p> <p><b>BT_MODE = GND:</b></p> <p>FXLS8964AF can automatically transition between the Active SLEEP and WAKE sub-modes when activity/inactivity is detected. Setting <b>ASLP_COUNT</b> ≥ 1 enables the Auto-WAKE/SLEEP mode.</p> <p><b>BT_MODE = V<sub>DD</sub>:</b></p> <p>The Auto-WAKE/SLEEP function is not typically used in this mode (defaults to disabled), but the host may enable Auto-WAKE/SLEEP by configuring it through the register interface.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Active <sup>[5]</sup> (EXT_TRIG)       | Available                      | ≥ 1.71 V        | <p>All blocks are enabled when needed (power cycled). I<sup>2</sup>C and SPI interfaces are able to respond to read and write commands.</p> <p><b>BT_MODE = GND:</b></p> <p><b>SENS_CONFIG4[INT2_FUNC] = 1</b></p> <p>FXLS8964AF automatically transitions between EXT_TRIG and Active mode upon receiving a trigger signal (low-to-high transition) on the EXT_TRIG/INT2 pin. Once the measurement cycle has completed, FXLS8964AF automatically transitions back to the EXT_TRIG state and waits for the next trigger event.</p> <p><b>BT_MODE = V<sub>DD</sub>:</b></p> <p>External trigger mode is not available; <b>SENS_CONFIG4 [INT2_FUNC]</b> shall not be written to with any value other than 0.</p>                                                                                                                                                                                                                                                                                                                      |

- [1] All register contents are preserved when transitioning from Active to Standby mode. Some registers are reset when transitioning from Standby to Active. The behavior of all registers is noted in [Table 20](#).

- [2] Exiting Hibernate mode causes all register settings to initialize to their default values. Entering Hibernate mode is equivalent to removing the V<sub>DD</sub> supply; the device state, sensor data, and host programmed register contents are lost when this mode is entered.

- [3] The SLEEP and WAKE modes are Active measurement modes. For more information on how to use the SLEEP and WAKE modes and how to transition between these modes, see [Table 16](#).

- [4] The SLEEP and WAKE modes each feature independent power mode and ODR settings for the HPM and LPM modes. FPM may also be independently enabled for either WAKE or SLEEP modes, allowing for user programmable idle times and measurement decimation factors. These features allow for the creation of custom ODRs and also realizing the optimal trade-off between resolution (noise) and power dissipation in a given application or use case.

- [5] The EXT\_TRIG mode may be used to synchronize the collection of acceleration and temperature data with an external system, or to create custom ODRs using an MCU output compare/PWM/GPIO pin.

**Figure 14. Operating modes transition diagram**

Table 16. Operating modes transition criteria

| Callout | Current mode | Next mode | Transition criteria                                                                                                                                                                                                                                                                                                                                                                                                                       |