## DESCRIPTION

The MP5098 is a 12V/5V, low quiescent current ( $I_Q$ ), low on resistance ( $R_{DS(ON)}$ ), dual-channel e-fuse protection device with current monitoring. It protects output circuitry from input transients, as well as protects input circuitry from output shorts and transients.

At start-up, the inrush current is limited by limiting the output slew rate. The slew rate is controlled via the SS pin capacitor ( $C_{SS}$ ).

The maximum load current ( $I_{LOAD\_MAX}$ ) at the output is current-limited. The magnitude of the current limit ( $I_{LIMIT}$ ) is fixed internally.

Full protection features include output over-voltage protection (OVP), over-current protection (OCP), short-circuit protection (SCP), and thermal shutdown.

The output voltage ( $V_{OUT}$ ) is limited by output OVP. Each rail's output current ( $I_{OUT}$ ) can be monitored via a resistor connected between the IMON1 and IMON2 pins.

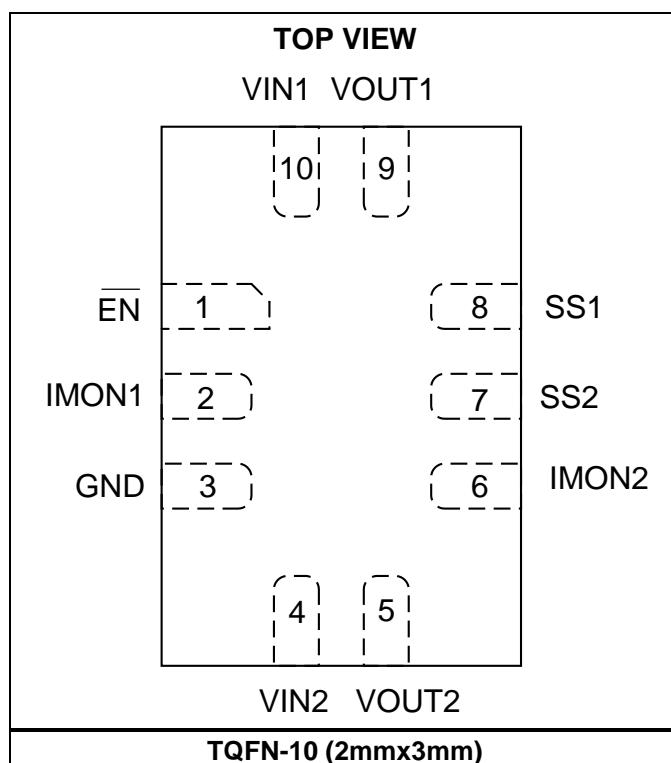

The MP5098 is available in a space-saving TQFN-10 (2mmx3mm) package.

## FEATURES

- 12V/5V Integrated Dual E-Fuse

- Dual-Channel Current Limiting

- 24V/100ms Maximum Surge Input Voltage ( $V_{IN}$ ) Tolerance for 12V Bus and 5V Bus

- 40mΩ Low On Resistance ( $R_{DS(ON)}$ )

- Low Quiescent Current ( $I_Q$ ):

- 210µA  $I_Q$  for 12V Bus

- 190µA  $I_Q$  for 15V Bus

- Configurable Soft-Start Time ( $t_{SS}$ )

- Fixed Trip/Hold Current Limit ( $I_{LIMIT}$ ):

- Fixed 4A Trip  $I_{LIMIT}$  for 12V Bus

- Fixed 2.5A Hold  $I_{LIMIT}$  for 12V Bus

- Fixed 3A Trip  $I_{LIMIT}$  for 5V Bus

- Fixed 1.3A Hold  $I_{LIMIT}$  for 5V Bus

- 15V Over-Voltage Protection (OVP) Threshold for 12V  $V_{IN}$  Channel

- 5.7V OVP Threshold for 5V  $V_{IN}$  Channel

- Over-Current Protection (OCP) with Hiccup Mode

- Short-Circuit Protection (SCP)

- Thermal Shutdown (Latch-Off Protection)

- Available in a TQFN-10 (2mmx3mm) Package

## APPLICATIONS

- Hard-Disk Drives (HDDs)

- Solid-State Drives (SSDs)

- Hot Swap Applications

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

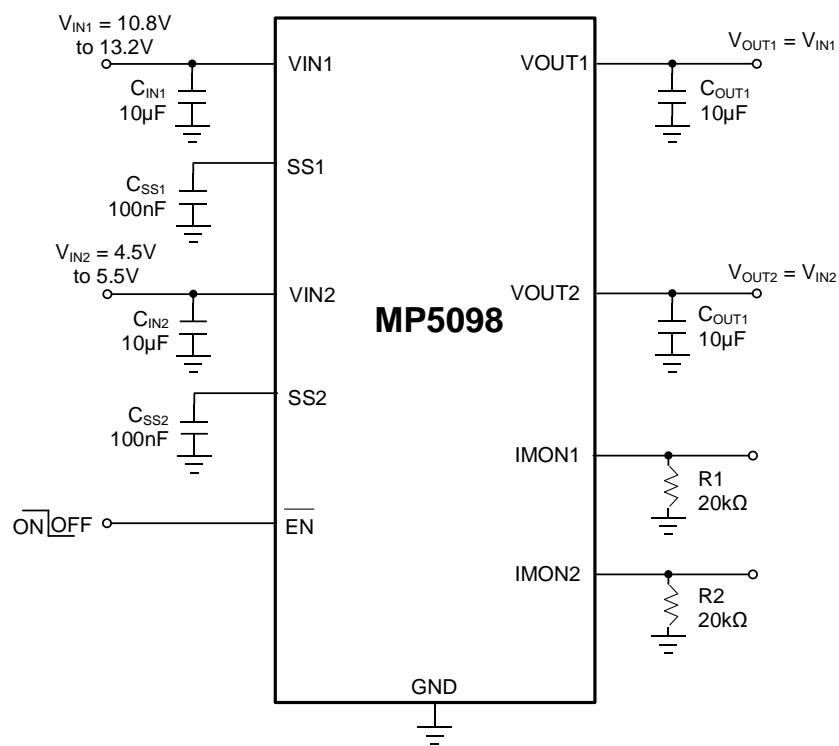

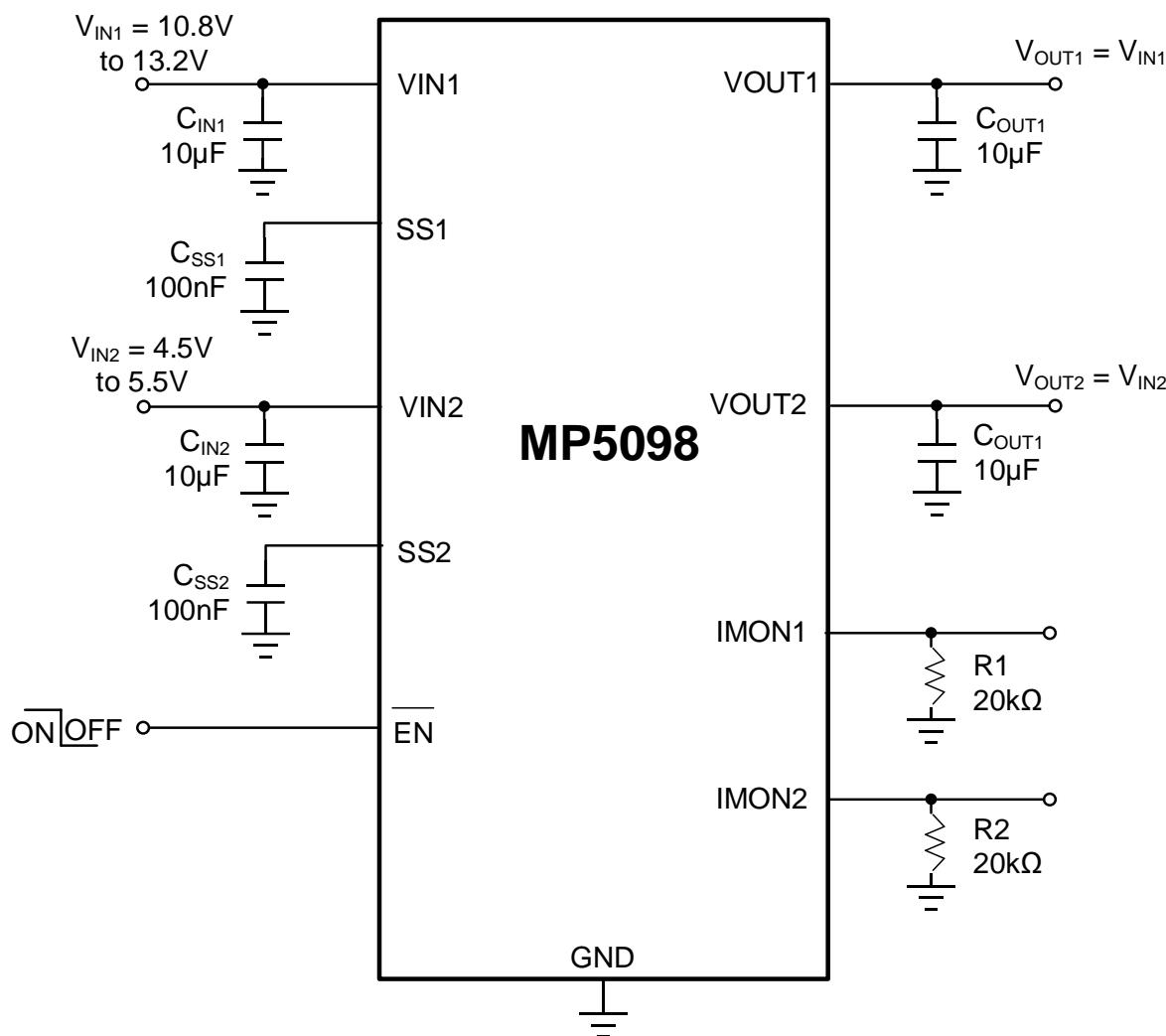

## TYPICAL APPLICATION

## ORDERING INFORMATION

| Part Number* | Package           | Top Marking | MSL Rating |

|--------------|-------------------|-------------|------------|

| MP5098GDT    | TQFN-10 (2mmx3mm) | See Below   | 1          |

\* For Tape & Reel, add suffix -Z (e.g. MP5098GDT-Z).

## TOP MARKING

BLB

YWW

LLL

BLB: Product code of MP5098GDT

Y: Year code

WW: Week code

www.weakseas

111 : lot number

## PACKAGE REFERENCE

## PIN FUNCTIONS

| Pin # | Name  | Description                                                                                                                                                                               |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | EN    | <b>Channel 1 and channel 2 enable.</b> The EN pin is a digital input that turns the regulator on and off. Float EN or pull EN low to turn the regulator on; pull EN high to turn it off.  |

| 2     | IMON1 | <b>Channel 1 current monitoring.</b> Connect a resistor between the IMON1 and GND pins to set the current monitor gain.                                                                   |

| 3     | GND   | <b>System ground.</b>                                                                                                                                                                     |

| 4     | VIN2  | <b>Channel 2 supply voltage.</b> Channel 2's typical input voltage ( $V_{IN}$ ) is 5V. Use a ceramic decoupling capacitor to decouple the VIN2 pin. Connect VIN2 using a wide PCB trace.  |

| 5     | VOUT2 | <b>Channel 2 output terminal.</b>                                                                                                                                                         |

| 6     | IMON2 | <b>Channel 2 current monitoring.</b> Connect a resistor between the IMON2 and GND pins to set the current monitor gain.                                                                   |

| 7     | SS2   | <b>Channel 2 soft start.</b> Connect a capacitor between the SS2 and GND pins to set channel 2's soft-start time (tss).                                                                   |

| 8     | SS1   | <b>Channel 1 soft start.</b> Connect a capacitor between the SS1 and GND pins to set channel 1's tss.                                                                                     |

| 9     | VOUT1 | <b>Channel 1 output terminal.</b>                                                                                                                                                         |

| 10    | VIN1  | <b>Channel 1 supply voltage.</b> Channel 2's typical input voltage ( $V_{IN}$ ) is 12V. Use a ceramic decoupling capacitor to decouple the VIN1 pin. Connect VIN1 using a wide PCB trace. |

ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup>

|                                                                       |                 |

|-----------------------------------------------------------------------|-----------------|

| $V_{IN1}, V_{OUT1}$ .....                                             | -0.3V to +22V   |

| Input positive transient (CH1 = 100ms) .....                          | 24V             |

| $V_{IN2}, V_{OUT2}$ .....                                             | -0.3V to +15V   |

| Input positive transient (CH2 = 100ms) .....                          | 24V             |

| All other pins .....                                                  | -0.3V to +5V    |

| Junction temperature .....                                            | -40°C to +150°C |

| Lead temperature .....                                                | 260°C           |

| Continuous Power Dissipation ( $T_A = 25^\circ C$ ) <sup>(2)(4)</sup> |                 |

| TQFN-10 (2mmx3mm) .....                                               | 3.1W            |

## ESD Ratings

|                                  |       |

|----------------------------------|-------|

| Human body model (HBM) .....     | 2000V |

| Charged device model (CDM) ..... | 1750V |

Recommended Operating Conditions <sup>(3)</sup>

|                                        |                 |

|----------------------------------------|-----------------|

| CH1 continuous voltage .....           | 10.8V to 13.8V  |

| CH2 continuous voltage .....           | 4.6V to 5.5V    |

| Operating junction temp ( $T_J$ ) .... | -40°C to +125°C |

**Thermal Resistance**  $\theta_{JA}$   $\theta_{JC}$

|                             |              |

|-----------------------------|--------------|

| TQFN-10 (2mmx3mm)           |              |

| EV5098-D-00A <sup>(4)</sup> | 40 .... °C/W |

| JESD51-7 <sup>(5)</sup>     | 70 .... °C/W |

## Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX) -  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, which may cause the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on the EV5098-D-00A, 2-layer PCB, 54mmx46mm.

- 5) The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

## ELECTRICAL CHARACTERISTICS

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $C_{OUT1} = C_{OUT2} = 10\mu F$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  <sup>(6)</sup>, typical values are tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                                        | Symbol                              | Condition                                                                                    | Min  | Typ  | Max  | Units     |

|----------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|-----------|

| <b>Supply Current</b>                                                            |                                     |                                                                                              |      |      |      |           |

| Quiescent current                                                                | $I_{Q\_CH1}$                        | $V_{EN}$ is low                                                                              |      | 210  |      | $\mu A$   |

|                                                                                  | $I_{Q\_CH2}$                        | $V_{EN}$ is low                                                                              |      | 190  |      | $\mu A$   |

| Shutdown current                                                                 | $I_{SD\_CH1}$                       | $V_{EN}$ is high                                                                             |      | 15   |      | $\mu A$   |

|                                                                                  | $I_{SD\_CH2}$                       | $V_{EN}$ is high                                                                             |      | 10   |      | $\mu A$   |

| <b>Power MOSFET</b>                                                              |                                     |                                                                                              |      |      |      |           |

| On resistance                                                                    | $R_{DS(ON)\_CH1}$                   | $T_J = 25^{\circ}C$                                                                          |      | 40   | 50   | $m\Omega$ |

|                                                                                  |                                     | $T_J = 125^{\circ}C$                                                                         |      |      | 65   | $m\Omega$ |

|                                                                                  | $R_{DS(ON)\_CH2}$                   | $T_J = 25^{\circ}C$                                                                          |      | 40   | 50   | $m\Omega$ |

|                                                                                  |                                     | $T_J = 125^{\circ}C$                                                                         |      |      | 65   | $m\Omega$ |

| Start-up delay                                                                   | $t_{EN\_DELAY\_CH1}$                | From $V_{EN}$ is low to $I_{OUT1}$ rises up to 100mA, with 1A load resistor, SS1 is floating |      | 220  |      | $\mu s$   |

|                                                                                  | $t_{EN\_DELAY\_CH2}$                | From $V_{EN}$ is low to $I_{OUT2}$ rises up to 100mA, with 1A load resistor, SS2 is floating |      | 220  |      | $\mu s$   |

| <b>Under-Voltage Lockout (UVLO) Protection and Over-Voltage Protection (OVP)</b> |                                     |                                                                                              |      |      |      |           |

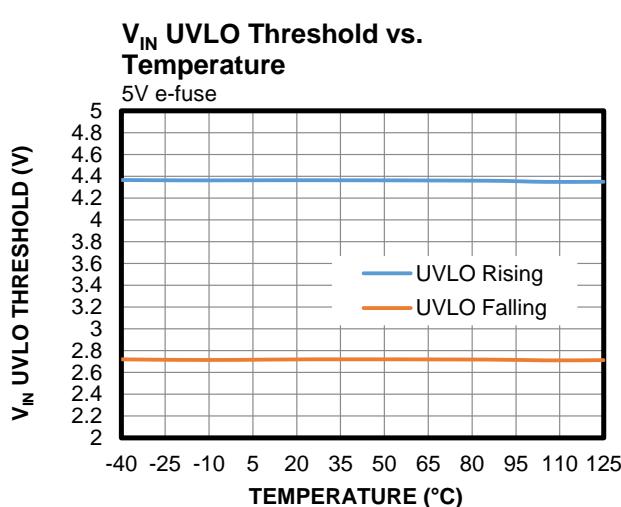

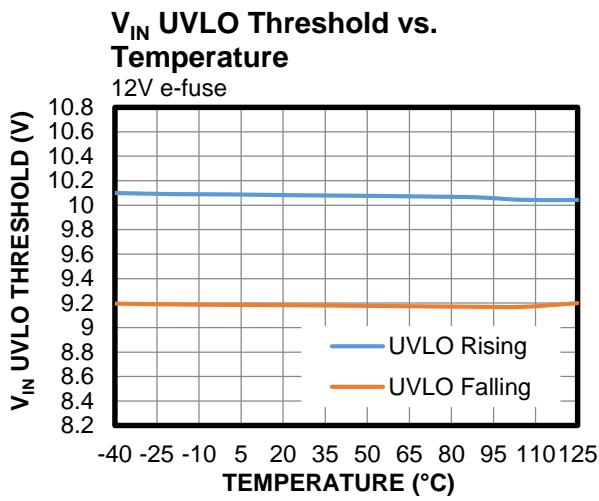

| UVLO rising threshold                                                            | $V_{UVLO\_RISING\_CH1}$             |                                                                                              | 9.6  | 10   | 10.4 | V         |

|                                                                                  | $V_{UVLO\_RISING\_CH2}$             |                                                                                              | 4.25 | 4.35 | 4.45 | V         |

| UVLO falling threshold                                                           | $V_{UVLO\_FALLING\_CH1}$            |                                                                                              |      | 9.1  |      | V         |

|                                                                                  | $V_{UVLO\_FALLING\_CH2}$            |                                                                                              |      | 2.65 |      | V         |

| Output OVP threshold                                                             | $V_{OVP\_CH1}$                      |                                                                                              | 13.8 | 15   | 16   | V         |

|                                                                                  | $V_{OVP\_CH2}$                      |                                                                                              | 5.5  | 5.7  | 5.9  | V         |

| Output OVP response time <sup>(7)</sup>                                          | $t_{OVP\_CH1}$                      | $C_{OUT1} = 10\mu F$ with $30\Omega$ load resistor, $V_{IN1} = 12V$ to $18V/10\mu s$         |      | 2    |      | $\mu s$   |

|                                                                                  | $t_{OVP\_CH2}$                      | $C_{OUT2} = 10\mu F$ with $10\Omega$ load resistor, $V_{IN2} = 5V$ to $7V/10\mu s$           |      | 2    |      | $\mu s$   |

| <b>Current Limit (<math>I_{LIMIT}</math>)</b>                                    |                                     |                                                                                              |      |      |      |           |

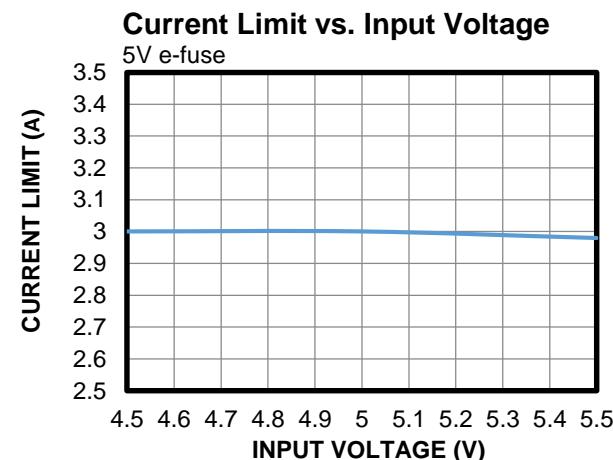

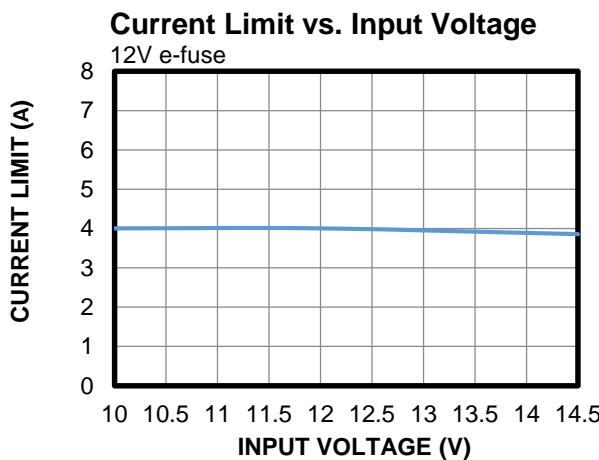

| $I_{LIMIT}$ during normal operation                                              | $I_{LIMIT\_CH1}$                    |                                                                                              | -10% | 4    | +10% | A         |

|                                                                                  | $I_{LIMIT\_CH2}$                    |                                                                                              | -10% | 3    | +10% | A         |

| Constant-current limit during normal operation                                   | $I_{LIMIT\_CC\_CH1}$ <sup>(7)</sup> |                                                                                              |      | 2.5  |      | A         |

|                                                                                  | $I_{LIMIT\_CC\_CH2}$ <sup>(7)</sup> |                                                                                              |      | 1.3  |      | A         |

| $I_{LIMIT}$ response time <sup>(7)</sup>                                         | $t_{CL\_CH1}$                       |                                                                                              |      | 15   |      | $\mu s$   |

|                                                                                  | $t_{CL\_CH2}$                       |                                                                                              |      | 15   |      | $\mu s$   |

| Secondary $I_{LIMIT}$ <sup>(7)</sup>                                             | $I_{LIMIT\_SEC\_CC\_CH1}$           |                                                                                              |      | 8    |      | A         |

|                                                                                  | $I_{LIMIT\_SEC\_CC\_CH2}$           |                                                                                              |      | 8    |      | A         |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $C_{OUT1} = C_{OUT2} = 10\mu F$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  <sup>(6)</sup>, typical values are tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                    | Symbol            | Condition | Min  | Typ  | Max  | Units       |

|----------------------------------------------|-------------------|-----------|------|------|------|-------------|

| Hiccup mode on time                          | $t_{ON\_HICCUP}$  |           |      | 2    |      | ms          |

| Hiccup mode off time                         | $t_{OFF\_HICCUP}$ |           |      | 200  |      | ms          |

| <b>Current Monitoring (IMON1/IMON2)</b>      |                   |           |      |      |      |             |

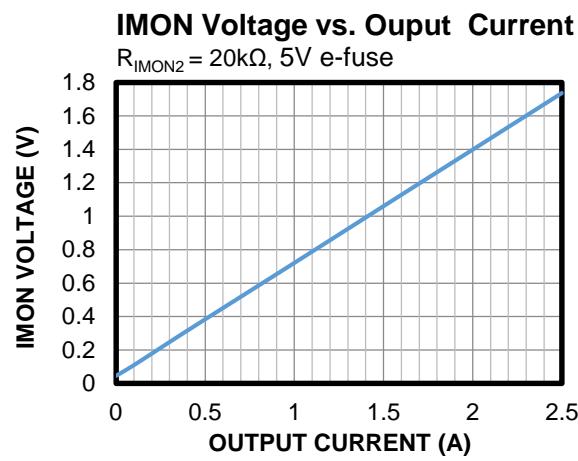

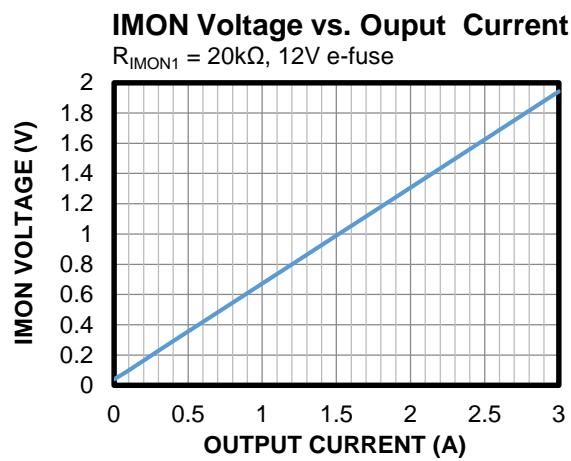

| Current-sense gain                           | $G_{IMON1}$       |           |      | 32   |      | $\mu A/A$   |

|                                              | $G_{IMON2}$       |           |      | 34   |      | $\mu A/A$   |

| Current-sense offset                         | $I_{OFFSET\_CH1}$ |           | 0.45 | 2    | 3.5  | $\mu A$     |

|                                              | $I_{OFFSET\_CH2}$ |           | 0.8  | 2.3  | 3.8  | $\mu A$     |

| Current monitor voltage range <sup>(7)</sup> | $V_{IMON}$        |           | 0    |      | 2.5  | V           |

| <b>Enable (EN) Control</b>                   |                   |           |      |      |      |             |

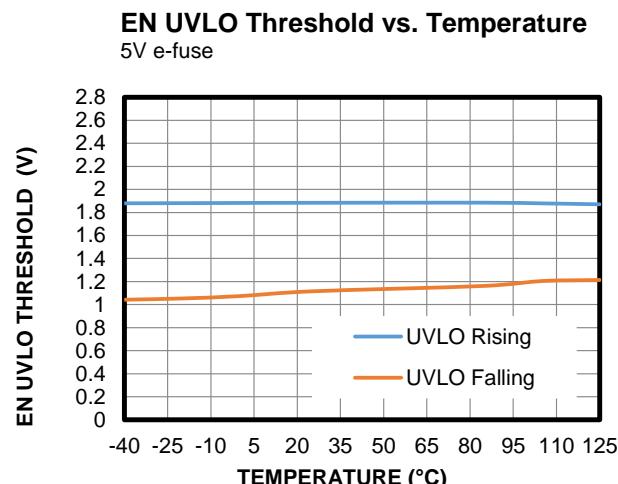

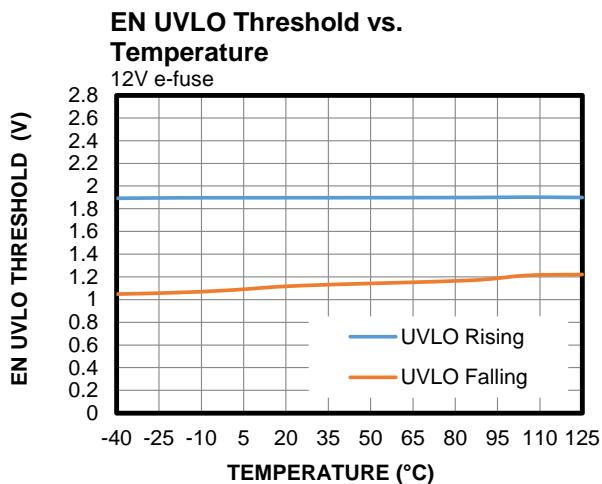

| EN falling threshold                         | $V_{EN\_FALLING}$ |           | 0.95 | 1.15 | 1.35 | V           |

| EN hysteresis                                | $V_{EN\_HYS}$     |           |      | 800  |      | mV          |

| EN pull down resistance                      | $R_{EN\_PD}$      |           |      | 0.77 |      | $M\Omega$   |

| <b>Soft Start (SS)</b>                       |                   |           |      |      |      |             |

| Soft-start current                           | $I_{SS\_CH1}$     |           | 4    | 5.5  | 7    | $\mu A$     |

|                                              | $I_{SS\_CH2}$     |           | 4    | 5.5  | 7    | $\mu A$     |

| <b>Thermal Shutdown</b>                      |                   |           |      |      |      |             |

| Thermal shutdown <sup>(7)</sup>              | $T_{SD}$          |           |      | 155  |      | $^{\circ}C$ |

### Notes:

6) Guaranteed by over-temperature correlation. Not tested in production.

7) Guaranteed by engineering sample characterization.

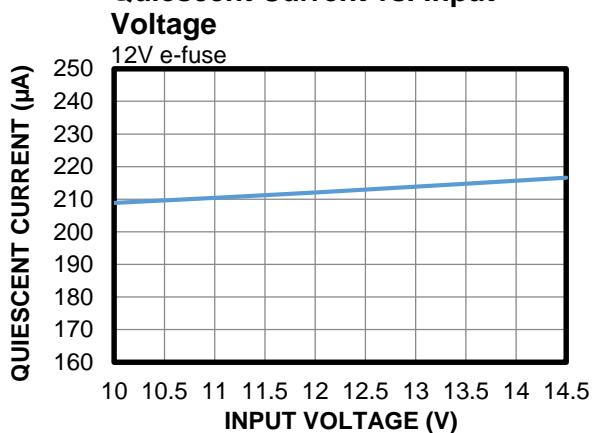

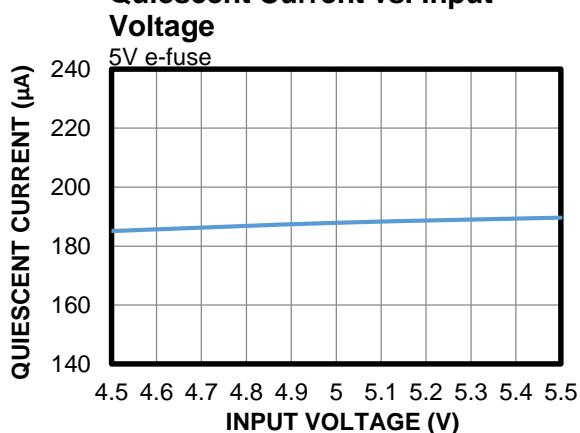

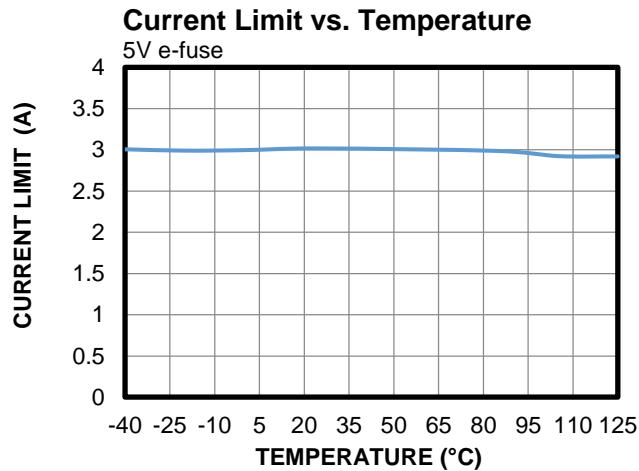

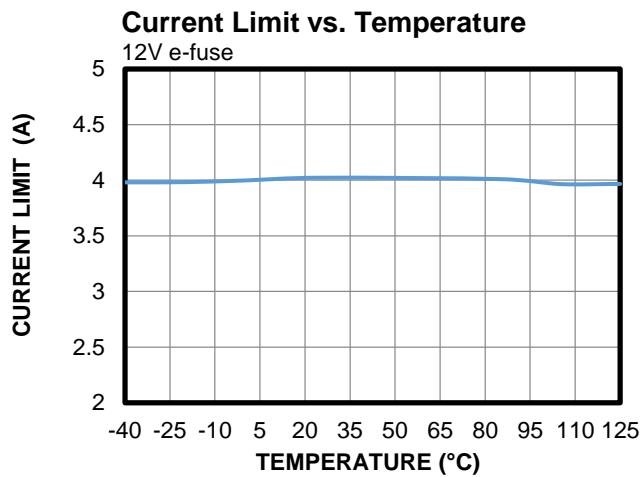

## TYPICAL CHARACTERISTICS

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

Quiescent Current vs. Input Voltage

Quiescent Current vs. Input Voltage

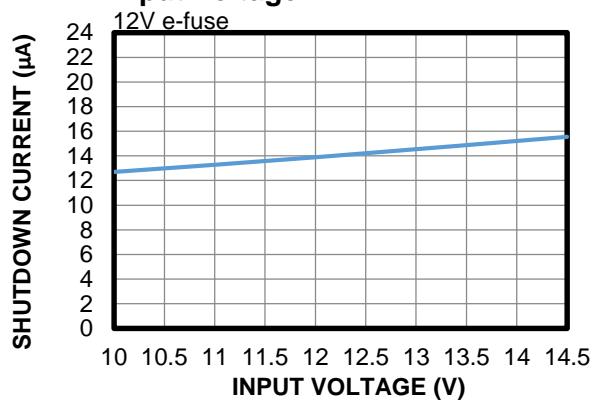

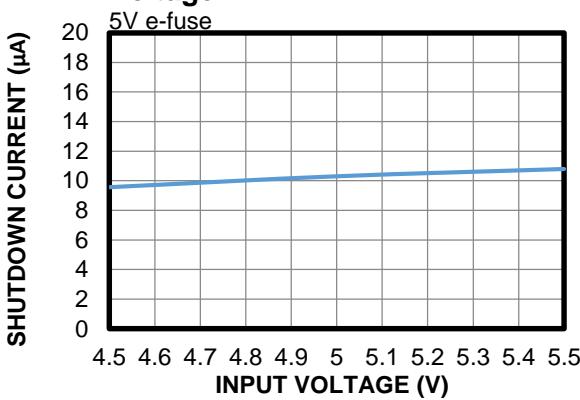

Shutdown Current vs. Input Voltage

Shutdown Current vs. Input Voltage

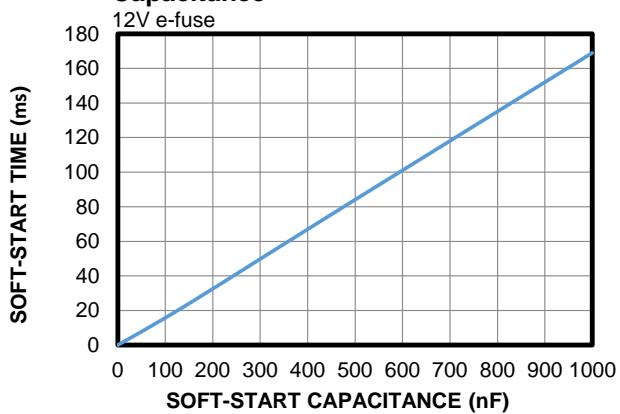

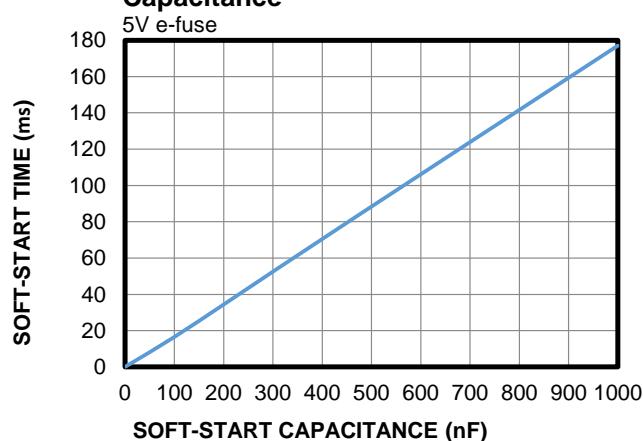

Soft-Start Time vs. Soft-Start Capacitance

Soft-Start Time vs. Soft-Start Capacitance

## TYPICAL CHARACTERISTICS (continued)

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

## TYPICAL CHARACTERISTICS (continued)

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

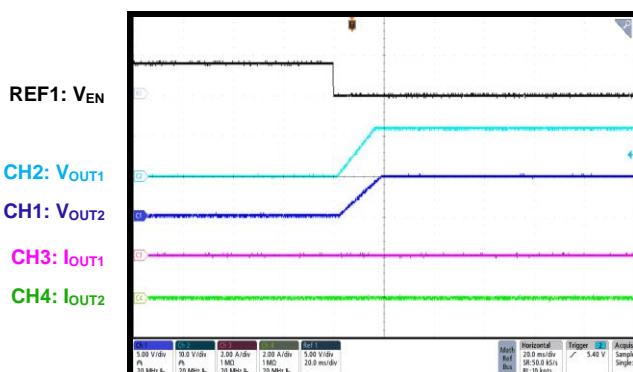

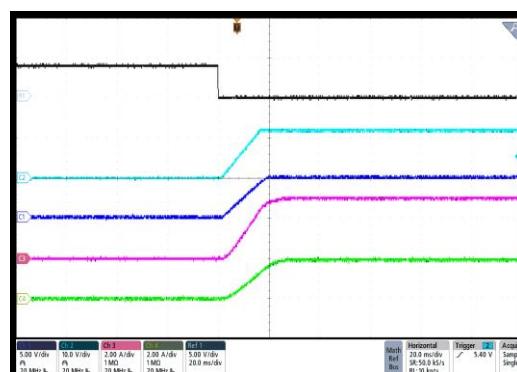

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

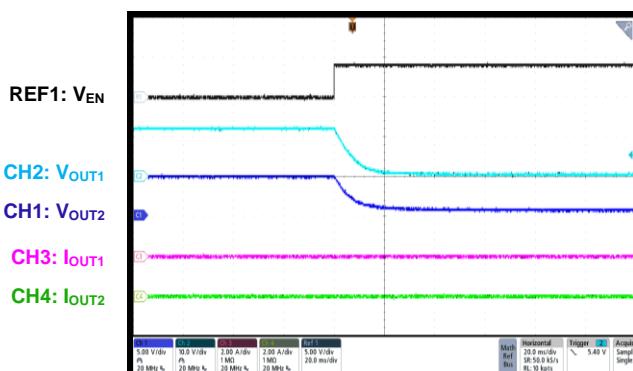

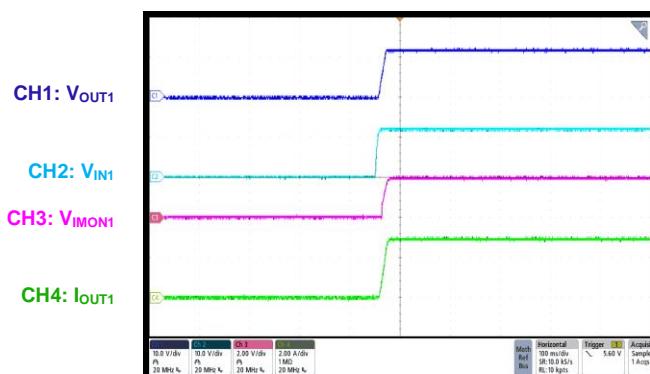

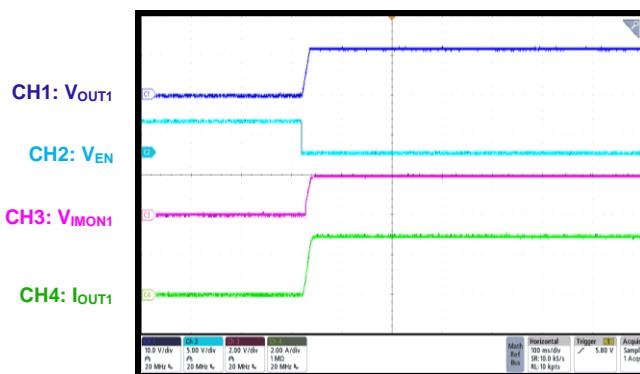

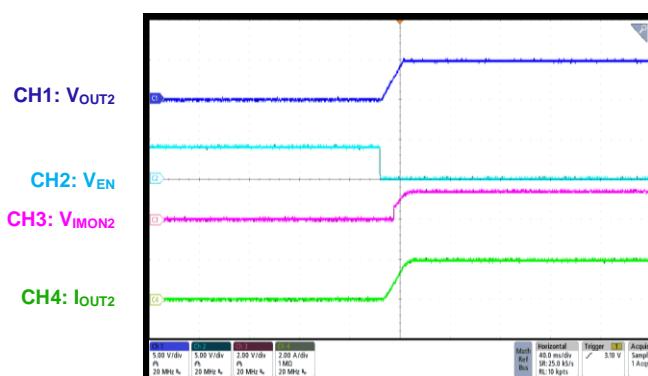

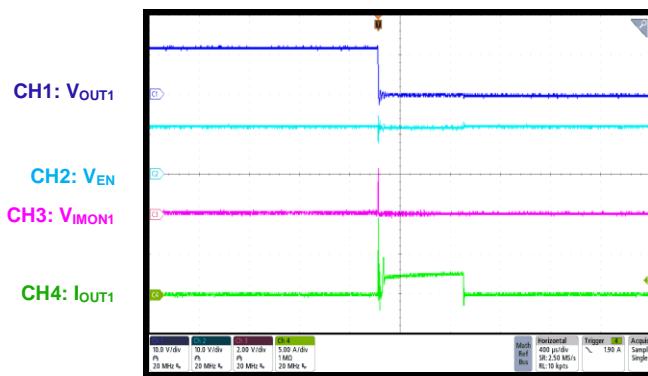

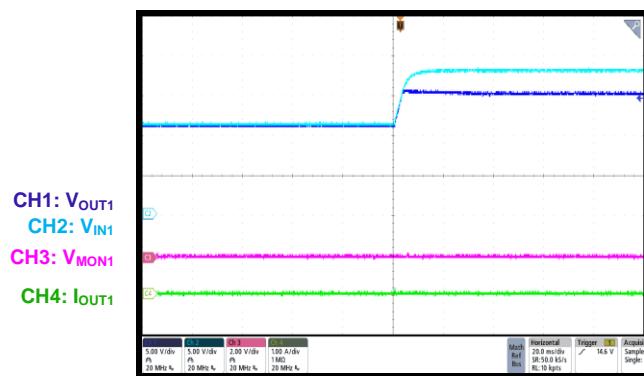

### CH1/CH2 Start-Up through EN

$I_{OUT1} = I_{OUT2} = 0A$

### CH1/CH2 Start-Up through EN

$I_{OUT1} = 3A$ ,  $I_{OUT2} = 2A$

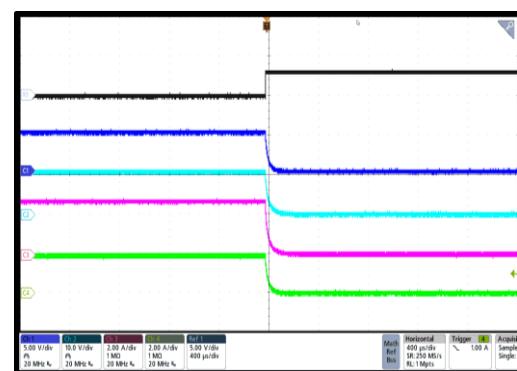

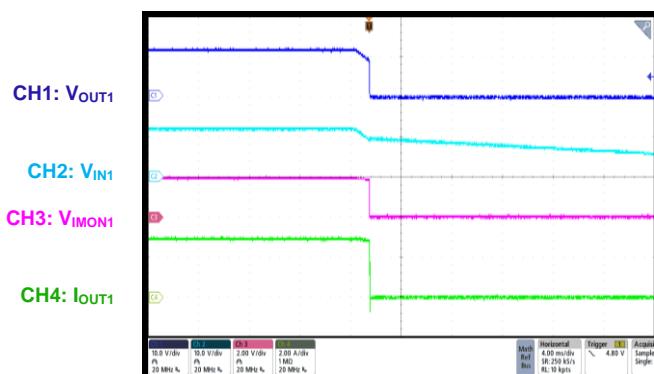

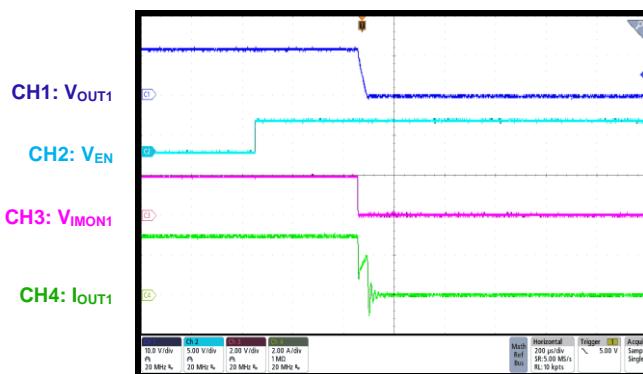

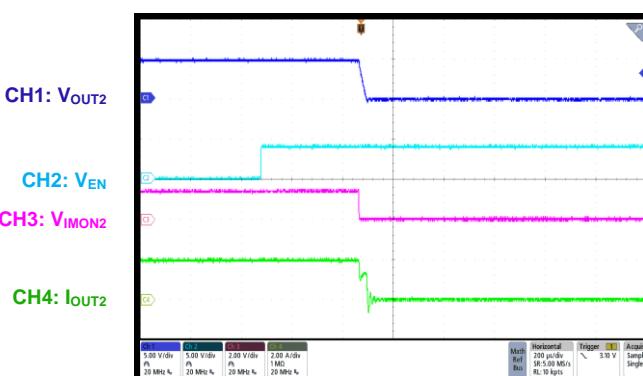

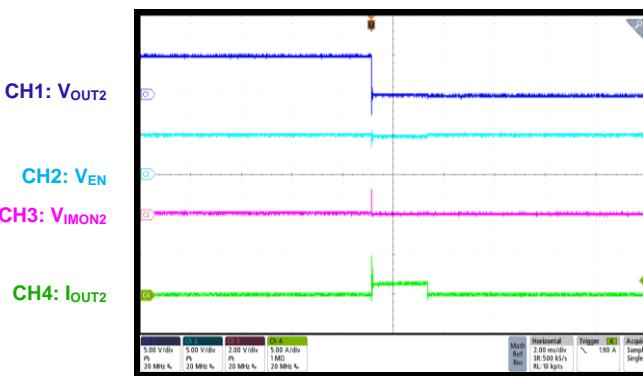

### CH1/CH2 Shutdown through EN

$I_{OUT1} = I_{OUT2} = 0A$

### CH1/CH2 Shutdown through EN

$I_{OUT1} = 3A$ ,  $I_{OUT2} = 2A$

### Start-Up through VIN1

12V e-fuse, no load

### Shutdown through VIN1

12V e-fuse, no load

**TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

**Start-Up through VIN1**

12V e-fuse, 3A load

**Shutdown through VIN1**

12V e-fuse, 3A load

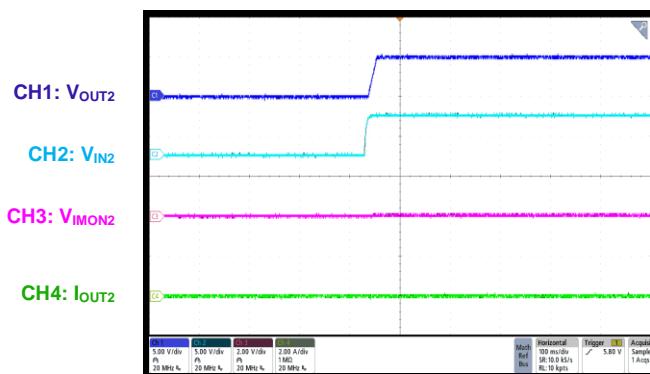

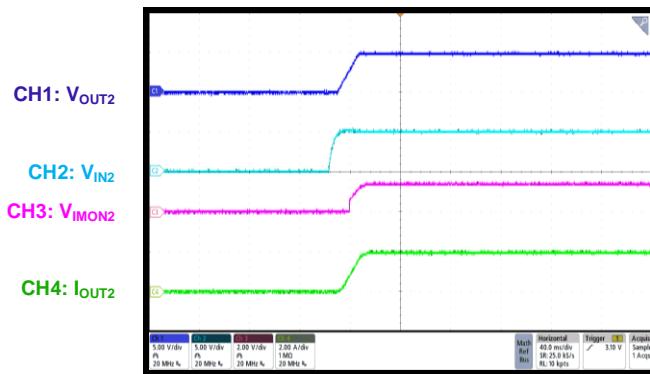

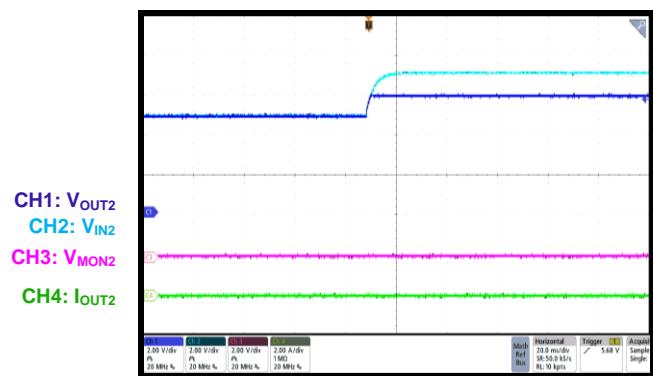

**Start-Up through VIN2**

5V e-fuse, no load

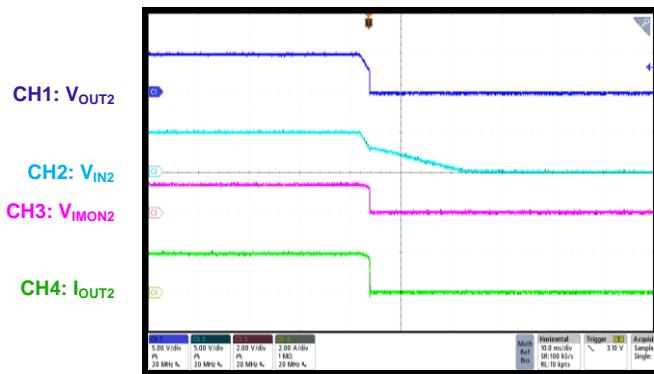

**Shutdown through VIN2**

5V e-fuse, no load

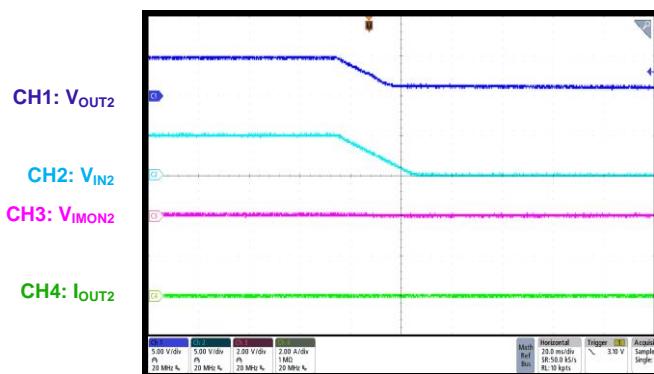

**Start-Up through VIN2**

5V e-fuse, 2A load

**Shutdown through VIN2**

5V e-fuse, 2A load

**TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

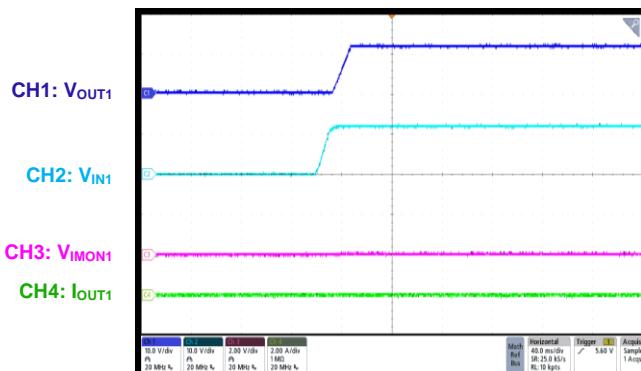

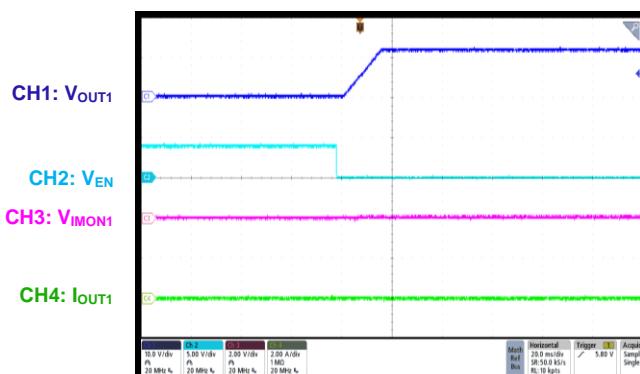

**Start-Up through EN**

12V e-fuse, no load

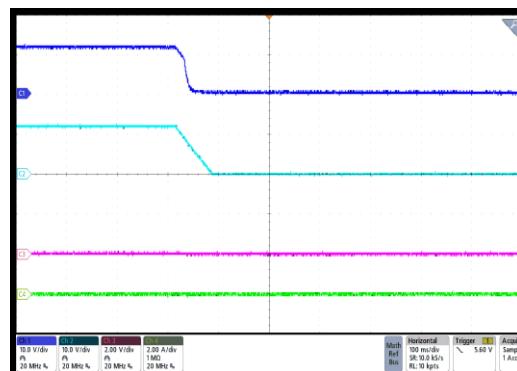

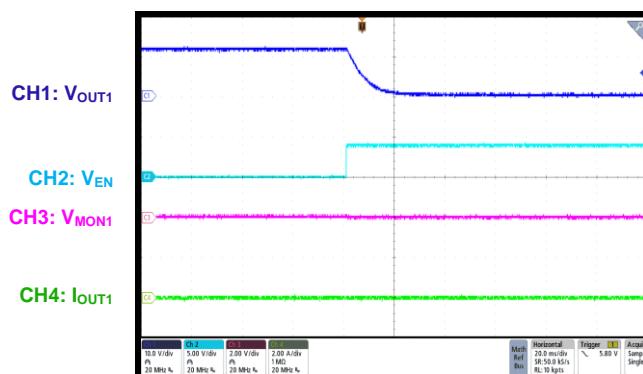

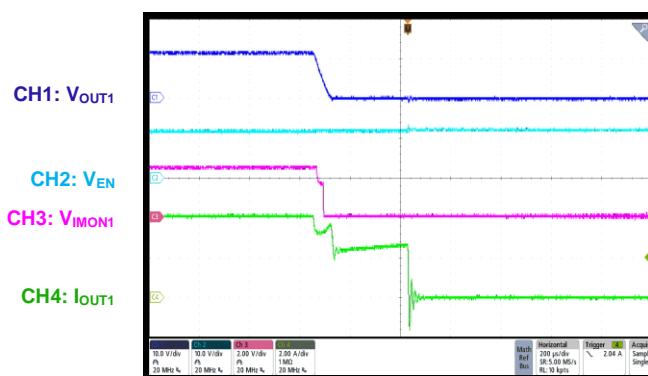

**Shutdown through EN**

12V e-fuse, no load

**Start-Up through EN**

12V e-fuse, 3A load

**Shutdown through EN**

12V e-fuse, 3A load

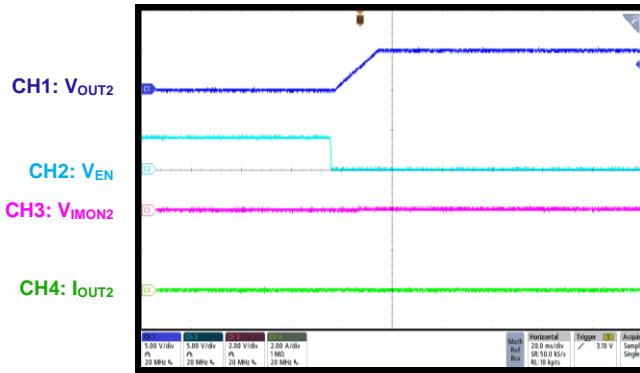

**Start-Up through EN**

5V e-fuse, no load

**Shutdown through EN**

5V e-fuse, no load

**TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

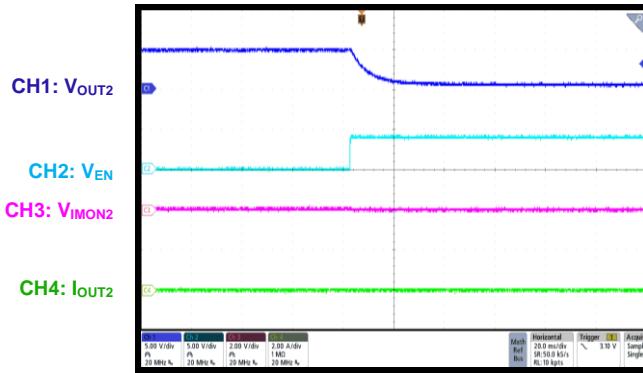

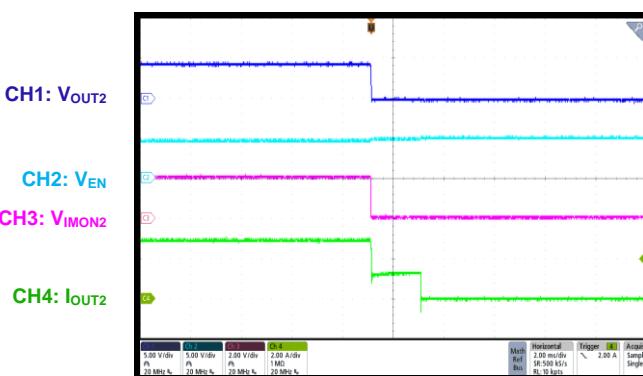

**Start-Up through EN**

5V e-fuse, 2A load

**Shutdown through EN**

5V e-fuse, 2A load

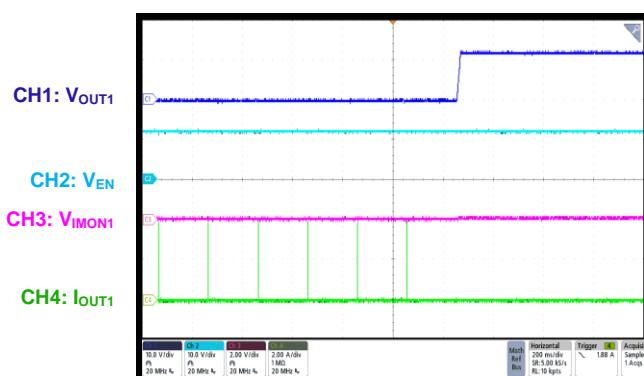

**Current Limit**

12V e-fuse, IOUT increases slowly

**Current Limit**

5V e-fuse, IOUT increases slowly

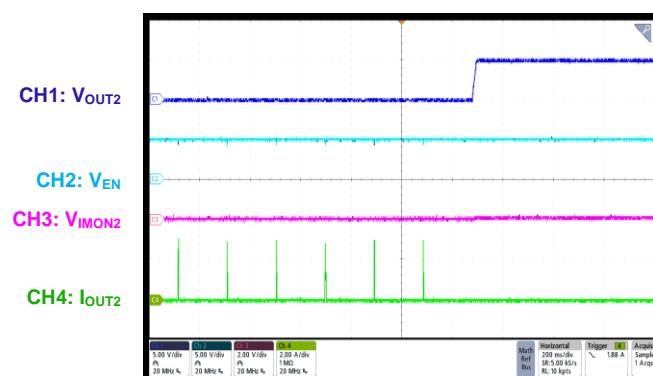

**SCP Entry**

12V e-fuse

**SCP Entry**

5V e-fuse

**TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN1} = 12V$ ,  $V_{IN2} = 5V$ ,  $T_A = 25^\circ C$ , unless otherwise noted.

**SCP Recovery**

12V e-fuse

**SCP Recovery**

5V e-fuse

**Output OVP**

12V e-fuse,  $V_{IN1} = 12V$  to 18V

**Output OVP**

5V e-fuse,  $V_{IN2} = 5V$  to 7V

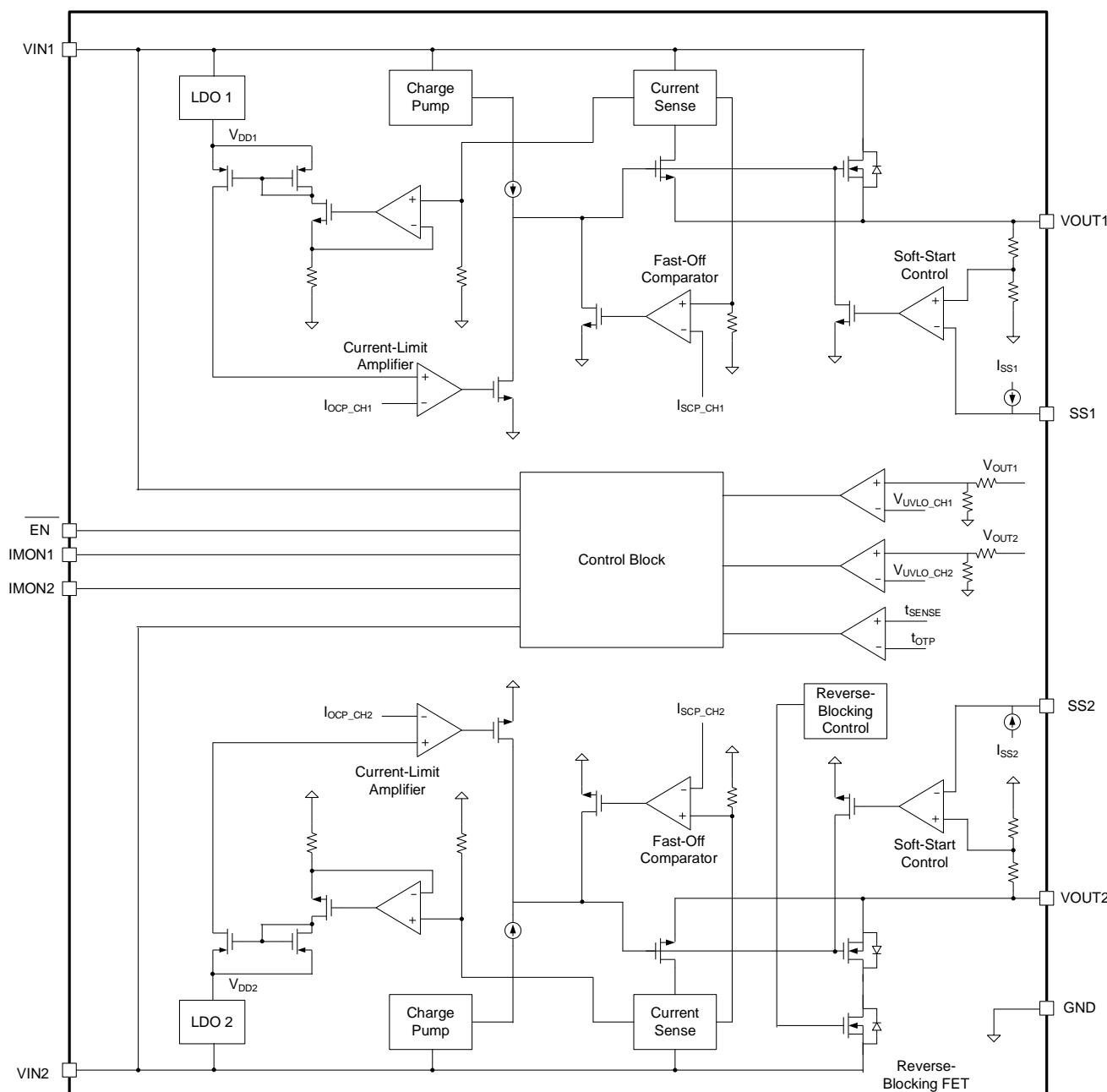

## FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## OPERATION

The MP5098 is a 12V/5V, dual-channel e-fuse with current limiting. It is designed to limit the inrush current to the load while a circuit card is inserted into a live backplane power source. This limits the backplane's voltage drop and the dV/dt to the load. The MP5098 offers an integrated solution that can monitor the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), output current ( $I_{OUT}$ ), and die temperature. This eliminates the need for an external current-sense resistor, power MOSFET, and thermal-sensing device.

### Under-Voltage Lockout (UVLO) Protection

Channel 1 can be used in the 12V system, and channel 2 can be used in the 5V system. High energy transients can occur during normal operation or hot swap. These transients are determined by the wire's parasitic inductance and resistance, as well as the VCC capacitor ( $C_{VCC}$ ). If a power-clamped TVS diode is not used, then the e-fuse should be able to withstand the transient voltage. The MP5098 integrates a high-voltage MOSFET and a high-voltage circuit at VCC to guarantee safe operation.

If  $V_{IN}$  drops below the under-voltage lockout (UVLO) threshold, then the output is disabled. Once  $V_{IN}$  exceeds the UVLO threshold, the output is enabled.

### Soft Start (SS)

Connect a capacitor to the SS pin to set the soft-start time ( $t_{SS}$ ).  $t_{SS}$  is a function of the soft-start capacitor ( $C_{SS}$ ). A constant-current source charges  $C_{SS}$ , and the SS voltage ( $V_{SS}$ ) ramps up.  $V_{OUT}$  ramps up at a similar slew rate to  $V_{SS}$ .

$t_{SS}$  can be calculated with Equation (1):

$$t_{DV/DT}(\text{ms}) = \frac{1V \times C_{SS}(\text{nF})}{I_{SS}} \quad (1)$$

Where  $t_{DV/DT}$  is  $t_{SS}$  between 0% and 100% of  $V_{OUT}$ , and  $I_{SS}$  is the soft-start current.

### Output Over-Voltage Protection (OVP)

The MP5098 provides output over-voltage protection (OVP) to protect the downstream load from surge voltages at the input. An accurate, fast comparator monitors  $V_{OUT}$ . If  $V_{OUT}$

exceeds the OVP threshold, then the gate voltage ( $V_{GATE}$ ) of the internal MOSFETs is pulled down.  $V_{GATE}$  is regulated at a certain value to keep  $V_{OUT}$  clamped at the OVP threshold. Fast loop response speed (typically 2 $\mu$ s) reduces the over-voltage (OV) overshoot.

### Over-Current Protection (OCP)

If an over-current (OC) fault occurs (e.g. the load exceeds the current limit [ $I_{LIMIT\_CHx}$ ] or a short occurs), then over-current protection (OCP) is triggered and the part enters constant-current mode. If the OC condition remains after 150 $\mu$ s, then the part enters hiccup mode and shuts down. After a 200ms off time ( $t_{OFF}$ ), the part starts up again. The MP5098 repeats this operation until the OC condition has been removed.

Channel 1's current limit ( $I_{LIMIT\_CH1}$ ) is set at 4A internally, and its constant-current limit ( $I_{LIMIT\_CC\_CH1}$ ) is set at 2.5A. Channel 2's current limit ( $I_{LIMIT\_CH2}$ ) is set at 3A internally, and its constant-current limit ( $I_{LIMIT\_CC\_CH2}$ ) is set at 1.3A.

### Current Monitoring

The MP5098 provides current monitoring for both channel 1 and channel 2. The IMONx pin generates a current proportional to channel 1 and channel 2's load current ( $I_{LOAD\_CHx}$ ). Connect a resistor to IMONx to generate the current monitor voltage ( $V_{IMONx}$ ). The effective  $V_{IMONx}$  range is between 0V and 2.5V to guarantee that the sensing results are linear.  $V_{IMONx}$  can be calculated with Equation (2):

$$V_{IMONx}(\text{mV}) = G_{IMONx} \times I_{OUT}(\text{A}) \times R_{IMONx}(\text{k}\Omega) + I_{OFFSET\_CHx} \times R_{IMONx}(\text{k}\Omega) \quad (2)$$

Where  $G_{IMON\_CHx}$  is the current-sense gain,  $R_{IMON\_CHx}$  is the current-sense resistor, and  $I_{OFFSET\_CHx}$  is the current-sense offset.

### Short Circuit Protection (SCP)

If the  $I_{LOAD\_CHx}$  increases rapidly due to a short circuit, the current may exceed  $I_{LIMIT\_CHx}$  before the control loop can respond. If the current reaches the secondary  $I_{LIMIT}$  level (8A), then short-circuit protection (SCP) is triggered and the fast turn-off circuit turns off the MOSFET (see Figure 1 on page 15). This limits the peak current through the MOSFET to maintain  $V_{IN}$ . The total short-circuit response time is less than

1μs. Once the e-fuse turns off, the part starts up after a delay (200ms). If the short still remains, then  $V_{GATE}$  is regulated to maintain the current at its  $I_{LIMIT}$  level, and the part enters hiccup mode after a 200ms off time ( $t_{OFF}$ ). The MP5098 repeats this operation until the short circuit has been removed.

#### **Enable**

$\overline{EN}$  is a digital control pin that enables and disabled the current-limit MOSFET. Pull  $\overline{EN}$  low

or float  $\overline{EN}$  to turn the current-limit MOSFET on; pull  $\overline{EN}$  high to turn it off. An internal 770kΩ resistor connected between  $\overline{EN}$  and GND allows  $\overline{EN}$  to float to start up the device.

#### **Thermal Shutdown**

Thermal shutdown monitors the silicon die temperature to prevent the chip from operating at exceedingly high temperatures. If the temperature exceeds 155°C, then the part shuts down.

## APPLICATION INFORMATION

### Setting the Soft-Start Time (t<sub>ss</sub>)

The soft-start time (t<sub>ss</sub>) is a function of the soft-start capacitor (C<sub>ss</sub>). t<sub>ss</sub> can be calculated with Equation (3):

$$t_{DV/DT} (\text{ms}) = \frac{1V \times C_{ss} (\text{nF})}{I_{ss}} \quad (3)$$

Where t<sub>DV/DT</sub> is t<sub>ss</sub> between 0% and 100% of V<sub>OUT</sub>.

### Design Example

Table 1 shows a design example following the application guidelines for the specifications.

Table 1: Design Example

|                   |     |

|-------------------|-----|

| V <sub>IN1</sub>  | 12V |

| V <sub>OUT1</sub> | 12V |

| V <sub>IN2</sub>  | 5V  |

| V <sub>OUT2</sub> | 5V  |

Figure 3 on page 19 shows the detailed application schematic. The typical performance and waveforms are shown in the Typical Characteristics section on page 7 and the Typical Performance Characteristics section on page 10. For more device applications, refer to the related evaluation board datasheet.

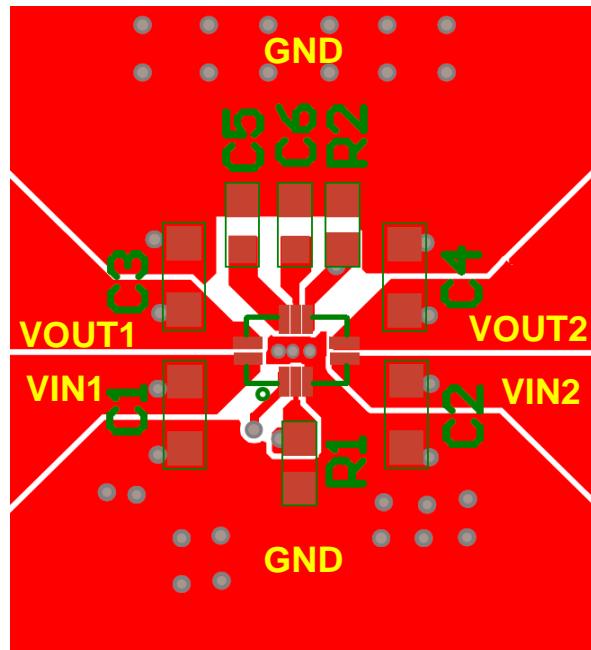

### PCB Layout Guidelines

Efficient PCB layout is critical for stable operation. For best results, refer to Figure 2 and follow the guidelines below:

1. Place the high-current paths (VIN and VOUT) close to the device using short, direct, and wide traces.

2. Place the input capacitors as close to the VIN and GND pins as possible.

3. To improve thermal performance, connect the VIN pad to the large VIN plane, and the VOUT pad to the large VOUT plane.

4. Place C<sub>ss</sub> as close to SS pin as possible.

Figure 2: Recommended PCB Layout

## TYPICAL APPLICATION CIRCUIT

Figure 3: Typical Application Circuit

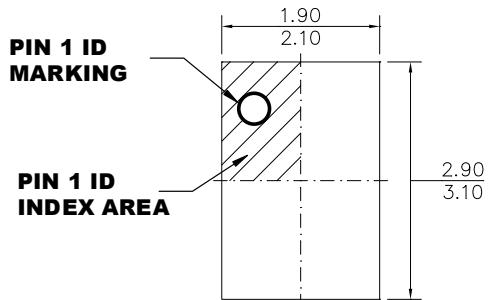

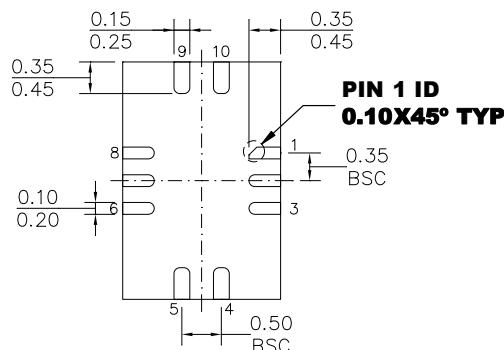

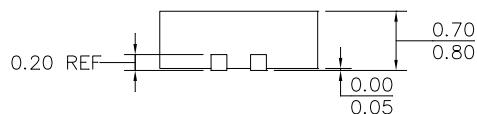

## PACKAGE INFORMATION

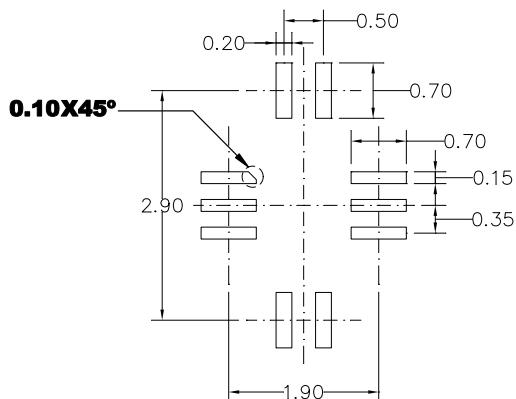

TQFN-10 (2mmx3mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

**RECOMMENDED LAND PATTERN**

**NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) LEAD COPLANARITIES SHALL BE 0.08 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220.

- 4) DRAWING IS NOT TO SCALE.

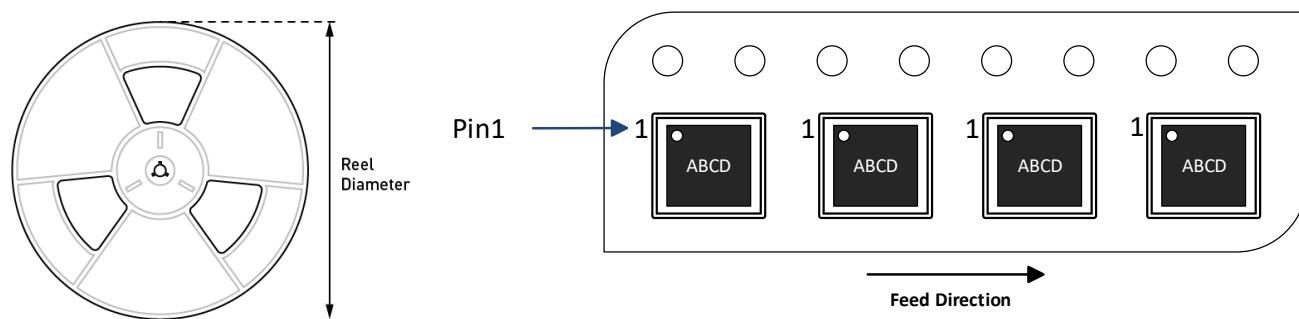

**CARRIER INFORMATION**

| Part Number | Package Description  | Quantity/Reel | Quantity/Tube | Quantity/Tray | Reel Diameter | Carrier Tape Width | Carrier Tape Pitch |

|-------------|----------------------|---------------|---------------|---------------|---------------|--------------------|--------------------|

| MP5098GDT-Z | TQFN-10<br>(2mmx3mm) | 5000          | N/A           | N/A           | 13in          | 12mm               | 8mm                |

**REVISION HISTORY**

| Revision # | Revision Date | Description     | Pages Updated |

|------------|---------------|-----------------|---------------|

| 1.0        | 11/02/2021    | Initial Release | -             |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[Monolithic Power Systems \(MPS\):](#)

[MP5098GDT-P](#) [MP5098GDT-Z](#)