## SAMR30 IEEE® 802.15.4™ Sub-1GHz Module Datasheet

### Introduction

The ATSAMR30M18A is an IEEE® 802.15.4™-2003/2006/2011 compliant RF module for the sub-1GHz ISM bands such as 780 MHz (China), 868 MHz (Europe) and 915 MHz (North America), optimized for low-power applications. This module combines the SAMR30E18A SiP (System in Package), 16 MHz crystal oscillator, discrete balun, lumped element harmonic reject filter and required RF shielding in a compact 12.7mm x 11.0mm design. The module as implemented on the Xplained Pro development board has passed regulatory approvals with chip antenna or SMA connectorized monopole antenna.

This datasheet provides only a brief overview of necessary sections of the module. For a detailed description of each peripheral, refer to the [ATSAMR30E18A datasheet](#).

### Features

- Processor

- ARM® Cortex®-M0+ CPU running at up to 48 MHz

- Single-cycle hardware multiplier

- Micro Trace Buffer (MTB)

- Memories

- 256 KB in-system self-programmable Flash

- 32 KB SRAM

- 8 KB low-power RAM

- System

- Power-on Reset (POR) and Brown-out Detection (BOD)

- Internal clock option with 48 MHz Digital Frequency Locked Loop (DFLL48M) and 48 MHz to 96 MHz Fractional Digital Phase Locked Loop (FDPLL96M)

- External Interrupt Controller (EIC)

- Up to 14 external interrupts

- One non-maskable interrupt

- Two-pin Serial Wire Debug (SWD) programming, test and debugging interface

- Low Power

- Idle and Standby Sleep modes

- Sleep walking peripherals

- Integrated Ultra-Low Power Transceiver for 700/800/900 MHz ISM Band:

- Chinese WPAN band from 779 to 787 MHz

- European SRD band from 863 to 870 MHz

- North American ISM band from 902 to 928 MHz

- Japanese band from 915 to 930 MHz

- Direct Sequence Spread Spectrum with Different Modulation and Data Rates:

- BPSK with 20 and 40 kb/s, compliant to IEEE 802.15.4-2003/2006/2011

- O-QPSK with 100 and 250kb/s, compliant to IEEE 802.15.4-2006/2011

- O-QPSK with 200, 400, 500, and 1000kb/s PSDU data rate

- Industry-leading link budget:

- RX sensitivity up to -105 dBm

- TX output power up to +8.7 dBm

- Hardware-assisted MAC:

- Auto-Acknowledge

- Auto-Retry

- CSMA-CA and Listen Before Talk (LBT)

- Automatic address filtering and automated FCS check

- Special 802.15.4-2011 hardware support:

- FCS computation and Clear Channel Assessment

- RSSI measurement, Energy Detection and Link Quality Indication

- 128 Byte TX/RX Frame Buffer

- Integrated 16 MHz Crystal Oscillator (external crystal is not needed)

- Fully integrated, fast settling transceiver PLL to support frequency hopping

- Hardware Security (AES, True Random Generator)

- Peripherals

- 16-channel Direct Memory Access Controller (DMAC)

- 12-channel event system

- Up to three 16-bit Timer/Counters (TC), including one low-power TC(TC4), each configurable as:

- 16-bit TC with two compare/capture channels

- 8-bit TC with two compare/capture channels

- 32-bit TC with two compare/capture channels, by using two TCs

- Two 24-bit and one 16-bit Timer/Counters for Control (TCC), with extended functions:

- Up to four compare channels with optional complementary output

- Generation of synchronized pulse width modulation (PWM) pattern across port pins

- Deterministic fault protection, fast decay and configurable dead-time between complementary output

- Dithering that increase resolution with up to 5 bit and reduce quantization error

- 32-bit Real Time Counter (RTC) with clock/calendar function

- Watchdog Timer (WDT)

- CRC-32 generator

- One full-speed (12 Mbps) Universal Serial Bus (USB) 2.0 interface

- Embedded host and device function

- Eight endpoints

- Up to two Serial Communication Interfaces (SERCOM), each configurable to operate as either:

- USART with full-duplex or single-wire half-duplex configuration

- I<sup>2</sup>C up to 3.4 MHz

- SPI

- LIN slave

- Up to three Serial Communication Interfaces (SERCOM) including one low-power SERCOM (SERCOM5), each configurable to operate as UART with internal clock

- One Configurable Custom Logic (CCL)

- One 12-bit, 350ksps Analog-to-Digital Converter (ADC) with up to four external channels

- Differential and single-ended input

- Automatic offset and gain error compensation

- Oversampling and decimation in hardware to support 13-, 14-, 15- or 16-bit resolution

- Two Analog Comparators (AC) with window compare function

- Peripheral Touch Controller (PTC)

- 12-Channel capacitive touch and proximity sensing

- Clock

- High precision 16 MHz integrated internal crystal

- 32.768 kHz internal oscillator (OSC32K)

- 32.768 kHz ultra-low power internal oscillator (OSCUMLP32K)

- 16/12/8/4 MHz high-accuracy internal oscillator (OSC16M)

- 48 MHz Digital Frequency Locked Loop (DFLL48M)

- 96 MHz Fractional Digital Phased Locked Loop (FDPLL96M)

- I/O and Package

- 16 programmable I/O pins

- 25-pin module package (12.7 mm x 11.0 mm) with castellated PCB pads

- Operating Voltage

- 1.8V – 3.6V

- Temperature Range

- -40°C to 85°C Industrial

- Power Consumption<sup>(1)</sup>

- RX\_ON = 10.79 mA

- BUSY\_TX = 26.97 mA

- Standby = 2.03 µA

- Backup mode = 0.77 µA

**Note:**

1. For more details, see [9.3.4 Current Consumption Specifications](#).

---

## Table of Contents

---

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| Introduction.....                                                                | 1  |

| Features.....                                                                    | 1  |

| 1. Ordering Information and Module Marking.....                                  | 6  |

| 2. Package Information.....                                                      | 7  |

| 3. Module Block Diagram.....                                                     | 8  |

| 3.1. Interconnection between SAM L21 and AT86RF212B within ATSAMR30E18A SiP..... | 8  |

| 3.2. AT86RF212B Transceiver Circuit Description.....                             | 10 |

| 4. Pinout Information.....                                                       | 12 |

| 5. Nonvolatile Memory Information.....                                           | 16 |

| 6. Boot Loader.....                                                              | 17 |

| 7. Module Description.....                                                       | 18 |

| 7.1. Physical Layer Modes.....                                                   | 18 |

| 7.2. Receiver (RX).....                                                          | 22 |

| 7.3. Transmitter (TX).....                                                       | 23 |

| 7.4. Frame Buffer.....                                                           | 26 |

| 7.5. Crystal Oscillator (XOSC) and Clock Output (CLKM).....                      | 28 |

| 7.6. Frequency Synthesizer (PLL).....                                            | 30 |

| 7.7. Automatic Filter Tuning (FTN).....                                          | 33 |

| 8. Radio Transceiver Usage.....                                                  | 35 |

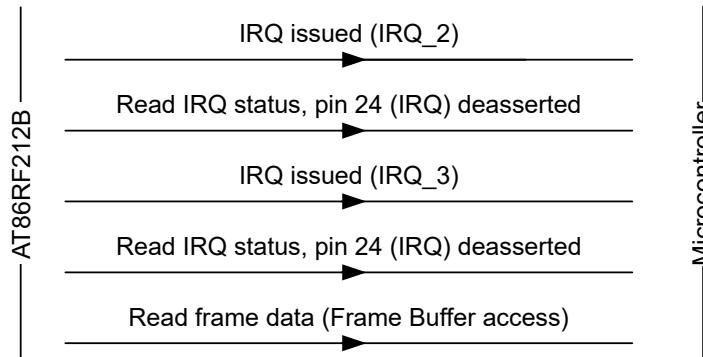

| 8.1. Frame Receive Procedure.....                                                | 35 |

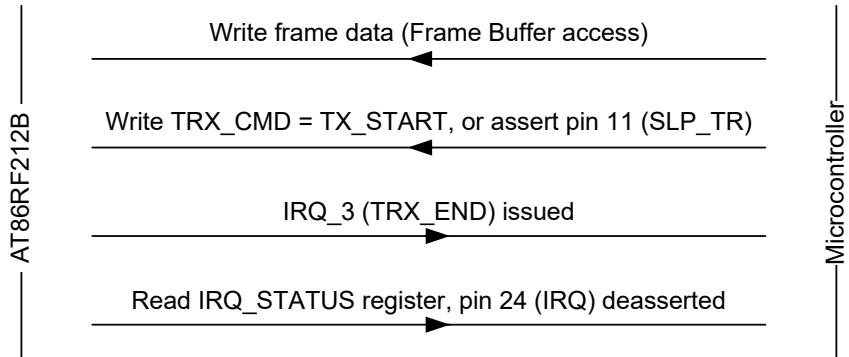

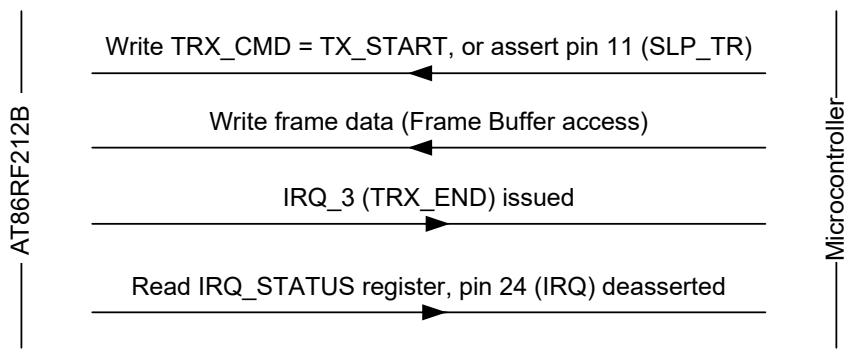

| 8.2. Frame Transmit Procedure.....                                               | 35 |

| 9. Electrical Characteristics.....                                               | 38 |

| 9.1. Absolute Maximum Ratings.....                                               | 38 |

| 9.2. Recommended Operating Conditions.....                                       | 38 |

| 9.3. Module Performance.....                                                     | 38 |

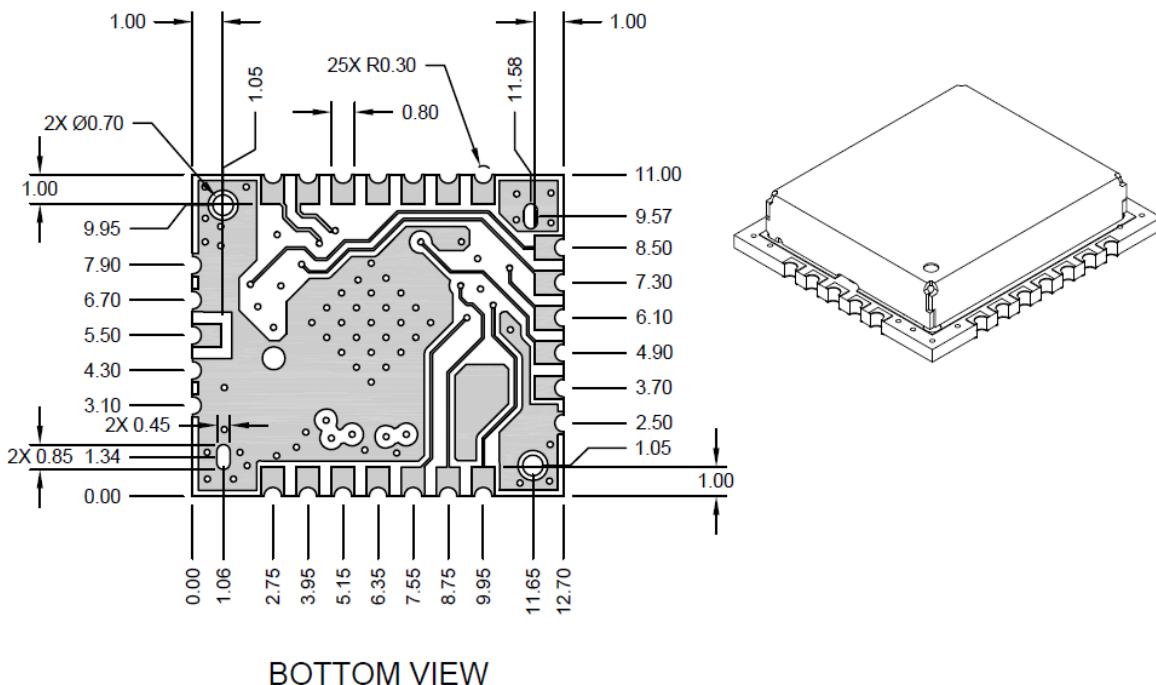

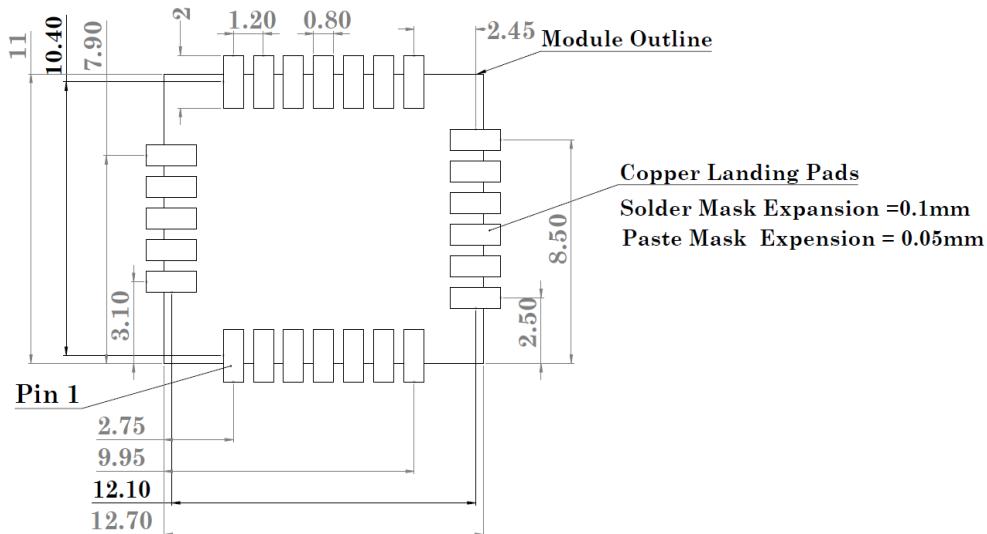

| 10. Mechanical Description.....                                                  | 47 |

| 10.1. Module Outline Drawings.....                                               | 47 |

| 10.2. Footprint.....                                                             | 48 |

| 11. Module Assembly Considerations.....                                          | 49 |

| 12. Reflow Profile Information.....                                              | 50 |

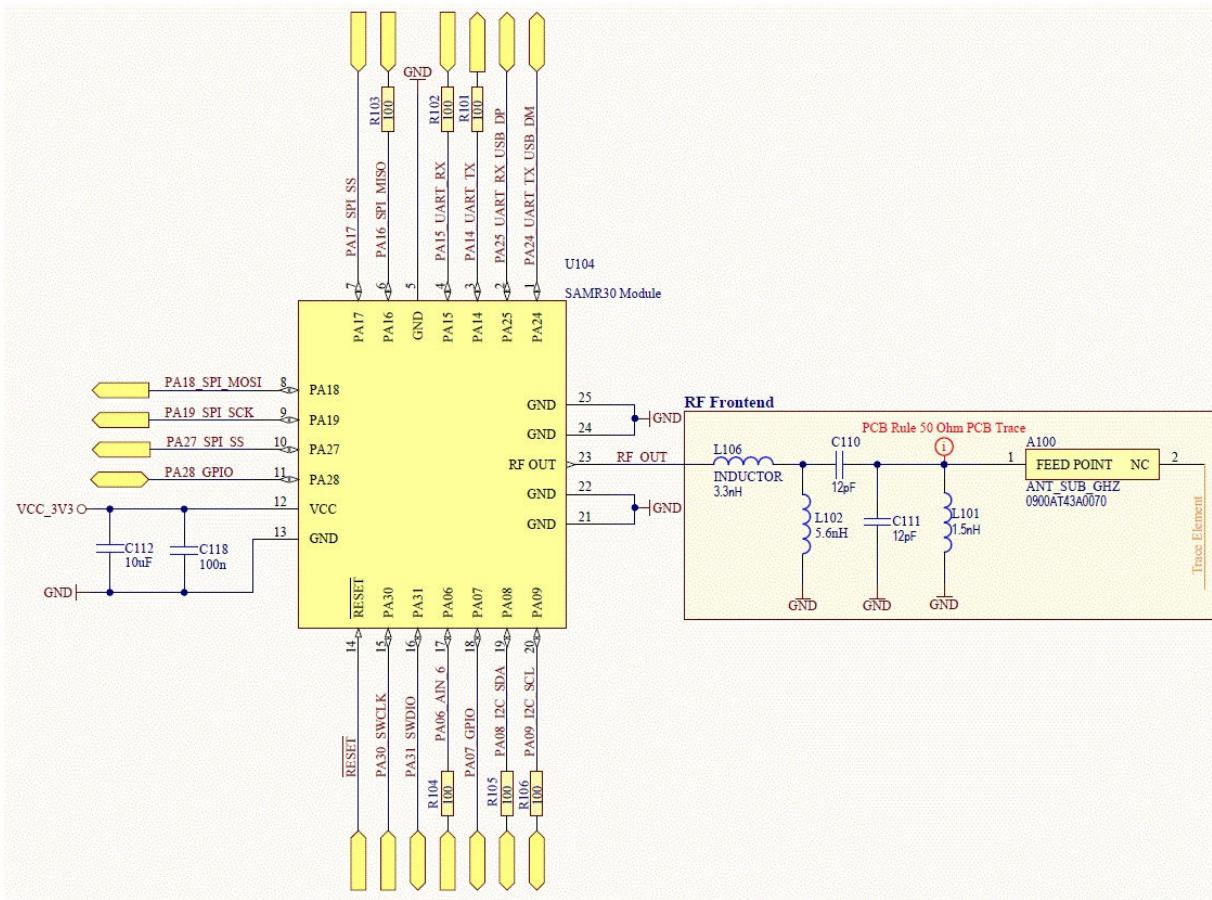

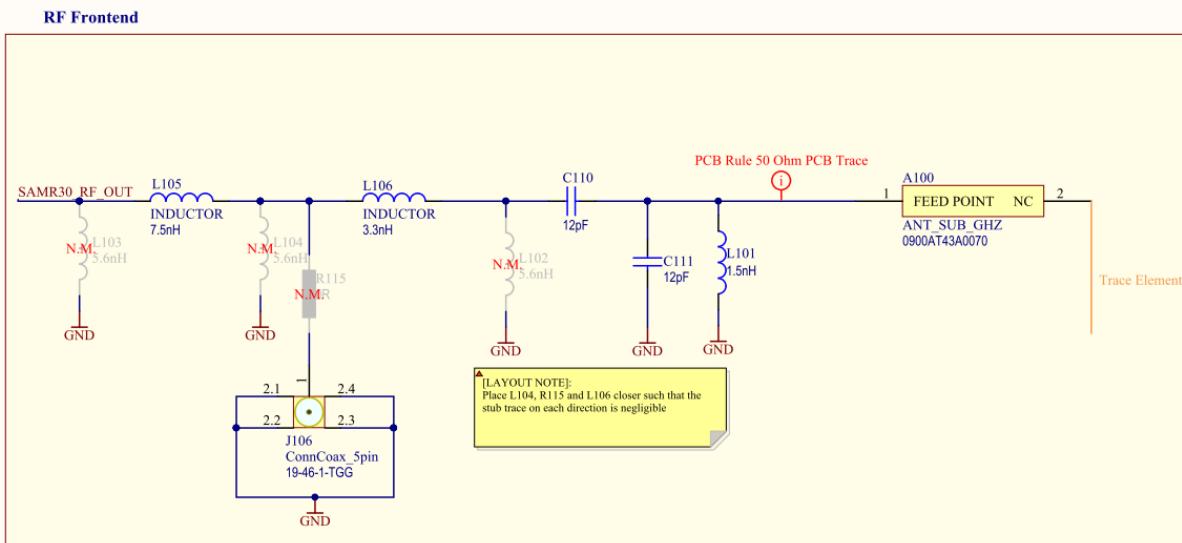

| 13. Application Reference Design.....                                            | 51 |

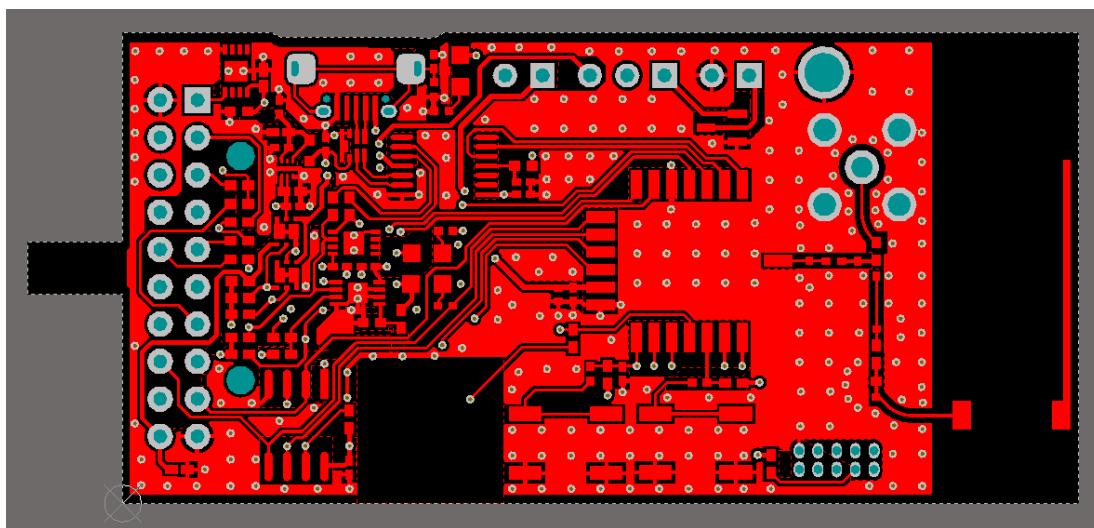

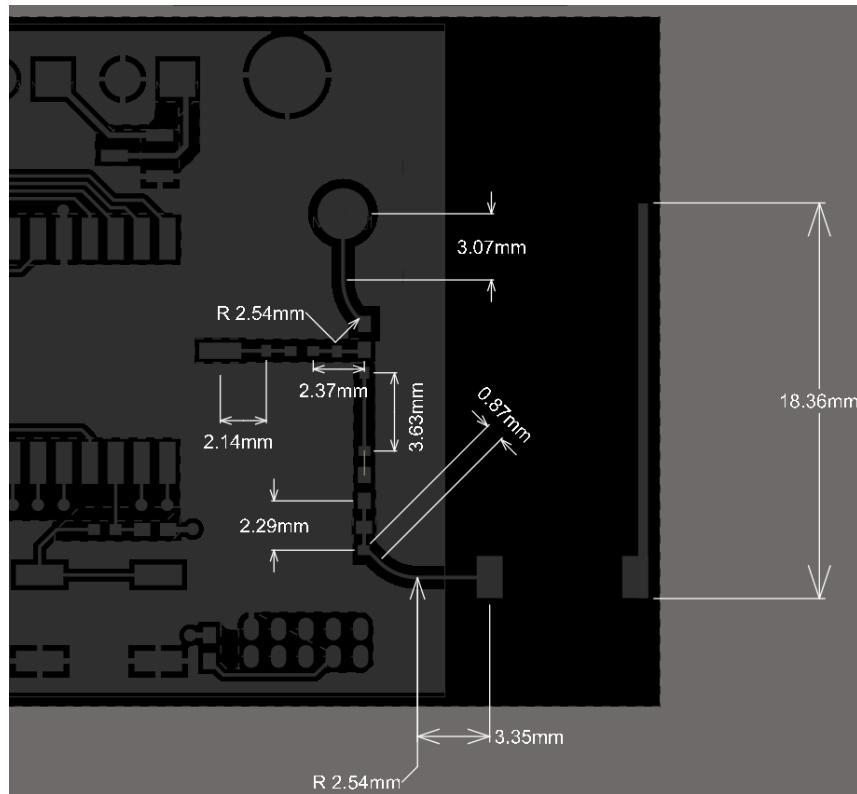

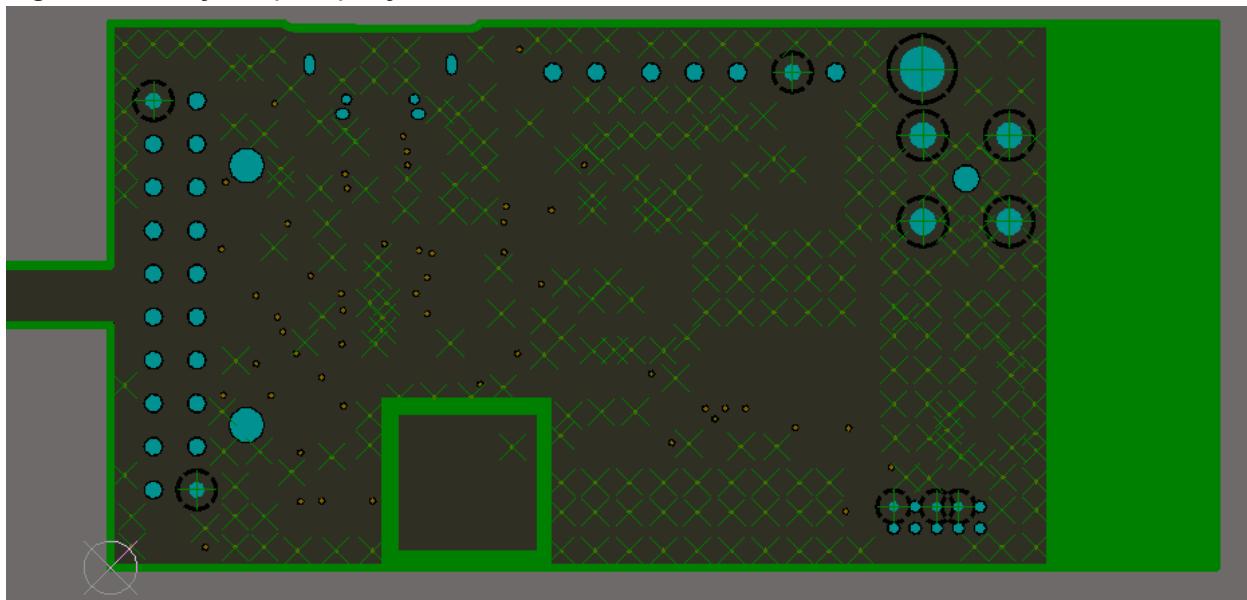

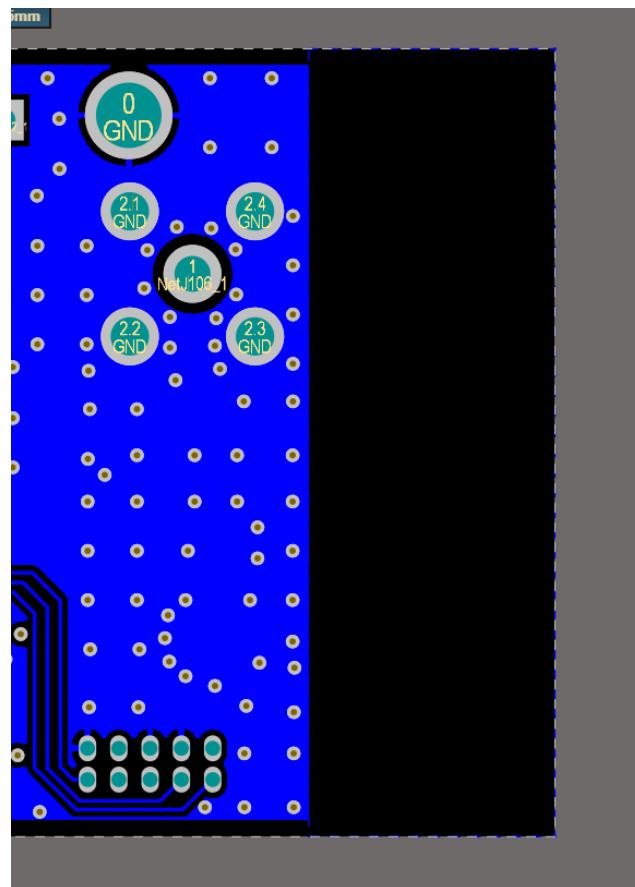

| 13.1. RF Trace Layout Design Instructions.....                                   | 51 |

---

|                                                   |           |

|---------------------------------------------------|-----------|

| 13.2. Routing Guidelines.....                     | 56        |

| <b>14. Regulatory Approval.....</b>               | <b>58</b> |

| 14.1. United States (FCC).....                    | 58        |

| 14.2. Canada (ISED).....                          | 60        |

| 14.3. Europe (ETSI).....                          | 62        |

| 14.4. Approved Antennas.....                      | 64        |

| <b>15. Continuous Transmission Test Mode.....</b> | <b>65</b> |

| 15.1. Overview.....                               | 65        |

| 15.2. Configuration.....                          | 65        |

| <b>16. Reference Documentation.....</b>           | <b>68</b> |

| <b>17. Document Revision History.....</b>         | <b>69</b> |

| The Microchip Web Site.....                       | 70        |

| Customer Change Notification Service.....         | 70        |

| Customer Support.....                             | 70        |

| Microchip Devices Code Protection Feature.....    | 70        |

| Legal Notice.....                                 | 71        |

| Trademarks.....                                   | 71        |

| Quality Management System Certified by DNV.....   | 72        |

| Worldwide Sales and Service.....                  | 73        |

## 1. Ordering Information and Module Marking

The following table provides the ordering details for the ATSAMR30M18A module.

**Table 1-1. Ordering Information for ATSAMR30M18A**

| Model Number | Ordering Code             | Package Dimension            | Number of Pins | Description                                      | Regulatory Approval |

|--------------|---------------------------|------------------------------|----------------|--------------------------------------------------|---------------------|

| ATSAMR30M18A | ATSAMR30M18A-I/<br>RMxxx  | 12.7mm x<br>11mm x<br>2.71mm | 25             | SAM R30<br>Module in Tray<br>package             | FCC, ISED,<br>CE    |

|              | ATSAMR30M18AT-I/<br>RMxxx |                              |                | SAM R30<br>Module in Tape<br>and Reel<br>package |                     |

**Figure 1-1. Module Ordering Code Information**

**ATSAMR 30 M 18 A T – I / RM XXX**

**Product Family**

SAMR = Microcontroller with RF

**Product Series**

30 = Cortex M0 + CPU + Sub GHz

802.15.4 Transceiver

**Pin Count**

M = Module

**Flash Memory Density**

18 = 256 KB

**Device Variant**

A = Hardware Revision

**xxx = Bootloader

FW Version**

**Package Type**

RM = Radio Module

**Temperature Rating**

I = -40 to +85C

**Package Carrier**

T = Tape and Reel

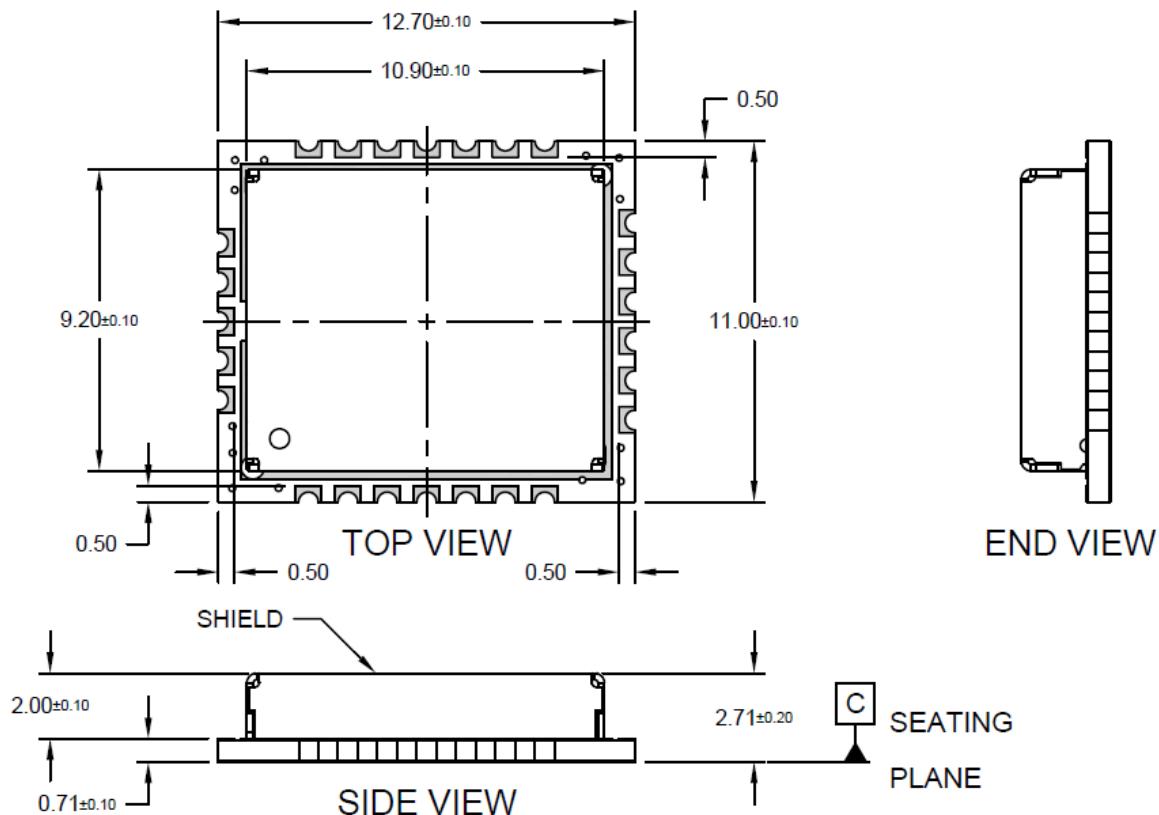

## 2. Package Information

The following table provides the ATSAMR30M18A module package dimensions.

**Table 2-1. ATSAMR30M18A Package Information**

| Parameter       | Value     | Units |

|-----------------|-----------|-------|

| Package size    | 12.7x11.0 | mm    |

| Pad count       | 25        | —     |

| Total thickness | 2.71      | mm    |

| Pad pitch       | 1.2       | mm    |

| Pad width       | 0.8       | mm    |

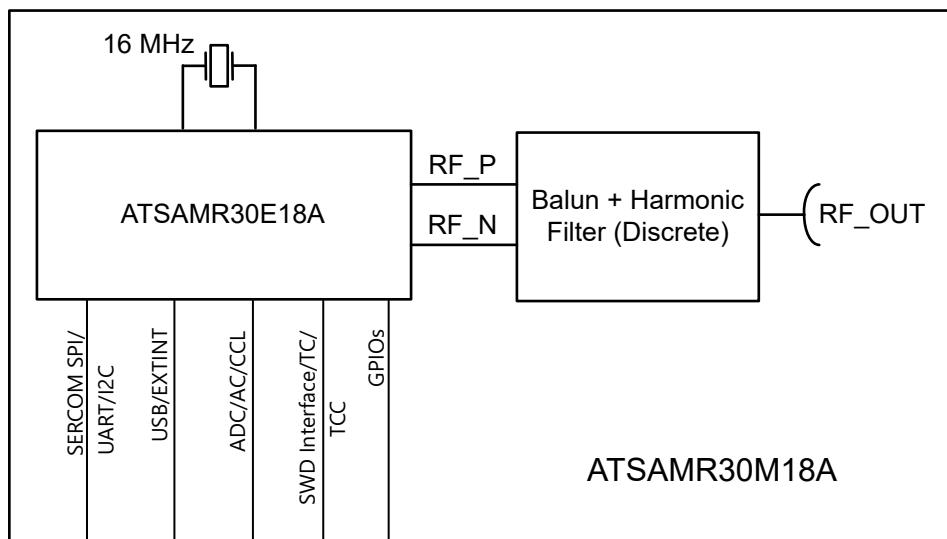

### 3. Module Block Diagram

The ATSAMR30M18A module contains ATSAMR30E18A SiP, 16 MHz crystal, discrete Balun and lumped element Harmonic Filter.

The following figure shows the block diagram of the ATSAMR30M18A module.

**Figure 3-1. Module Block Diagram**

The ATSAMR30E18A SiP consists of two vertically integrated silicon dies:

- SAM L21 ARM Cortex M0+ based microcontroller

- AT86RF212B low-power, low-voltage 700/800/900 MHz transceiver

The local communication and control interface is wired within the package. Key I/O external signals are exposed as I/O pins.

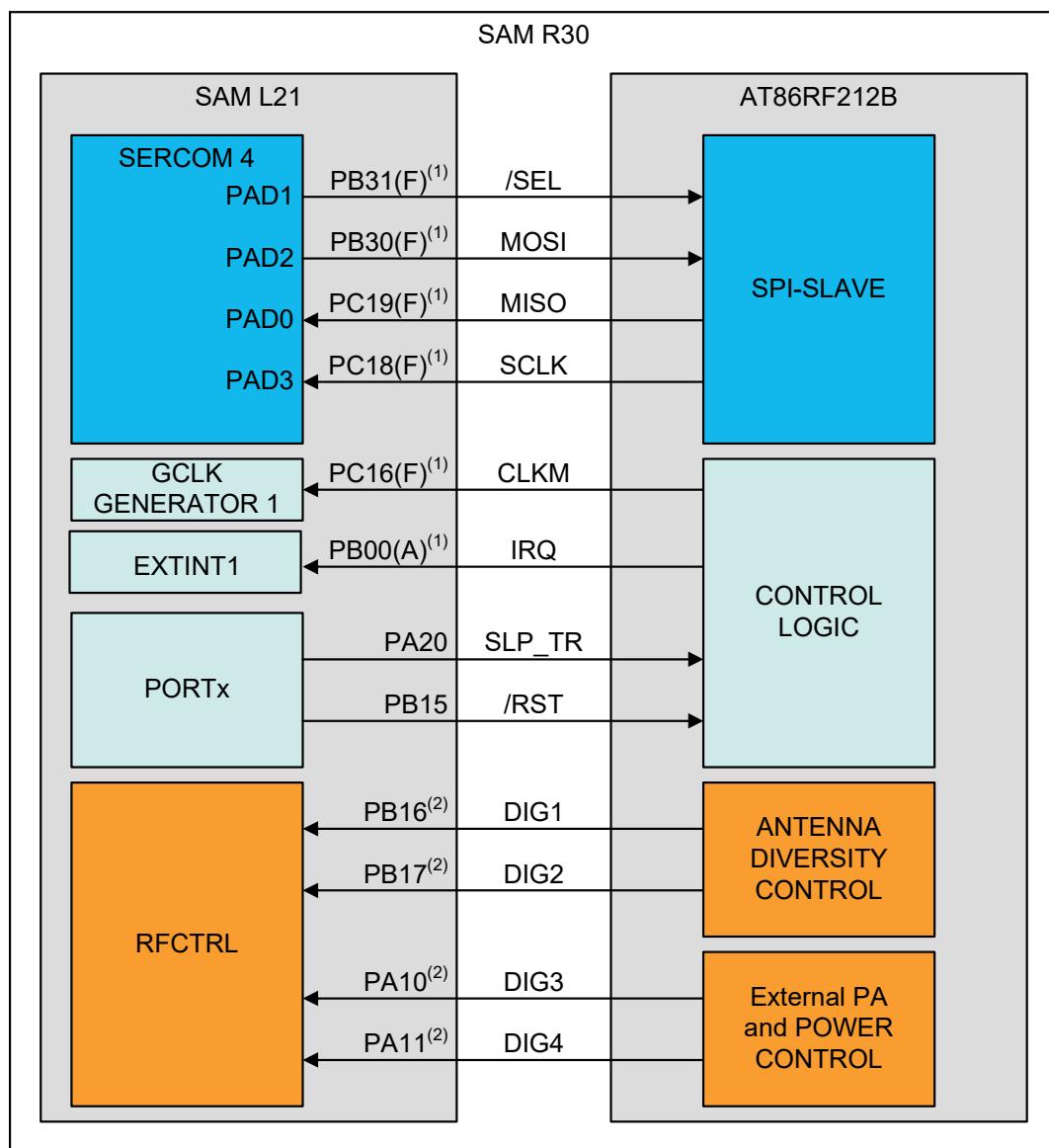

#### 3.1 Interconnection between SAM L21 and AT86RF212B within ATSAMR30E18A SiP

This section describes the interconnection between SAM L21 and AT86RF212B. The interface comprises a slave SPI and additional control signals. This interface is a master SPI interface in SAM L21 as shown in the following figure.

Figure 3-2. Interconnection between SAM L21 and AT86RF212B

1. Alternate pin function and direction has to be configured by software.

2. Pin function is configured by hardware automatically after reset.

The SPI is used for register, Frame Buffer, SRAM, and AES access. The additional control signals are connected to the GPIO/IRQ interface of the microcontroller. The following table introduces the radio transceiver I/O signals and their functionality.

Table 3-1. Microcontroller Interface Signal Description

| Signal | Description                                 |

|--------|---------------------------------------------|

| /SEL   | SPI select signal, active-low               |

| MOSI   | SPI data (master output slave input) signal |

| MISO   | SPI data (master input slave output) signal |

.....continued

| Signal | Description                                                                                                                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK   | SPI clock signal                                                                                                                                                                                                                        |

| CLKM   | Optional, clock output, usable as: <ul style="list-style-type: none"> <li>- microcontroller clock source and/or MAC timer reference</li> <li>- high precision timing reference</li> </ul>                                               |

| IRQ    | Interrupt request signal, further used as: <ul style="list-style-type: none"> <li>- Frame Buffer Empty indicator</li> </ul>                                                                                                             |

| SLP_TR | Multi-purpose control signal (functionality is state dependent): <ul style="list-style-type: none"> <li>- Sleep/Wake up: enable/disable SLEEP state</li> <li>- TX start: BUSY_TX_(ARET) state</li> <li>- disable/enable CLKM</li> </ul> |

| /RST   | AT86RF212B Reset signal; active-low                                                                                                                                                                                                     |

| DIG2   | Optional, <ul style="list-style-type: none"> <li>- IRQ_2 (RX_START) for RX Frame Time Stamping</li> </ul>                                                                                                                               |

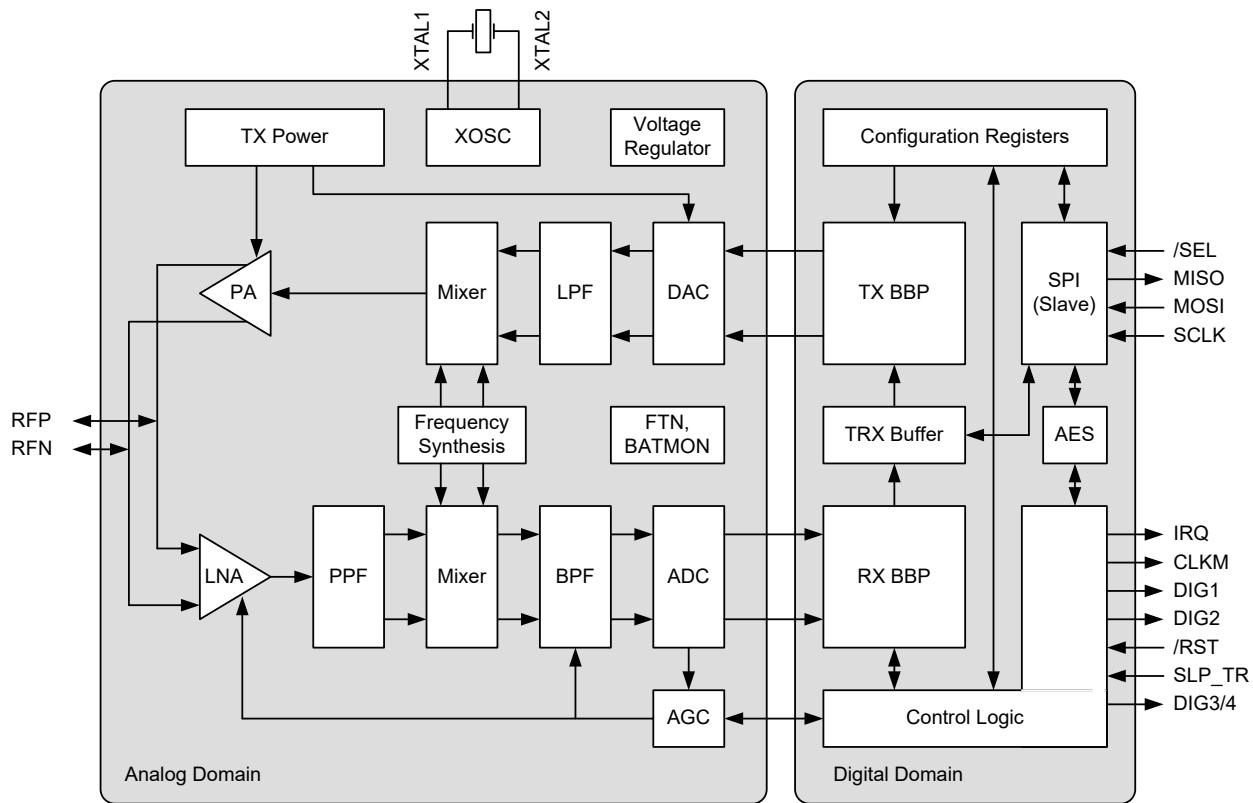

### 3.2 AT86RF212B Transceiver Circuit Description

The AT86RF212B single-chip radio transceiver provides a complete radio transceiver interface between radio frequency signals and baseband microcontroller. It comprises a bidirectional analog RF front end, direct-conversion mixers, low-noise fractional-n PLL, quadrature digitizer, DSP modem and baseband packet-handler optimized for IEEE 802.15.4 MAC/PHY automation and low power. An SPI accessible 128-byte TRX buffer stores receive or transmit data. Radio communication between transmitter and receiver is based on DSSS Spread Spectrum with OQPSK or BPSK modulation schemes as defined by the IEEE 802.15.4 standard. Additional proprietary modulation modes include high-data rate payload encoding and wideband BPSK-40-ALT.

Figure 3-3. AT86RF212B Block Diagram

The number of required external components is minimal. The basic requirements are an antenna, a balun, harmonic filter, crystal oscillator and bypass capacitors. The RF Ports are bidirectional differential signals that do not require external TX/RX switches. Hardware control signals are automatically generated for TX/RX arbitration of high-powered PA/LNA front ends and transmitter diversity for systems with dual antennas.

The AT86RF212B supports the IEEE 802.15.4-2006 [2] standard mandatory BPSK modulation and optional O-QPSK modulation in the 868.3MHz and 915MHz bands. In addition, it supports the O-QPSK modulation defined in IEEE 802.15.4-2011 [4] for the Chinese 780MHz band. For applications not targeting IEEE compliant networks, the radio transceiver supports proprietary High Data Rate Modes based on O-QPSK. Additionally the AT86RF212B provides BPSK-40-ALT wideband BPSK mode for compliance with FCC rule 15.247 and backward compatibility with legacy BPSK networks.

The AT86RF212B features hardware-supported 128-bit security operation. The standalone AES encryption/decryption engine can be accessed in parallel to all PHY operational modes. Configuration of the AT86RF212B, reading and writing of data memory, as well as the AES hardware engine are controlled by the SPI interface and additional control signals.

On-chip low-dropout linear regulators provide clean 1.8 V<sub>DC</sub> power for critical analog and digital subsystems. To conserve power, these rails are automatically sequenced by the transceiver's state machine. This feature greatly improves EMC in the RF domain and reduces external power supply complexity to the simple addition of frequency compensation capacitors on the AVDD and DVDD pins.

Additional features of the Extended Feature Set are provided to simplify the interaction between radio transceiver and microcontroller.

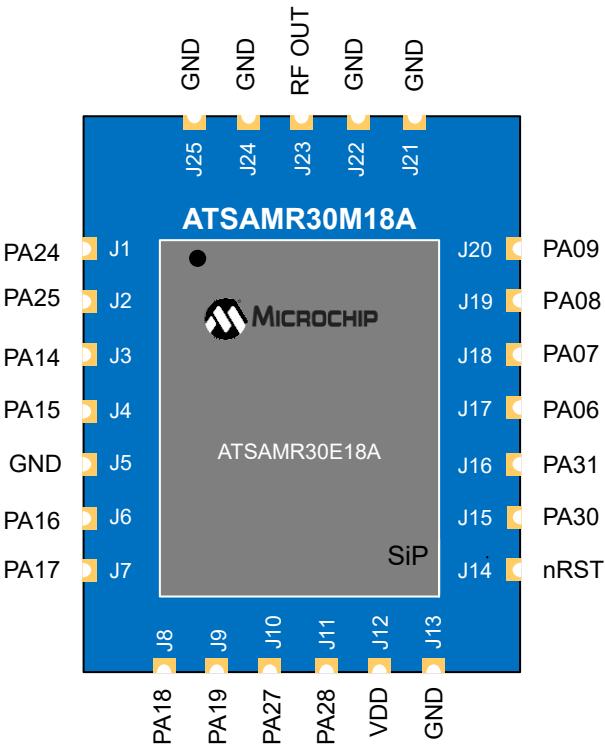

## 4. Pinout Information

The ATSAMR30M18A module pin assignment is shown in the following figure.

Figure 4-1. ATSAMR30M18A Module Pin Assignment

The module pin assignment is shown in the following table. The **SiP pin** column is a reference to the [ATSAMR30E18 datasheet](#) (SAMR30E18A).

Table 4-1. ATSAMR30M18A Module Pin Assignment

| Module  |          |                                             | SAMR30E |                                                                               |

|---------|----------|---------------------------------------------|---------|-------------------------------------------------------------------------------|

| Pin No. | Pin Name | Possible Peripheral Function <sup>(1)</sup> | SiP Pin | Pin Description                                                               |

| J1      | PA24     | UART5_Tx                                    | 22      | EXTINT[12], SERCOM3 or 5/ PAD[2], TC1/ WO[0], TCC1/ WO[2], USB/DM, CCL2/IN[2] |

.....continued

| Module  |                     |                                             | SAMR30E          |                                                                                              |

|---------|---------------------|---------------------------------------------|------------------|----------------------------------------------------------------------------------------------|

| Pin No. | Pin Name            | Possible Peripheral Function <sup>(1)</sup> | SiP Pin          | Pin Description                                                                              |

| J2      | PA25                | UART5_Rx                                    | 23               | EXTINT[13], SERCOM3 or 5/ PAD[3], TC1/ WO[1], TCC1/ WO[3], USB/DP, CCL2/OUT                  |

| J3      | PA14                | UART2_Tx                                    | 15               | EXTINT[14], SERCOM2/PAD[2], TC4/WO[0], TCC0/ WO[4], GCLK/IO[0]                               |

| J4      | PA15                | UART2_Rx                                    | 16               | EXTINT[15], SERCOM2/PAD[3], TC4/WO[1], TCC0/ WO[5], GCLK/IO[1]                               |

| J5      | GND                 | -                                           | 3, 6, 11, 14, 28 | Ground                                                                                       |

| J6      | PA16 <sup>(2)</sup> | SPI1_MISO                                   | 17               | EXTINT[0], PTC_X[4], SERCOM1 or 3/ PAD[0], TCC2/ WO[0], TCC0/ WO[6], GCLK/ IO[2], CCL0/IN[0] |

| J7      | PA17 <sup>(2)</sup> | SPI1_SS                                     | 18               | EXTINT[1], PTC_X[5], SERCOM1 or 3/ PAD[1], TCC2/ WO[1], TCC0/ WO[7], GCLK/ IO[3], CCL0/IN[1] |

| J8      | PA18                | SPI1_MOSI                                   | 19               | EXTINT[2], PTC_X[6], SERCOM1 or 3/ PAD[2], TC4/ WO[0], TCC0/ WO[2], AC/CMP[0], CCL0/IN[2]    |

.....continued

| Module  |          |                                             | SAMR30E          |                                                                                                                     |

|---------|----------|---------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name | Possible Peripheral Function <sup>(1)</sup> | SiP Pin          | Pin Description                                                                                                     |

| J9      | PA19     | SPI1_SCK                                    | 20               | EXTINT[3],<br>PTC_X[7],<br>SERCOM1 or 3/<br>PAD[3], TC4/<br>WO[1], TCC0/<br>WO[3], AC/CMP[1],<br>CCL0/OUT           |

| J10     | PA27     | GPIO                                        | 25               | EXTINT[15],<br>GCLK/IO[0]                                                                                           |

| J11     | PA28     | GPIO                                        | 27               | EXTINT[8], GCLK/<br>IO[0]                                                                                           |

| J12     | VDD      | -                                           | 4, 24, 30        | Power (VDDANA,<br>VDDIO, VDDIN)                                                                                     |

| J13     | GND      | GND                                         | 3, 6, 11, 14, 28 | Ground                                                                                                              |

| J14     | RESET#   | nRST                                        | 26               | CPU Reset                                                                                                           |

| J15     | PA30     | SWCLK                                       | 31               | EXTINT[10],<br>SERCOM1/PAD[2],<br>TCC1/WO[0],<br>CM0P/SWCLK,<br>GCLK/IO[0], CCL1/<br>IN[0]                          |

| J16     | PA31     | SWDIO                                       | 32               | EXTINT[11],<br>SERCOM1/PAD[3],<br>TCC1/WO[1],<br>SWDIO <sup>(3)</sup> ,<br>CCL1/OUT                                 |

| J17     | PA06     | AIN[6]                                      | 7                | EXTINT[6],<br>EXTWAKE[6],<br>AC_AIN[2],<br>ADC_AIN[6],<br>PTC_Y[4],<br>SERCOM0/PAD[2],<br>TCC1/WO[0],<br>CCL0/IN[2] |

.....continued

| Module  |                     |                                             | SAMR30E          |                                                                                                                        |

|---------|---------------------|---------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name            | Possible Peripheral Function <sup>(1)</sup> | SiP Pin          | Pin Description                                                                                                        |

| J18     | PA07                | GPIO                                        | 8                | EXTINT[7],<br>EXTWAKE[7],<br>AC_AIN[3],<br>ADC_AIN[7],<br>SERCOM0/PAD[3],<br>TCC1/WO[1],<br>CCL0/OUT                   |

| J19     | PA08 <sup>(2)</sup> | I2C2_SDA                                    | 9                | NMI, ADC_AIN[16],<br>PTC_X[0] or Y[6],<br>SERCOM0 or 2/<br>PAD[0], TCC0/<br>WO[0], TCC1/<br>WO[2], CCL1/IN[0]          |

| J20     | PA09 <sup>(2)</sup> | I2C2_SCL                                    | 10               | EXTINT[9],<br>ADC_AIN[17],<br>PTC_X[1] or Y[7],<br>SERCOM0 or 2/<br>PAD[1], TCC0/<br>WO[1], TCC1/<br>WO[3], CCL1/IN[1] |

| J21     | GND                 | -                                           | 3, 6, 11, 14, 28 | Ground                                                                                                                 |

| J22     | GND                 | -                                           | 3, 6, 11, 14, 28 | Ground                                                                                                                 |

| J23     | RF OUT              | RFP, RFN                                    | 12,13            | 50 ohm single-ended RF Output                                                                                          |

| J24     | GND                 | -                                           | 3, 6, 11, 14, 28 | Ground                                                                                                                 |

| J25     | GND                 | -                                           | 3, 6, 11, 14, 28 | Ground                                                                                                                 |

**Note:**

1. The peripheral function indicated in this column is based on the reference design. This is one of the possibilities as each ATSAMRE18A pin supports several multiplexed peripheral functions mentioned in Pin description column.

2. Only these pins can be used for the SERCOM I2C mode: PA08, PA09, PA16, and PA17.

3. This function is only activated in the presence of a debugger.

## 5. Nonvolatile Memory Information

The ATSAMR30M18A provides the user a readable Nonvolatile Memory (NVM) space called user row, programmed in the factory. The base address for the application is 0x804008. The following table shows the implemented data structure.

**Table 5-1. NVM (user row) Data**

| Address Offset   | Field Name       | Field Description                   | Length  |

|------------------|------------------|-------------------------------------|---------|

| BaseAddr. + 0x00 | MIB_REVISION     | Data structure revision. 0x1501     | 2 Byte  |

| + 0x02           | MAC_IEEE_ADDRESS | Module specific IEEE MAC Address    | 8 Byte  |

| + 0x0A           | BOARD_SERIAL     | Module specific serial number       | 10 Byte |

| + 0x14           | PART_NO          | Product specific part number        | 8 Bytes |

| + 0x1C           | PCBA_REV         | Product PCB/assembly revision       | 1 Byte  |

| + 0x1D           | XTAL_TRIM        | Reference crystal calibration value | 1 Byte  |

| + 0x1E           | CRC16            | Checksum for this data structure    | 2 Byte  |

BOARD\_SERIAL and PART\_NO for this ATSAMR30M18A will be programmed with 0xFF. The end user application software must copy two data fields to radio transceiver registers. The data in MAC\_IEEE\_ADDRESS must be copied to the registers IEEE\_ADDR\_0 to IEEE\_ADDR\_7 of AT86RF212B. The MAC\_IEEE\_ADDRESS is stored little-endian with the first byte stored at the lowest address.

The XTAL\_TRIM value is determined during the production test and must be copied to the transceiver XTAL\_TRIM bits of XOSC\_CTRL register (AT86RF212B). For more information on registers, see the [SAM R30 Datasheet](#). Programming the XTAL\_TRIM value reduces the absolute deviation for the 16 MHz reference crystal. CRC16 is calculated using CRC-CCITT with the polynomial  $x^{16} + x^{12} + x^5 + 1$  and initial value as 0xFFFF.

---

## 6. Boot Loader

The module is delivered with a pre-flashed boot loader. The bootloader memory section (8 kB) is write-protected at factory. To overwrite the write-protection, program the BOOTPROT bits[2:0] of NVM User Row with the default value of 0x7.

Customers not using the bootloader must program the BOOTPROT bits to default value to program the complete Flash of the SAMR30 device. For detailed information, refer to the boot loader manual. The related information is available in the AVR2054 Application Note.

## 7. Module Description

This section provides an overview of the major features of AT86RF212B. For detailed information, refer to Reference guide - AT86RF212B section of the [SAM R30 datasheet](#).

### 7.1 Physical Layer Modes

#### 7.1.1 Spreading, Modulation, and Pulse Shaping

The AT86RF212B supports various physical layer (PHY) modes independent of the RF channel selection. Symbol mapping along with chip spreading, modulation, and pulse shaping are a part of the digital base band processor.

The combination of spreading, modulation, and pulse shaping are restricted to several combinations as shown in the table below.

The AT86RF212B is fully compliant to the IEEE 802.15.4 low data rate modes of 20kb/s or 40kb/s, employing binary phase-shift keying (BPSK) and spreading with a fixed chip rate of 300kchip/s or 600kchip/s, respectively. The symbol rate is 20ksymbol/s or 40ksymbol/s, respectively. In both cases, pulse shaping is approximating a raised cosine filter with roll-off factor 1.0 (RC-1.0).

For optional data rates according to IEEE 802.15.4-2006, offset quadrature phase-shift keying (O-QPSK) is supported by the AT86RF212B with a fixed chip rate of either 400kchip/s or 1000kchip/s.

At a chip rate of 400kchip/s, there is a choice between two different Pulse Shaping modes. One Pulse Shaping mode uses a combination of both, half-sine shaping (SIN) and raised cosine filtering with roll-off factor 0.2 (RC-0.2) according to IEEE 802.15.4-2006 [2] for the 868.3MHz band. The other uses raised cosine filtering with roll-off factor 0.2 (RC-0.2).

At a chip rate of 1000kchip/s, pulse shaping is either half-sine filtering (SIN) as specified in IEEE 802.15.4-2006 [2], or, alternatively, raised cosine filtering with roll-off factor 0.8 (RC-0.8) as specified in IEEE 802.15.4c™-2009 [3] and IEEE 802.15.4-2011 [4].

For O-QPSK, the AT86RF212B supports spreading according to IEEE 802.15.4-2006 with data rates of either 100kb/s or 250kb/s depending on the chip rate, leading to a symbol rate of either 25ksymbol/s or 62.5ksymbol/s, respectively.

Additionally, the AT86RF212B supports two more spreading codes for O-QPSK with shortened code lengths. This leads to higher but non IEEE 802.15.4 compliant data rates for PSDU transmission at 200, 400, 500, and 1000kb/s.

**Table 7-1. Modulation and Pulse Shaping**

| Modulation | Chip Rate<br>[kchip/s] | Supported Data Rate for<br>PPDU Header [kb/s] | Supported Data Rates for<br>PSDU [kb/s] | Pulse Shaping |

|------------|------------------------|-----------------------------------------------|-----------------------------------------|---------------|

| BPSK       | 300                    | 20                                            | 20                                      | RC-1.0        |

|            | 600                    | 40                                            | 40 <sup>(1)</sup>                       | RC-1.0        |

.....continued

| Modulation | Chip Rate<br>[kchip/s] | Supported Data Rate for<br>PPDU Header [kb/s] | Supported Data Rates for<br>PSDU [kb/s] | Pulse Shaping  |

|------------|------------------------|-----------------------------------------------|-----------------------------------------|----------------|

| O-QPSK     | 400                    | 100                                           | 100, 200, 400                           | SIN and RC-0.2 |

|            | 400                    | 100                                           | 100, 200, 400                           | RC-0.2         |

|            | 1000                   | 250                                           | 250, 500 <sup>(1)</sup> , 1000          | SIN            |

|            | 1000                   | 250                                           | 250, 500 <sup>(1)</sup> , 1000          | RC-0.8         |

1. Support of two different spreading codes.

In the following table, all PHY modes supported by the AT86RF212B are summarized with the relevant setting for each bit of register TRX\_CTRL\_2. The “-“ (minus) character means that the bit entry is not relevant for the particular PHY mode.

|                          |  | TRX_CTRL_2 Register Bits |   |   |   |   |   |   |   |                                                                   |  |

|--------------------------|--|--------------------------|---|---|---|---|---|---|---|-------------------------------------------------------------------|--|

| PHY Mode                 |  | 7                        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Compliance                                                        |  |

| BPSK-20                  |  | -                        | - | - | 0 | 0 | 0 | 0 | 0 | IEEE 802.15.4™-2003/2006/2011:<br>channel page 0, channel 0       |  |

| BPSK-40                  |  | -                        | - | - | 0 | 0 | 1 | 0 | 0 | IEEE 802.15.4™-2003/2006/2011:<br>channel page 0, channel 1 to 10 |  |

| BPSK-40-ALT              |  | -                        | - | - | 1 | 0 | 1 | 0 | 0 | Proprietary,<br>alternative spreading code                        |  |

| OQPSK-SIN-RC-100         |  | -                        | - | - | 0 | 1 | 0 | 0 | 0 | IEEE 802.15.4-2006/2011:<br>channel page 2, channel 0             |  |

| OQPSK-SIN-RC-200         |  | -                        | - | - | 0 | 1 | 0 | 0 | 1 | Proprietary                                                       |  |

| OQPSK-SIN-RC-400-SCR-ON  |  | -                        | - | 1 | 0 | 1 | 0 | 1 | 0 | Proprietary, scrambler on                                         |  |

| OQPSK-SIN-RC-400-SCR-OFF |  | -                        | - | 0 | 0 | 1 | 0 | 1 | 0 | Proprietary, scrambler off                                        |  |

| OQPSK-RC-100             |  | -                        | - | - | 1 | 1 | 0 | 0 | 0 | Proprietary                                                       |  |

| OQPSK-RC-200             |  | -                        | - | - | 1 | 1 | 0 | 0 | 1 | Proprietary                                                       |  |

| OQPSK-RC-400-SCR-ON      |  | -                        | - | 1 | 1 | 1 | 0 | 1 | 0 | Proprietary, scrambler on                                         |  |

| OQPSK-RC-400-SCR-OFF     |  | -                        | - | 0 | 1 | 1 | 0 | 1 | 0 | Proprietary, scrambler off                                        |  |

| OQPSK-SIN-250            |  | -                        | - | - | 0 | 1 | 1 | 0 | 0 | IEEE 802.15.4-2006/2011:<br>channel page 2, channel 1 to 10       |  |

| OQPSK-SIN-500            |  | -                        | - | - | 0 | 1 | 1 | 0 | 1 | Proprietary                                                       |  |

| OQPSK-SIN-500-ALT        |  | -                        | - | - | 0 | 1 | 1 | 1 | 1 | Proprietary,<br>alternative spreading code                        |  |

.....continued

| TRX_CTRL_2 Register Bits |   |   |   |   |   |   |   |   |                                                       |

|--------------------------|---|---|---|---|---|---|---|---|-------------------------------------------------------|

| PHY Mode                 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Compliance                                            |

| OQPSK-SIN-1000-SCR-ON    | - | - | 1 | 0 | 1 | 1 | 1 | 0 | Proprietary, scrambler on                             |

| OQPSK-SIN-1000-SCR-OFF   | - | - | 0 | 0 | 1 | 1 | 1 | 0 | Proprietary, scrambler off                            |

| OQPSK-RC-250             | - | - | - | 1 | 1 | 1 | 0 | 0 | IEEE 802.15.4-2011:<br>channel page 5, channel 0 to 3 |

| OQPSK-RC-500             | - | - | - | 1 | 1 | 1 | 0 | 1 | Proprietary                                           |

| OQPSK-RC-500-ALT         | - | - | - | 1 | 1 | 1 | 1 | 1 | Proprietary,<br>alternative spreading code            |

| OQPSK-RC-1000-SCR-ON     | - | - | 1 | 1 | 1 | 1 | 1 | 0 | Proprietary, scrambler on                             |

| OQPSK-RC-1000-SCR-OFF    | - | - | 0 | 1 | 1 | 1 | 1 | 0 | Proprietary, scrambler off                            |

### 7.1.2 Recommended PHY Modulation Modes for Different Frequency Bands

The following are the recommended PHY modes for North American band:

- BPSK-40

- BPSK-40-ALT

- OQPSK-SIN-250/500/1000

The following are the recommended PHY modes for European band:

- BPSK-20

- OQPSK-SIN-RC-100/200/400

- OQPSK-RC-100/200/400

### 7.1.3 Configuration

The PHY mode can be selected by setting the appropriate BPSK\_OQPSK, SUB\_MODE, OQPSK\_DATA\_RATE, and ALT\_SPECTRUM bits in the TRX\_CTRL\_2. During configuration, the transceiver needs to be in TRX\_OFF state.

### 7.1.4 Symbol Period

Within IEEE 802.15.4 and, accordingly, within this document, time references are often specified in units of symbol periods, leading to a PHY mode independent description. The table below shows the duration of the symbol period.

**Table 7-2. Duration of the Symbol Period**

| Modulation | PSDU Data Rate<br>[kb/s] | Duration of Symbol Period [μs] |

|------------|--------------------------|--------------------------------|

| BPSK       | 20                       | 50                             |

|            | 40                       | 25                             |

| O-QPSK     | 100, 200, 400            | 40                             |

|            | 250, 500, 1000           | 16                             |

- For the proprietary High Data Rate Modes, the symbol period is (by definition) the same as the symbol period of the corresponding base mode.

### 7.1.5 Proprietary High Data Rate Modes

The main features are:

- High data rates up to 1000kb/s

- Support of Basic and Extended Operating Mode

- Reduced ACK timing (optional)

#### 7.1.5.1 Overview

The AT86RF212B supports alternative data rates of 200, 400, 500, and 1000kb/s for applications not necessarily targeting IEEE 802.15.4 compliant networks.

The High Data Rate Modes utilize the same RF channel bandwidth as the IEEE 802.15.4-2006 sub-1GHz O-QPSK modes. Higher data rates are achieved by using the modified O-QPSK spreading codes having reduced code lengths. The lengths are reduced by the factor of two or by the factor of four.

For O-QPSK with 400kchip/s, this leads to a data rate of 200kb/s (2-fold) and 400kb/s (4-fold), respectively.

For O-QPSK with 1000kchip/s, the resulting data rate is 500kb/s (2-fold) and 1000kb/s (4-fold), respectively.

Due to the decreased spreading factor, the sensitivity of the receiver is reduced. The  $P_{SENS}$  parameter in the *Receiver Characteristics* shows typical values of the sensitivity for different data rates.

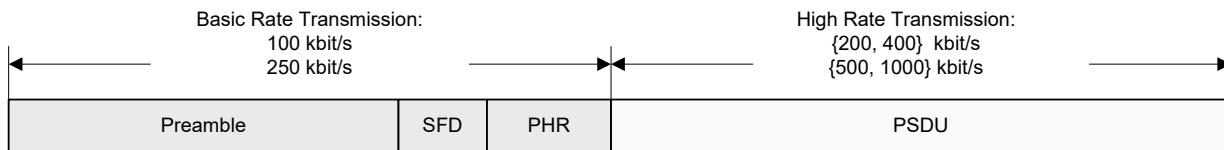

#### 7.1.5.2 High Data Rate Frame Structure

In order to allow robust frame synchronization, the AT86RF212B high data rate modulation is restricted to the PSDU part only. The PPDU header (the preamble, the SFD, and the PHR field) are transmitted with a rate of either 100kb/s or 250kb/s (basic rates).

**Figure 7-1. High Date Rate Frame Structure**

Due to the overhead caused by the PPDU header and the FCS, the effective data rate is less than the selected data rate, depending on the length of the PSDU.

Consequently, high data rate transmission is useful for large PSDU lengths due to the higher effective data rate, or in order to reduce the power consumption of the system.

#### 7.1.5.3 High Data Rate Mode Options

##### Reduced Acknowledgment Time

If the AACK\_ACK\_TIME bit in the XAM\_CTRL\_1 register (XAH\_CTRL\_1.AACK\_ACK\_TIME) is set, the acknowledgment time is reduced to the duration of two symbol periods for 200 and 400kb/s data rates, and to three symbol periods for 500 and 1000kb/s data rates. The reduced acknowledgment time is untouched in IEEE 802.15.4. Otherwise, it defaults to 12 symbol periods according to IEEE 802.15.4.

##### Receiver Sensitivity Control

The different data rates between PPDU header (SHR and PHR) and PHY payload (PSDU) cause a different sensitivity between header and payload. This can be adjusted by defining sensitivity threshold levels of the receiver. With a sensitivity threshold level set, the AT86RF212B does not synchronize to

---

frames with an RSSI level below that threshold. The sensitivity threshold is configured by the RX\_PDT\_LEVEL bits in the RX\_SYN register (RX\_SYN.RX\_PDT\_LEVEL).

### Scrambler

For data rates 400kb/s and 1000kb/s, additional chip scrambling is applied default in order to mitigate data dependent spectral properties. Scrambling can be disabled if the OQPSK\_SCRAM\_EN bit in the TRX\_CTRL\_2 register (TRX\_CTRL\_2.OQPSK\_SCRAM\_EN) is set to zero.

### Energy Detection

The Energy Detection (ED) measurement time span is eight symbol periods according to IEEE 802.15.4. For frames operated at a higher data rate, the automated measurement duration is reduced to two symbol periods taking reduced frame durations into account. This means, the ED measurement time is 80 $\mu$ s for modes 200kb/s and 400kb/s, and 32 $\mu$ s for modes 500kb/s and 1000kb/s. For manually initiated ED measurements in these modes, the measurement time is still eight symbol periods.

### Carrier Sense

For clear channel assessment, IEEE 802.15.4-2006 specifies several modes which may either apply “energy above threshold” or “carrier sense” (CS) or a combination of both. Since signals of the High Data Rate Modes are not compliant to IEEE 802.15.4-2006, CS is not supported when the AT86RF212B is operating in these modes. However, “energy above threshold” is supported.

### Link Quality Indicator (LQI)

For the High Data Rate Modes, the link quality value does not contain useful information and should be discarded.

## 7.2 Receiver (RX)

### 7.2.1 Overview

The AT86RF212B transceiver is split into an analog radio front-end and a digital domain. Referring to the receiver part of the analog domain, the differential RF signal is amplified by a low noise amplifier (LNA) and split into quadrature signals by a poly-phase filter (PPF). Two mixer circuits convert the quadrature signal down to an intermediate frequency. Channel selectivity is achieved by an integrated band-pass filter (BPF). The subsequent analog-to-digital converter (ADC) samples the receive signal and additionally generates a digital RSSI signal. The ADC output is then further processed by the digital baseband receiver (RX BBP), which is part of the digital domain.

The BBP performs further filtering and signal processing. In RX\_ON state, the receiver searches for the synchronization header. Once the synchronization is established and the SFD is found, the received signal is demodulated and provided to the Frame Buffer. Upon synchronization the receiver performs a state change from RX\_ON to BUSY\_RX which is indicated by the TRX\_STATUS bits in the TRX\_STATUS register (TRX\_STATUS.TRX\_STATUS). Once the frame is received, the receiver switches back to RX\_ON in the listen mode on the selected channel. A similar scheme applies to the Extended Operating Mode.

The receiver is designed to handle reference oscillator accuracies up to  $\pm 60$ ppm; refer to the  $f_{SRD}$  parameter in the *General RF Specifications* section. This results in the estimation and correction of frequency and symbol rate errors up to  $\pm 120$ ppm.

Several status information are generated during the receive process: LQI, ED, and RX\_STATUS. They are automatically appended during Frame Read Access. Some information is also available through

---

register access, for example the PHY\_ED\_LEVEL.ED\_LEVEL and FCS correctness with the PHY\_RXSII.RX\_CRC\_VALID.

The Extended Operating Mode of the AT86RF212B supports frame filtering and pending data indication.

### 7.2.2 Frame Receive Procedure

The frame receive procedure, including the radio transceiver setup for reception and reading PSDU data from the Frame Buffer, is described in the *Frame Receive Procedure* section.

### 7.2.3 Configuration

In Basic Operating Mode, the receiver is enabled by writing command RX\_ON to the TRX\_CMD bits in the TRX\_STATE register (TRX\_STATE.TRX\_CMD) in states TRX\_OFF or PLL\_ON. In Extended Operating Mode, the receiver is enabled for RX\_AACK operation from state PLL\_ON by writing the command RX\_AACK\_ON.

There is no additional configuration required to receive IEEE 802.15.4 compliant frames in Basic Operating Mode. However, the frame reception in the AT86RF212B Extended Operating Mode requires further register configurations.

For specific applications, the receiver can additionally be configured to handle critical environment to simplify the interaction with the microcontroller, or to operate in different data rates.

There are scenarios where CSMA-CA is not used before a transmission or where CSMA-CA is not really reliable, for example in hidden node scenarios. As two transceivers compete for the use of one channel they may interfere with each other which may produce unreliable transmission. Receiver Override can be used to cope with such scenarios. The level of interference (which can be caused by a new incoming frame) is continuously measured while decoding a frame. The synchronization to the potential new frame starts if the interference level does not allow for a reliable detection.

The AT86RF212B receiver has an outstanding sensitivity performance. At certain environmental conditions or for High Data Rate Modes it may be useful to manually decrease this sensitivity. This is achieved by adjusting the synchronization header detector threshold using register the RX\_PDT\_LEVEL bits in the RX\_SYN register (RX\_SYN.RX\_PDT\_LEVEL). Received signals with a RSSI value below the threshold do not activate the demodulation process.

Furthermore, at times it may be useful to protect a received frame against overwriting by a new subsequent data frame, when the receive data buffer has not been read on time. A Dynamic Frame Buffer Protection is enabled with the RX\_SAFE\_MODE bit in the TRX\_CTRL\_2 register (TRX\_CTRL\_2.RX\_SAFE\_MODE) set. The receiver remains in RX\_ON or RX\_AACK\_ON state until the whole frame is uploaded by the microcontroller, indicated by pin 23 (/SEL) = H during the SPI Frame Receive Mode. The Frame Buffer content is only protected if the FCS is valid.

A Static Frame Buffer Protection is enabled with the RX\_PDT\_DIS bit in the RX\_SYN register (RX\_SYN.RX\_PDT\_DIS) set. The receiver remains in RX\_ON or RX\_AACK\_ON state and no further SHR is detected until the register bit RX\_PDT\_DIS is set back.

## 7.3 Transmitter (TX)

### 7.3.1 Overview

The AT86RF212B transmitter utilizes a direct up-conversion topology. The digital transmitter (TX BBP) generates the in-phase (I) and quadrature (Q) component of the modulation signal. A Digital-to-Analog converter (DAC) forms the analog modulation signal. A quadrature mixer pair converts the analog

modulation signal to the RF domain. The Power Amplifier (PA) provides signal power delivered to the differential antenna pins (RFP, RFN). Both, the LNA of the receiver input and the PA of the transmitter output are internally connected to the bidirectional differential antenna pins so that no external antenna switch is needed.

Using the default settings, the PA incorporates an equalizer to improve its linearity. The enhanced linearity keeps the spectral side lobes of the transmit spectrum low in order to meet the requirements of the European 868.3MHz band.

If the PA Boost mode is turned on, the equalizer is disabled. This allows delivery of a higher transmit power of up to +9 dBm at the cost of higher spectral side lobes and higher harmonic power.

In Basic Operating Mode, a transmission is started from PLL\_ON state by either writing TX\_START to the TRX\_CMD bits in the TRX\_STATE register (TRX\_STATE.TRX\_CMD) or by a rising edge of pin 11 (SLP\_TR).

In Extended Operating modes, a transmission might be started automatically depending on the transaction phase of either RX\_AACK or TX\_ARET.

### 7.3.2 Frame Transmit Procedure

The frame transmit procedure, including writing PSDU data into the Frame Buffer and initiating a transmission, is described in the *Radio Transceiver Usage - Frame Transmit Procedure* section.

### 7.3.3 TX Output Power

The maximum output power of the transmitter is typically +3.2 dBm in normal mode and +8.7 dBm in boost mode. The TX output power can be set via the TX\_PWR bits in the PHY\_TX\_PWR register (PHY\_TX\_PWR.TX\_PWR). The output power of the transmitter can be controlled down to -27 dBm with 1 dB resolution.

To meet the spectral requirements of the European and Chinese bands, it is necessary to limit the TX power by appropriate setting of the TX\_PWR and GC\_PA bits in the PHY\_TX\_PWR register (PHY\_TX\_PWR.TX\_PWR and PHY\_TX\_PWR.GC\_PA), and the GC\_TX\_OFFSET bits in the RF\_CTRL\_0 register (RF\_CTRL\_0.GC\_TX\_OFFSET)..

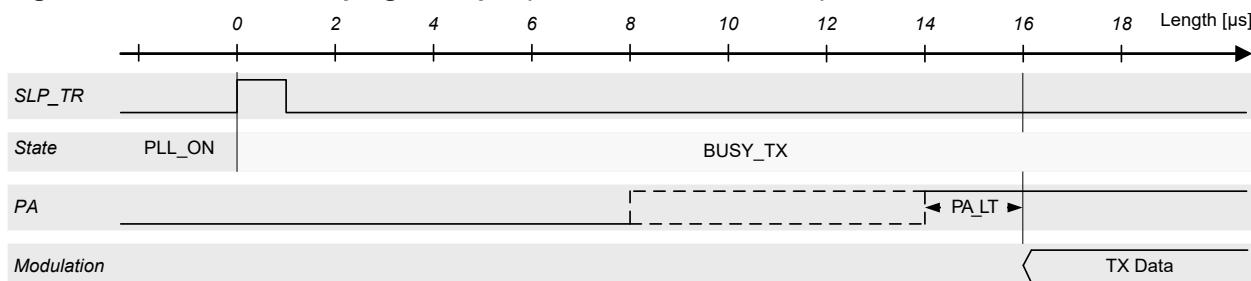

### 7.3.4 TX Power Ramping

To optimize the output Power Spectral Density (PSD), individual transmitter blocks are enabled sequentially. A transmit action is started by either the rising edge of pin 11 (SLP\_TR) or by writing TX\_START command to the TRX\_CMD bits in the TRX\_STATE register (TRX\_STATE.TRX\_CMD). One symbol period later the data transmission begins. During this time period, the PLL settles to the frequency used for transmission. The PA is enabled prior to the data transmission start. This PA lead time can be adjusted with the PA\_LT bits in the RF\_CTRL\_0 register (RF\_CTRL\_0.PA\_LT). The PA is always enabled at the lowest gain value corresponding to GC\_PA = 0. Then the PA gain is increased automatically to the value set by the GC\_PA bits in the PHY\_TX\_PWR register (PHY\_TX\_PWR.GC\_PA). After transmission is completed, TX power ramping down is performed in an inverse order.

The control signals associated with TX power ramping are shown in the figure below. In this example, the transmission is initiated with the rising edge of pin 11 (SLP\_TR). The radio transceiver state changes from PLL\_ON to BUSY\_TX.

**Figure 7-2. TX Power Ramping Example (O-QPSK 250kb/s Mode)**

Using an external RF front-end, it may be required to adjust the start-up time of the external PA relative to the internal building blocks to optimize the overall PSD. This can be achieved using the RF\_CTRL\_0.PA\_LT bits.

For more details on actual TX power for each gain settings, see [Table 9-5](#).

**Table 7-3. Recommended Mapping of TX Power, Frequency Band, and PHY\_TX\_PWR (register 0x05).**

|                  |                                                                                                                                               | PHY_TX_PWR (register 0x05)                                                                                                                         |                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| TX Power Setting | 915MHz North American Band<br>PHY Modes: BPSK-40 (GC_TX_OFFSET=3), BPSK-40-ALT (GC_TX_OFFSET=3), OQPSK-SIN-RC-{250,500,1000} (GC_TX_OFFSET=2) | 868.3MHz European Band<br>PHY Modes: BPSK-20 (GC_TX_OFFSET=3), OQPSK-SIN-RC-{100,200,400} (GC_TX_OFFSET=2) OQPSK-RC-{100,200,400} (GC_TX_OFFSET=3) | 780MHz Chinese Band<br>PHY Modes: OQPSK-RC-{250,500,1000} (GC_TX_OFFSET=2) |

| 11               | 0xC0                                                                                                                                          | 0xA0                                                                                                                                               | 0xC1                                                                       |

| 10               | 0xC1                                                                                                                                          | 0x80                                                                                                                                               | 0xE3                                                                       |

| 9                | 0x80                                                                                                                                          | 0xE4                                                                                                                                               | 0xE4                                                                       |

| 8                | 0x82                                                                                                                                          | 0xE6                                                                                                                                               | 0xC5                                                                       |

| 7                | 0x83                                                                                                                                          | 0xE7                                                                                                                                               | 0xE7                                                                       |

| 6                | 0x84                                                                                                                                          | 0xE8                                                                                                                                               | 0xE8                                                                       |

| 5                | 0x40                                                                                                                                          | 0xE9                                                                                                                                               | 0xE9                                                                       |

| 4                | 0x86                                                                                                                                          | 0xEA                                                                                                                                               | 0xEA                                                                       |

| 3                | 0x00                                                                                                                                          | 0xCB                                                                                                                                               | 0xCB                                                                       |

| 2                | 0x01                                                                                                                                          | 0xCC                                                                                                                                               | 0xCC                                                                       |

| 1                | 0x02                                                                                                                                          | 0xCC                                                                                                                                               | 0xCD                                                                       |

| 0                | 0x03                                                                                                                                          | 0xAD                                                                                                                                               | 0xCE                                                                       |

| -1               | 0x04                                                                                                                                          | 0x47                                                                                                                                               | 0xCF                                                                       |

| -2               | 0x27                                                                                                                                          | 0x48                                                                                                                                               | 0xAF                                                                       |

| -3               | 0x05                                                                                                                                          | 0x49                                                                                                                                               | 0x26                                                                       |

| -4               | 0x07                                                                                                                                          | 0x29                                                                                                                                               | 0x27                                                                       |

| -5               | 0x08                                                                                                                                          | 0x90                                                                                                                                               | 0x28                                                                       |

| -6               | 0x91                                                                                                                                          | 0x91                                                                                                                                               | 0x29                                                                       |

.....continued

|                         |                                                                                                                                                          | PHY_TX_PWR (register 0x05)                                                                                                                                       |                                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| <b>TX Power Setting</b> | <b>915MHz North American Band</b><br><b>PHY Modes: BPSK-40 (GC_TX_OFFSET=3), BPSK-40-ALT (GC_TX_OFFSET=3), OQPSK-SIN-{250,500,1000} (GC_TX_OFFSET=2)</b> | <b>868.3MHz European Band</b><br><b>PHY Modes: BPSK-20 (GC_TX_OFFSET=3), OQPSK-SIN-RC-{100,200,400} (GC_TX_OFFSET=2) OQPSK-RC-{100,200,400} (GC_TX_OFFSET=3)</b> | <b>780MHz Chinese Band</b><br><b>PHY Modes: OQPSK-RC-{250,500,1000} (GC_TX_OFFSET=2)</b> |

| -7                      | 0x09                                                                                                                                                     | 0x93                                                                                                                                                             | 0x07                                                                                     |

| -8                      | 0x0B                                                                                                                                                     | 0x94                                                                                                                                                             | 0x08                                                                                     |

| -9                      | 0x0C                                                                                                                                                     | 0x2F                                                                                                                                                             | 0x09                                                                                     |

| -10                     | 0x0D                                                                                                                                                     | 0x30                                                                                                                                                             | 0x0A                                                                                     |

| -11                     | 0x0E                                                                                                                                                     | 0x31                                                                                                                                                             | 0x0B                                                                                     |

| -12                     | 0x0F                                                                                                                                                     | 0x0F                                                                                                                                                             | 0x0C                                                                                     |

| -13                     | 0x10                                                                                                                                                     | 0x10                                                                                                                                                             | 0x0D                                                                                     |

| -14                     | 0x11                                                                                                                                                     | 0x11                                                                                                                                                             | 0x0E                                                                                     |

| -15                     | 0x12                                                                                                                                                     | 0x12                                                                                                                                                             | 0x0F                                                                                     |

| -16                     | 0x13                                                                                                                                                     | 0x13                                                                                                                                                             | 0x10                                                                                     |

| -17                     | 0x14                                                                                                                                                     | 0x14                                                                                                                                                             | 0x11                                                                                     |

| -18                     | 0x15                                                                                                                                                     | 0x15                                                                                                                                                             | 0x13                                                                                     |

| -19                     | 0x16                                                                                                                                                     | 0x17                                                                                                                                                             | 0x14                                                                                     |

| -20                     | 0x17                                                                                                                                                     | 0x18                                                                                                                                                             | 0x15                                                                                     |

| -21                     | 0x19                                                                                                                                                     | 0x19                                                                                                                                                             | 0x16                                                                                     |

| -22                     | 0x1A                                                                                                                                                     | 0x1A                                                                                                                                                             | 0x17                                                                                     |

| -23                     | 0x1B                                                                                                                                                     | 0x1B                                                                                                                                                             | 0x18                                                                                     |

| -24                     | 0x1C                                                                                                                                                     | 0x1C                                                                                                                                                             | 0x19                                                                                     |

| -25                     | 0x1D                                                                                                                                                     | 0x1D                                                                                                                                                             | 0x1A                                                                                     |

## 7.4 Frame Buffer

The AT86RF212B contains a 128 byte dual port SRAM. One port is connected to the SPI interface, the other one to the internal transmitter and receiver modules. For data communication, both ports are independent and simultaneously accessible.

The Frame Buffer utilizes the SRAM address space 0x00 to 0x7F for RX and TX operation of the radio transceiver and can keep a single IEEE 802.15.4 RX or a single TX frame of maximum length at a time.

Frame Buffer access conflicts are indicated by an underrun interrupt IRQ\_6 (TRX\_UR).

**Note:** The IRQ\_6 (TRX\_UR) interrupt also occurs on the attempt to write frames longer than 127 octets to the Frame Buffer (overflow). In that case the content of the Frame Buffer cannot be guaranteed.

Frame Buffer access is only possible if the digital voltage regulator (DVREG) is turned on. This is valid in all device states except in SLEEP state. An access in P\_ON state is possible if pin 17 (CLKM) provides the 1MHz master clock.

#### 7.4.1 Data Management

Data in Frame Buffer (received data or data to be transmitted) remains valid as long as:

- No new frame or other data are written into the buffer over SPI

- No new frame is received (in any BUSY\_RX state)

- No state change into SLEEP state is made

- No RESET took place

By default, there is no protection of the Frame Buffer against overwriting. Therefore, if a frame is received during Frame Buffer read access of a previously received frame, interrupt IRQ\_6 (TRX\_UR) is issued and the stored data might be overwritten.

Even so, the old frame data can be read, if the SPI data rate is higher than the effective over air data rate. For a data rate of 250kb/s, a minimum SPI clock rate of 1MHz is recommended. Finally, the microcontroller should check the transferred frame data integrity by an FCS check.

To protect the Frame Buffer content against being overwritten by newly incoming frames, the radio transceiver state should be changed to PLL\_ON state after reception. This can be achieved by writing immediately the command PLL\_ON to the TRX\_CMD bits in the TRX\_STATE register (TRX\_STATE.TRX\_CMD) after receiving the frame, indicated by IRQ\_3 (TRX\_END). Alternatively, Dynamic Frame Buffer Protection can be used to protect received frames against overwriting. Both procedures do not protect the Frame Buffer from overwriting by the microcontroller.

In Extended Operating Mode during TX\_ARET operation the radio transceiver switches to receive state if an acknowledgement of a previously transmitted frame was requested. During this period, received frames are evaluated but not stored in the Frame Buffer. This allows the radio transceiver to wait for an acknowledgement frame and retry the frame transmission without writing the frame again.

A radio transceiver state change, except a transition to SLEEP state or a reset, does not affect the Frame Buffer content. If the radio transceiver is taken into SLEEP, the Frame Buffer is powered off and the stored data get lost.

#### 7.4.2 User accessible Frame Content

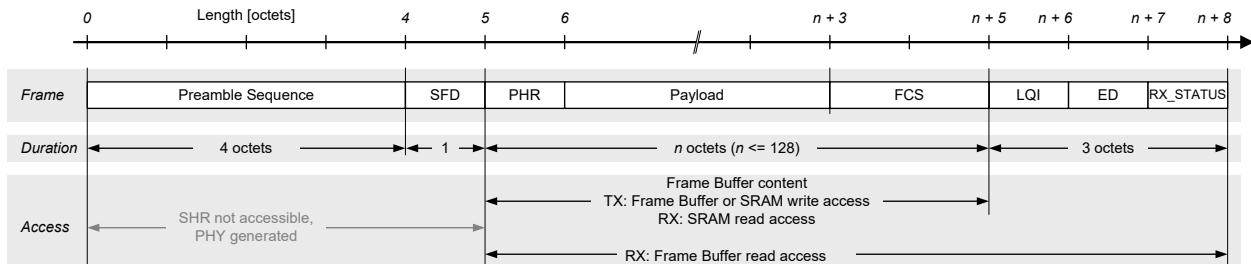

The AT86RF212B supports an IEEE 802.15.4 compliant frame format as shown in the figure below.

Figure 7-3. AT86RF212B Frame Structure

A frame comprises two sections, the radio transceiver internally generated SHR field and the user accessible part stored in the Frame Buffer. The SHR contains the preamble and the SFD field. The variable frame section contains the PHR and the PSDU including the FCS.

To access the data, follow the procedures described in *Frame Check Sequence (FCS)*.

The frame length information (PHR field) and the PSDU are stored in the Frame Buffer. During frame reception, the link quality indicator (LQI) value, the energy detection (ED) value, and the status information (RX\_STATUS) of a received frame are additionally stored. The radio transceiver appends these values to the frame data during Frame Buffer read access.

If the SRAM read access is used to read an RX frame, the frame length field (PHR) can be accessed at address zero. The SHR (except the SFD value used to generate the SHR) cannot be read by the microcontroller.

For frame transmission, the PHR and the PSDU needs to be stored in the Frame Buffer. The maximum Frame Buffer size supported by the radio transceiver is 128 bytes. If the TX\_AUTO\_CRC\_ON bit in the TRX\_CTRL\_1 register (TRX\_CTRL\_1.TX\_AUTO\_CRC\_ON) is set, the FCS field of the PSDU is replaced by the automatically calculated FCS during frame transmission.

To manipulate individual bytes of the Frame Buffer a SRAM write access can be used instead.

For non IEEE 802.15.4 compliant frames, the minimum frame length supported by the radio transceiver is one byte (Frame Length Field + one byte of data).

#### 7.4.3 Interrupt Handling

Access conflicts may occur when reading and writing data simultaneously at the two independent ports of the Frame Buffer, TX/RX BBP and SPI. These ports have their own address counter that points to the Frame Buffer's current address.

Access violations may cause data corruption and are indicated by IRQ\_6 (TRX\_UR) interrupt when using the Frame Buffer access mode. Note that access violations are not indicated when using the SRAM access mode.

While receiving a frame, first the data need to be stored in the Frame Buffer before reading it. This can be ensured by accessing the Frame Buffer at least eight symbols (BPSK) or two symbols (O-QPSK) after interrupt IRQ\_2 (RX\_START). When reading the frame data continuously, the SPI data rate shall be lower than the current TRX bit rate to ensure no underrun interrupt occurs. To avoid access conflicts and to simplify the Frame Buffer read access, Frame Buffer Empty indication may be used.

When writing data to the Frame Buffer during frame transmission, the SPI data rate shall be higher than the PHY data rate avoiding underrun. The first byte of the PSDU data must be available in the Frame Buffer before SFD transmission is complete, which takes 41 symbol periods for BPSK (one symbol PA ramp up + 40 symbols SHR) and 11 symbol periods for O-QPSK (one symbol PA ramp up + 10 symbols SHR) from the rising edge of pin 11 (SLP\_TR).

**Note:**

1. Interrupt IRQ\_6 (TRX\_UR) is valid two octets after IRQ\_2 (RX\_START).

2. If a Frame Buffer read access is not finished until a new frame is received, an IRQ\_6 (TRX\_UR) interrupt occurs. Nevertheless the old frame data can be read, if the SPI data rate is higher than the effective PHY data rate. A minimum SPI clock rate of 1MHz is recommended in this case. Finally, the microcontroller should check the integrity of the transferred frame data by calculating the FCS.

3. When writing data to the Frame Buffer during frame transmission, the SPI data rate shall be higher than the PHY data rate to ensure no under run interrupt. The first byte of the PSDU data must be available in the Frame Buffer before SFD transmission is complete.

## 7.5 Crystal Oscillator (XOSC) and Clock Output (CLKM)

The main crystal oscillator features are:

- 16 MHz amplitude-controlled crystal oscillator

- Fast settling time after leaving SLEEP state

- Configurable trimming capacitance array

- Configurable clock output (CLKM)

### 7.5.1 Overview

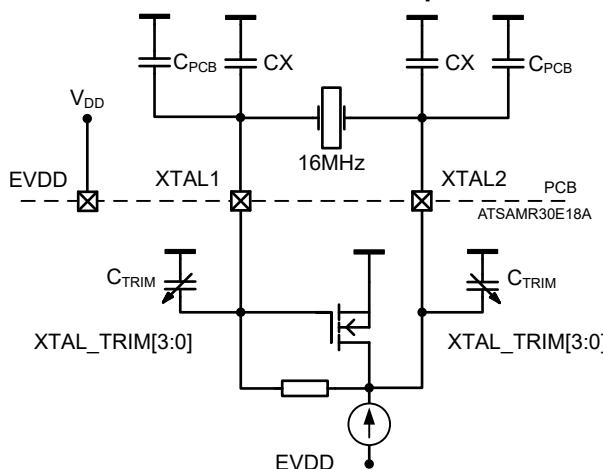

The internal 16 MHz crystal oscillator to the module generates the reference frequency for the AT86RF212B. All other internally generated frequencies of the radio transceiver are derived from this frequency. The XOSC\_CTRL register provides access to the control signals of the oscillator.

### 7.5.2 Integrated Oscillator Setup

Using the internal oscillator, the oscillation frequency depends on the load capacitance between the crystal pin 2 (XTAL1) and pin 1 (XTAL2) of SAMR30E18A. The total load capacitance  $C_L$  must be equal to the specified load capacitance of the crystal itself. It consists of the internal capacitors CX and parasitic capacitances connected to the XTAL nodes inside the module.

The figure below shows all parasitic capacitances, such as PCB stray capacitances and the pin input capacitance, summarized to  $C_{PAR}$ .

**Figure 7-4. Simplified XOSC Schematic with External Components**

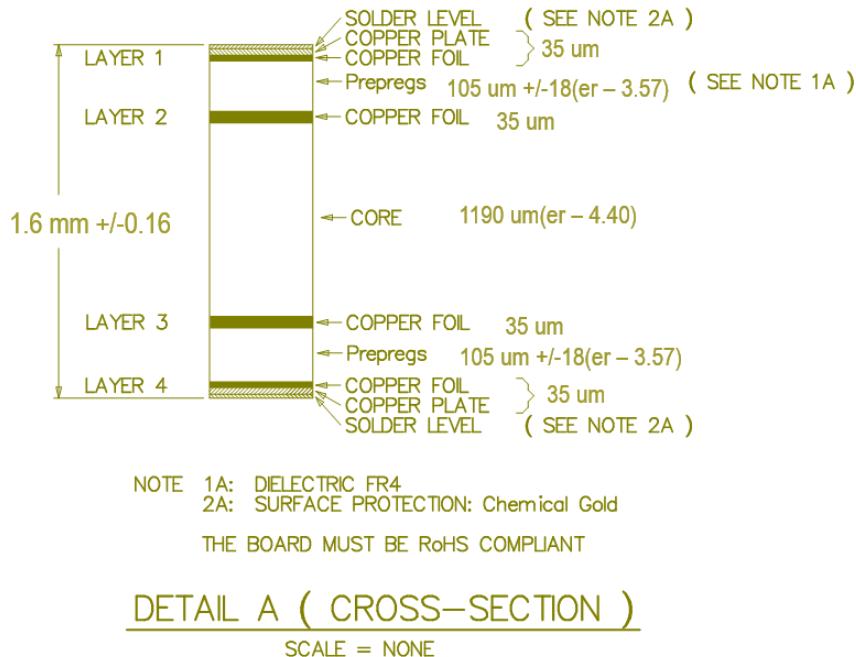

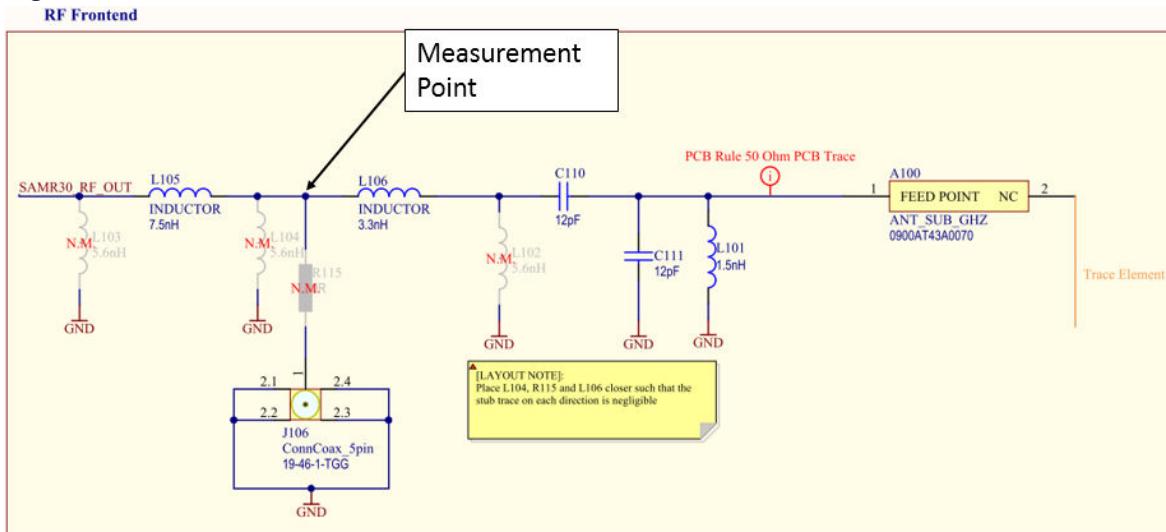

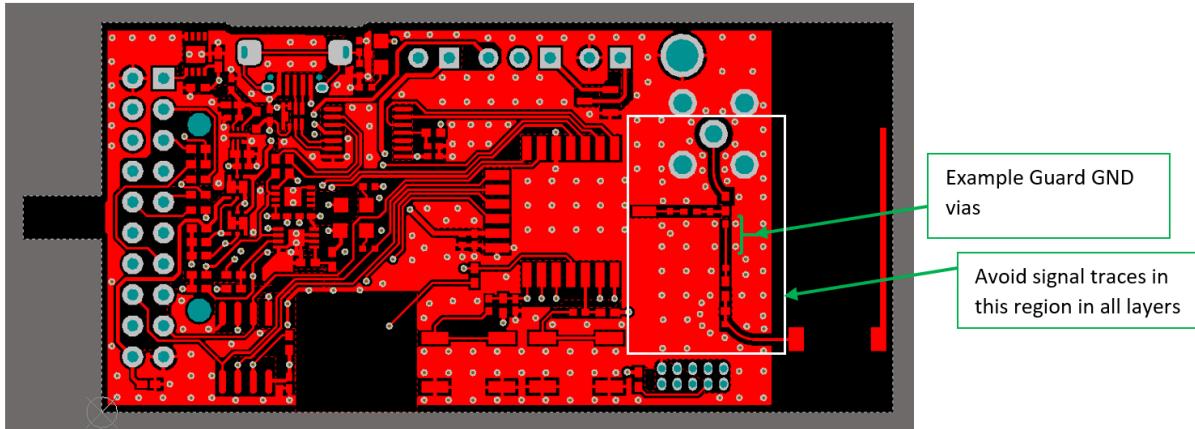

Additional internal trimming capacitors  $C_{TRIM}$  are available. Any value in the range from 0pF to 4.5pF with a 0.3pF resolution is selectable using the XTAL\_TRIM bits in the XOSC\_CTRL register (XOSC\_CTRL.XTAL\_TRIM). To calculate the total load capacitance, the following formula can be used: