Click [here](#) for production status of specific part numbers.

## MAX41461/MAX41462

## 300MHz–960MHz ASK Transmitter with I<sup>2</sup>C Interface

### General Description

The MAX41461/MAX41462 is a UHF sub-GHz ISM/SRD transmitter is designed to transmit On-Off Keying (OOK) or Amplitude-Shift Keying (ASK) data in the 286MHz to 960MHz frequency range. It integrates a fractional phase-locked-loop (PLL), so a single, low-cost crystal can be used to generate commonly used world-wide sub-GHz frequencies. The fast response time of the PLL allows for frequency-hopping spread spectrum protocols for increased range and security. The chip also features pre-set modes with pin-selectable frequencies so that only one wire is required for external microcontroller interface. The only frequency-dependent components required are for the external antenna matching network. Optionally, the device can be put into programmable mode and programmed using an I<sup>2</sup>C interface. The crystal-based architecture of the MAX41461/MAX41462 eliminates many of the common problems with SAW-based transmitters by providing greater modulation depth, faster frequency settling, higher tolerance of the transmit frequency, and reduced temperature dependence. A clock-out signal at 800kHz is also provided.

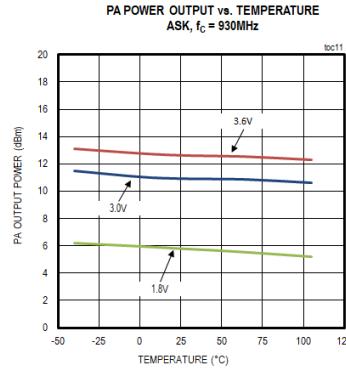

The MAX41461/MAX41462 provides output power up to +13dBm into a 50Ω load while drawing < 8mA (Manchester coded). The output load can be adjusted to increase power up to +16dBm, and a PA boost mode can be enabled at frequencies above 850MHz to compensate for losses. The PA output power can also be controlled using programmable register settings in I<sup>2</sup>C mode.

The MAX41461/MAX41462 also features single-supply operation from +1.8V to +3.6V. The device has an auto-shutdown feature to extend battery life and a fast oscillator wake-up with data activity detection.

The MAX41461/MAX41462 is available in a 10-pin μMAX package and is specified over the -40°C to +105°C extended temperature range. The MAX41461/MAX41462 has an ESD rating of 2.5kV HBM.

### Applications

- Building Automation and Security

- Wireless Sensors and Alarms

- Remote and Passive Keyless Entry (RKE/PKE)

- Tire Pressure Monitoring Systems (TPMS)

- Automatic Meter Reading (AMR)

- Garage Door Openers (GDO)

- Radio Control Toys

- Internet of Things (IoT)

### Benefits and Features

- Low Implementation Cost

- Bits-to-RF Single Wire Operation

- Low Bill-of-Materials (BOM)

- Uses Single, Low-Cost, 16MHz Crystal

- Small 3mm x 3mm μMAX-10 Package

- Increased Range, Data Rates, and Security

- Up to +16dBm PA Output Power

- Fast Frequency Switching for FHSS/DSSS

- Fast-On Oscillator: < 250μs Startup Time

- Up to 200kbps NRZ Data Rate

- Extend Battery Life with Low Supply Current

- < 8mA ASK Manchester Coded

- Selectable Standby and Shutdown Modes

- Auto Shutdown at < 20nA (typ) Current

- Ease of Use

- Pin Selectable 300MHz–928MHz Frequencies

- Pin Compatible ASK and FSK Versions

- +1.8V to +3.6V Single-Supply Operation

- Fully Programmable with 400kHz/1MHz I<sup>2</sup>C Interface

*Ordering Information* appears at end of data sheet.

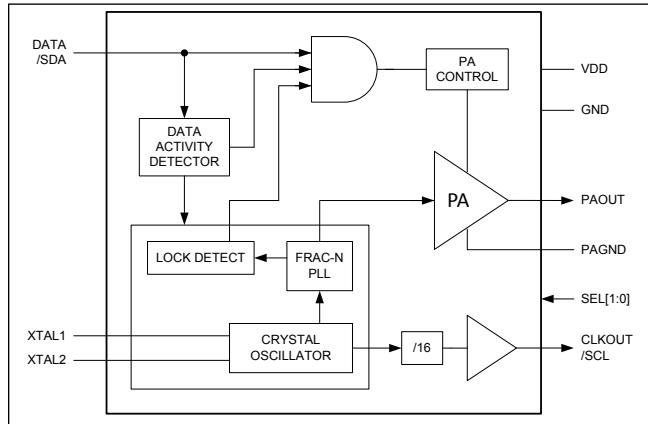

### Simplified Block Diagram

**Absolute Maximum Ratings**

|                                                                                             |                                   |                                      |                 |

|---------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------|-----------------|

| V <sub>DD</sub> to GND.....                                                                 | -0.3V to +4V                      | Junction Temperature .....           | +150°C          |

| All Others Pins to GND.....                                                                 | -0.3V to (V <sub>DD</sub> + 0.3)V | Storage Temperature Range .....      | -60°C to +150°C |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C, derate 5.6mW/°C<br>above +70°C) ..... | 444.4mW                           | Lead Temperature (reflow) .....      | +300°C          |

| Operating Temperature Range .....                                                           | -40°C to +105°C                   | Soldering Temperature (reflow) ..... | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Information****10 µMAX (similar to 10 TSSOP)**

|                                                        |                         |

|--------------------------------------------------------|-------------------------|

| Package Code                                           | U10+2                   |

| Outline Number                                         | <a href="#">21-0061</a> |

| Land Pattern Number                                    | <a href="#">90-0330</a> |

| <b>Thermal Resistance, Single-Layer Board:</b>         |                         |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 180°C/W                 |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 36°C/W                  |

| <b>Thermal Resistance, Four-Layer Board:</b>           |                         |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 113.1°C/W               |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 36°C/W                  |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

## Electrical Characteristics

(*Typical Application Circuit*, all RF inputs and outputs are referenced to  $50\Omega$ ,  $V_{DD} = +1.8V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+105^\circ C$ ,  $P_{OUT} = +13\text{dBm}$  for 300MHz–450MHz or  $+11\text{dBm}$  for 863MHz–928MHz,  $\text{PA\_BOOST} = 0$ , unless otherwise noted. Typical values are at  $V_{DD} = +3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted. (Note 1))

| PARAMETER                    | SYMBOL      | CONDITIONS                                                                            | MIN                                                                                                   | TYP  | MAX | UNITS         |

|------------------------------|-------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----|---------------|

| <b>DC CHARACTERISTICS</b>    |             |                                                                                       |                                                                                                       |      |     |               |

| Operating Current            | $I_{DD}$    | $V_{DATA}$ at 50% duty cycle (ASK) (Note 3, Note 4)                                   | $f_{RF} = 315\text{MHz}$                                                                              | 7    | 12  | mA            |

|                              |             |                                                                                       | $f_{RF} = 434\text{MHz}$                                                                              | 8    | 12  |               |

|                              |             |                                                                                       | $f_{RF} = 863\text{MHz} - 928\text{MHz}$                                                              | 10   | 19  |               |

|                              |             |                                                                                       | $f_{RF} = 315\text{MHz}$ , $P_{OUT} = 16\text{dBm}$ (Note 5)                                          | 24   |     |               |

|                              |             |                                                                                       | $f_{RF} = 434\text{MHz}$ , $P_{OUT} = 16\text{dBm}$ (Note 5)                                          | 26   |     |               |

|                              |             |                                                                                       | $f_{RF} = 863\text{MHz} - 928\text{MHz}$ , $P_{OUT} = 16\text{dBm}$ , $\text{PA\_BOOST} = 1$ (Note 5) | 45   |     |               |

|                              |             | $V_{DATA}$ at 50% duty cycle (ASK), Low Phase Noise mode (Note 3, Note 4)             | $f_{RF} = 315\text{MHz}$                                                                              | 9.5  |     |               |

|                              |             |                                                                                       | $f_{RF} = 434\text{MHz}$                                                                              | 10.5 |     |               |

|                              |             |                                                                                       | $f_{RF} = 863\text{MHz} - 928\text{MHz}$                                                              | 12.8 |     |               |

|                              |             | PA off (Note 2)                                                                       | $f_{RF} = 315\text{MHz}$                                                                              | 2    | 3   |               |

|                              |             |                                                                                       | $f_{RF} = 434\text{MHz}$                                                                              | 2    | 3   |               |

|                              |             |                                                                                       | $f_{RF} = 863\text{MHz} - 928\text{MHz}$                                                              | 3    | 4   |               |

|                              |             | PA off, Low Phase Noise mode (Note 2)                                                 | $f_{RF} = 315\text{MHz}$                                                                              | 4    |     |               |

|                              |             |                                                                                       | $f_{RF} = 434\text{MHz}$                                                                              | 4    |     |               |

|                              |             |                                                                                       | $f_{RF} = 863\text{MHz} - 928\text{MHz}$                                                              | 5    |     |               |

| Supply Voltage               | $V_{DD}$    | $\text{PA\_BOOST} = 0$                                                                |                                                                                                       | 1.8  | 3   | 3.6           |

|                              |             | $\text{PA\_BOOST} = 1$                                                                |                                                                                                       | 1.8  | 2.7 | 3.0           |

| Standby Current              | $I_{STDBY}$ | Crystal oscillator on, everything off.                                                | $T_A = 25^\circ C$                                                                                    | 200  | 500 | $\mu\text{A}$ |

|                              |             |                                                                                       | $T_A = 105^\circ C$                                                                                   | 250  |     |               |

| Shutdown Current             | $I_{SHDN}$  | Everything off                                                                        | $T_A = 25^\circ C$                                                                                    | 19   | 100 | nA            |

| <b>MODULATION PARAMETERS</b> |             |                                                                                       |                                                                                                       |      |     |               |

| ASK Modulation Depth         |             | Supply current and output power are greatly dependent on board layout and PAOUT match |                                                                                                       |      | 70  | $\text{dB}$   |

| Maximum NRZ Data Rate        |             |                                                                                       |                                                                                                       |      | 200 | kbps          |

**Electrical Characteristics (continued)**

(*Typical Application Circuit*, all RF inputs and outputs are referenced to 50Ω, V<sub>DD</sub> = +1.8V to +3.6V, T<sub>A</sub> = -40°C to +105°C, P<sub>OUT</sub> = +13dBm for 300MHz–450MHz or +11dBm for 863MHz–928MHz, PA\_BOOST = 0, unless otherwise noted. Typical values are at V<sub>DD</sub> = +3V, T<sub>A</sub> = +25°C, unless otherwise noted. (Note 1))

| PARAMETER                          | SYMBOL           | CONDITIONS                                                                                                                          | MIN                                 | TYP                                | MAX | UNITS             |

|------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------|-----|-------------------|

| <b>POWER AMPLIFIER</b>             |                  |                                                                                                                                     |                                     |                                    |     |                   |

| Output Power                       | P <sub>OUT</sub> | f <sub>RF</sub> = 300MHz–450MHz (Note 4)                                                                                            | 13                                  |                                    |     | dBm               |

|                                    |                  | f <sub>RF</sub> = 300MHz–450MHz (Note 4, Note 5)                                                                                    | 17                                  |                                    |     |                   |

|                                    |                  | f <sub>RF</sub> = 863MHz–928MHz (Note 4)                                                                                            | 11                                  |                                    |     |                   |

|                                    |                  | f <sub>RF</sub> = 863MHz–928MHz (Note 4, Note 5), PA_BOOST = 1                                                                      | 16                                  |                                    |     |                   |

| Maximum Carrier Harmonics          |                  | PA_BOOST = 0. Supply current, output power, and harmonics are dependent on board layout and PAOUT match.                            |                                     | -24                                |     | dBc               |

| <b>PLL</b>                         |                  |                                                                                                                                     |                                     |                                    |     |                   |

| Frequency Range                    |                  | Low Current mode (default)                                                                                                          | 286                                 | 960                                |     | MHz               |

|                                    |                  | Low Phase Noise mode, LODIV = DIV12                                                                                                 | 286.7                               | 320                                |     |                   |

|                                    |                  | Low Phase Noise mode, LODIV = DIV8                                                                                                  | 425                                 | 480                                |     |                   |

|                                    |                  | Low Phase Noise mode, LODIV = DIV4                                                                                                  | 860                                 | 960                                |     |                   |

| PLL Phase Noise                    |                  | f <sub>RF</sub> = 315MHz, Low Current mode (default)                                                                                | f <sub>OFFSET</sub> = 200kHz        | -82                                |     | dBc/Hz            |

|                                    |                  |                                                                                                                                     | f <sub>OFFSET</sub> = 1MHz          | -90                                |     |                   |

|                                    |                  | f <sub>RF</sub> = 434MHz, Low Current mode (default)                                                                                | f <sub>OFFSET</sub> = 200kHz        | -80                                |     |                   |

|                                    |                  |                                                                                                                                     | f <sub>OFFSET</sub> = 1MHz          | -90                                |     |                   |

|                                    |                  | f <sub>RF</sub> = 915MHz, Low Phase Noise mode                                                                                      | f <sub>OFFSET</sub> = 200kHz        | -82                                |     |                   |

|                                    |                  |                                                                                                                                     | f <sub>OFFSET</sub> = 1MHz          | -104                               |     |                   |

| LO Divider Settings                |                  |                                                                                                                                     |                                     | 4                                  |     |                   |

|                                    |                  |                                                                                                                                     |                                     | 8                                  |     |                   |

|                                    |                  |                                                                                                                                     |                                     | 12                                 |     |                   |

| Minimum Synthesizer Frequency Step |                  |                                                                                                                                     |                                     | f <sub>XTAL</sub> /2 <sup>16</sup> |     | Hz                |

| Reference Spur                     |                  | f <sub>RF</sub> = 315MHz                                                                                                            | f <sub>RF</sub> ± f <sub>XTAL</sub> | -67                                |     | dBc               |

|                                    |                  | f <sub>RF</sub> = 434MHz                                                                                                            | f <sub>RF</sub> ± f <sub>XTAL</sub> | -60                                |     |                   |

|                                    |                  | f <sub>RF</sub> = 868MHz                                                                                                            | f <sub>RF</sub> ± f <sub>XTAL</sub> | -57                                |     |                   |

|                                    |                  | f <sub>RF</sub> = 915MHz                                                                                                            | f <sub>RF</sub> ± f <sub>XTAL</sub> | -56                                |     |                   |

| Reference Frequency Input Level    |                  |                                                                                                                                     |                                     | 500                                |     | mV <sub>P-P</sub> |

| Frequency Switching Time           |                  | 26MHz frequency step, 902MHz to 928MHz band, time from end of register write to frequency settled to within 5kHz of desired carrier |                                     | 50                                 |     | μs                |

| Loop Bandwidth                     | LBW              |                                                                                                                                     |                                     | 300                                |     | kHz               |

**Electrical Characteristics (continued)**

(*Typical Application Circuit*, all RF inputs and outputs are referenced to  $50\Omega$ ,  $V_{DD} = +1.8V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+105^\circ C$ ,  $P_{OUT} = +13dBm$  for 300MHz–450MHz or  $+11dBm$  for 863MHz–928MHz,  $PA\_BOOST = 0$ , unless otherwise noted. Typical values are at  $V_{DD} = +3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted. (Note 1))

| PARAMETER                                       | SYMBOL          | CONDITIONS                                             |                 | MIN  | TYP             | MAX  | UNITS   |

|-------------------------------------------------|-----------------|--------------------------------------------------------|-----------------|------|-----------------|------|---------|

| LO Frequency Divider Range                      | N               |                                                        |                 | 11   |                 | 72   |         |

| Turn-On Time of PLL                             | $t_{PLL}$       | $f_{RF} = 315MHz$                                      |                 | 30   |                 |      | $\mu s$ |

|                                                 |                 | $f_{RF} = 915MHz$                                      |                 | 90   |                 |      |         |

| <b>CRYSTAL OSCILLATOR</b>                       |                 |                                                        |                 |      |                 |      |         |

| Crystal Frequency                               | $f_{XTAL}$      | Recommended value (Note 3)                             |                 | 12.8 | 16              | 19.2 | MHz     |

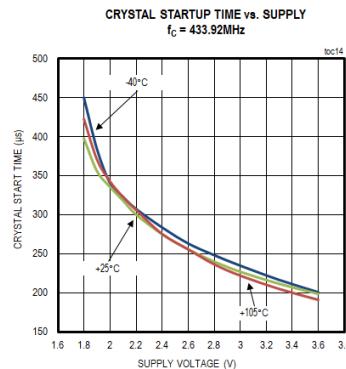

| Crystal Oscillator Startup Time                 | $t_{XO}$        | See <i>Preset Mode Transmission</i> section            |                 | 243  |                 |      | $\mu s$ |

| Frequency Pulling by $V_{DD}$                   |                 |                                                        |                 | 3    |                 |      | ppm/V   |

| Crystal Input Capacitance                       | $C_X$           | Internal capacitance of XTAL1 and XTAL2 pins to ground |                 | 12   |                 |      | pF      |

| <b>CMOS INPUT/OUTPUT</b>                        |                 |                                                        |                 |      |                 |      |         |

| Input Low Voltage                               | $V_{IL}$        | SCL/SDA                                                | 1.8V compatible |      | 0.36            |      | V       |

|                                                 | $V_{IL\_SEL}$   | SEL0/SEL1                                              |                 |      | 0.1 x $V_{DD3}$ |      |         |

| Input High Voltage                              | $V_{IH}$        | SCL/SDA                                                | 1.8V compatible | 1.44 |                 |      | V       |

|                                                 | $V_{IH\_SEL}$   | SEL0/SEL1                                              |                 |      | 0.9 x $V_{DD3}$ |      |         |

| Input Current                                   | $I_{IL}/I_{IH}$ |                                                        |                 |      | $\pm 10$        |      | $\mu A$ |

| Output Low Voltage                              | $V_{OL}$        | $I_{SINK} = 650\mu A$                                  |                 |      | 0.25            |      | V       |

| Output High Voltage                             | $V_{OH}$        | $I_{SOURCE} = 350\mu A$                                |                 |      | $V_{DD} - 0.25$ |      | V       |

| Maximum Capacitance at SEL0/SEL1 Pins           | $C_{L\_SEL}$    |                                                        |                 |      | 10              |      | pF      |

| Maximum Load Capacitance at CLKOUT/SDO Pin      | $C_{LOAD}$      |                                                        |                 |      | 10              |      | pF      |

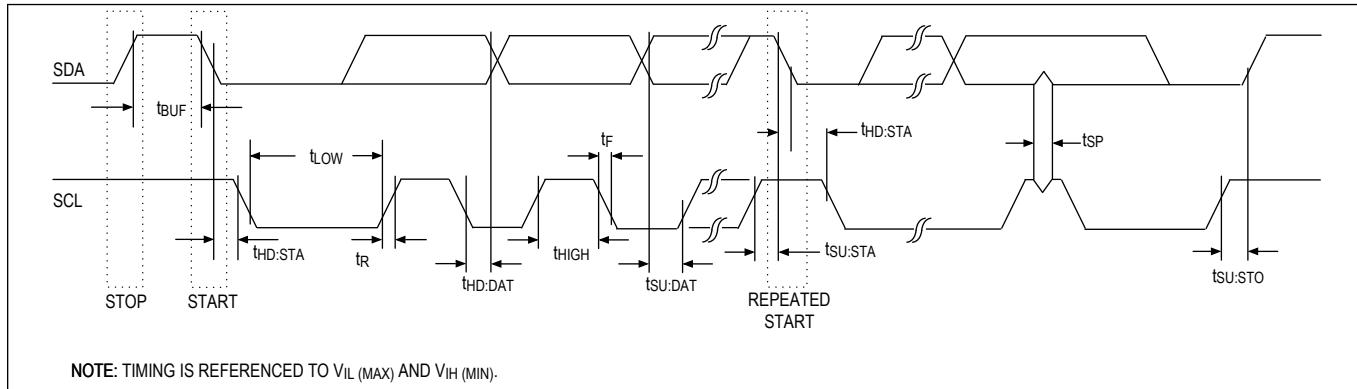

| <b>SERIAL INTERFACE (FIGURE 1)</b>              |                 |                                                        |                 |      |                 |      |         |

| SCL Clock Frequency                             | $f_{SCL}$       |                                                        |                 | 400  | 1000            |      | kHz     |

| Bus Free Time Between STOP and START Conditions | $t_{BUF}$       |                                                        |                 | 500  |                 |      | ns      |

| Hold Time (Repeated) START Condition            | $t_{HD:STA}$    |                                                        |                 | 260  |                 |      | ns      |

| Low Period of SCL                               | $t_{LOW}$       |                                                        |                 | 500  |                 |      | ns      |

| High Period of SCL                              | $t_{HIGH}$      |                                                        |                 | 260  |                 |      | ns      |

| Data Hold Time                                  | $t_{HD:DAT}$    | Receive                                                |                 | 0    | 150             |      | ns      |

|                                                 |                 | Transmit                                               |                 | 0    |                 |      |         |

| Data Setup Time                                 | $t_{SU:DAT}$    |                                                        |                 | 50   |                 |      | ns      |

## Electrical Characteristics (continued)

(*Typical Application Circuit*, all RF inputs and outputs are referenced to  $50\Omega$ ,  $V_{DD} = +1.8V$  to  $+3.6V$ ,  $T_A = -40^\circ C$  to  $+105^\circ C$ ,  $P_{OUT} = +13dBm$  for 300MHz–450MHz or  $+11dBm$  for 863MHz–928MHz,  $PA\_BOOST = 0$ , unless otherwise noted. Typical values are at  $V_{DD} = +3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted. (Note 1))

| PARAMETER             | SYMBOL       | CONDITIONS | MIN                         | TYP | MAX | UNITS |

|-----------------------|--------------|------------|-----------------------------|-----|-----|-------|

| Start Setup Time      | $t_{SU:STA}$ |            | 260                         |     |     | ns    |

| SDA and SCL Rise Time | $t_R$        |            |                             | 120 |     | ns    |

| SDA and SCL Fall Time | $t_F$        |            | $20 \times$<br>$V_{IO}/5.5$ | 120 |     | ns    |

| Stop Setup Time       | $t_{SU:STO}$ |            | 260                         |     |     | ns    |

| Noise Spike Reject    | $t_{SP}$     |            | 25                          |     |     | ns    |

**Note 1:** Supply current, output power and efficiency are greatly dependent on board layout and PA output match.

**Note 2:** 100% tested at  $T_A = +25^\circ C$ . Limits over operating temperature and relevant supply voltage are guaranteed by design and characterization over temperature.

**Note 3:** Guaranteed by design and characterization. Not production tested.

**Note 4:** Typical values are average, peak power is 3dB higher.

**Note 5:** Using high output power match, see [Table 3](#).

Figure 1. Serial Interface Timing Diagram

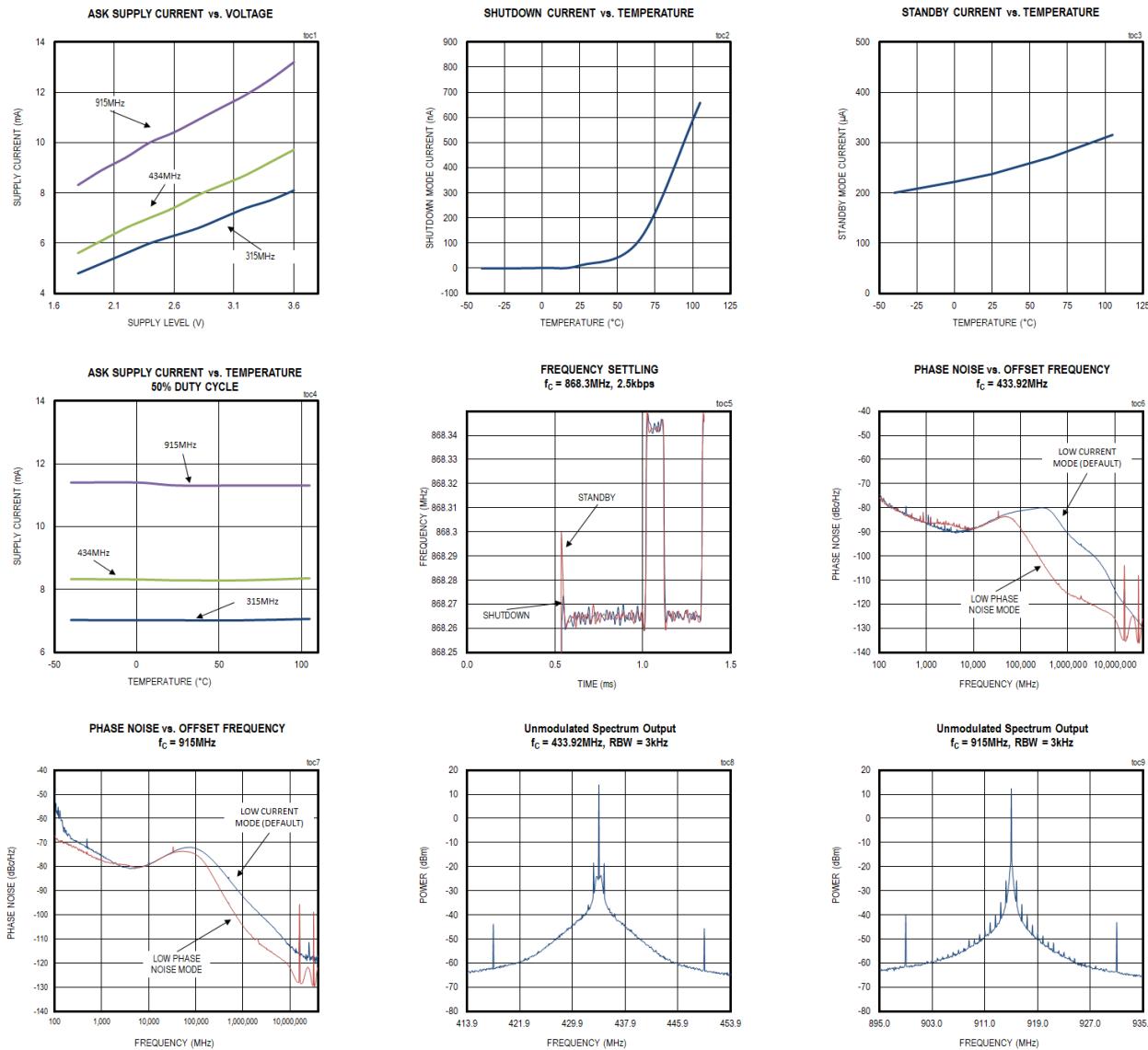

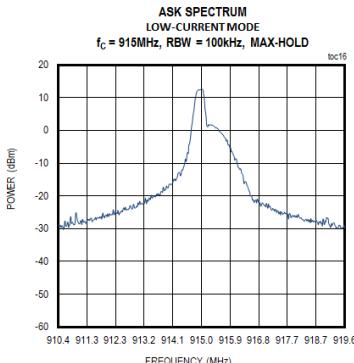

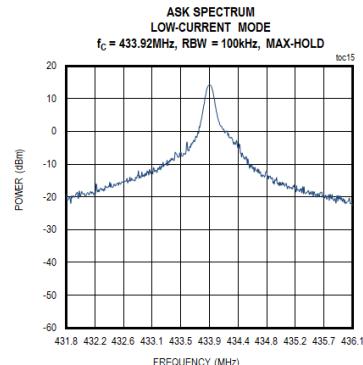

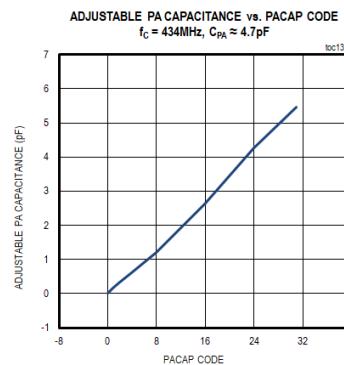

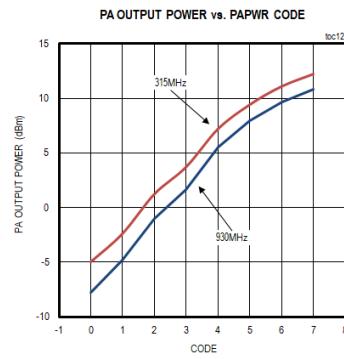

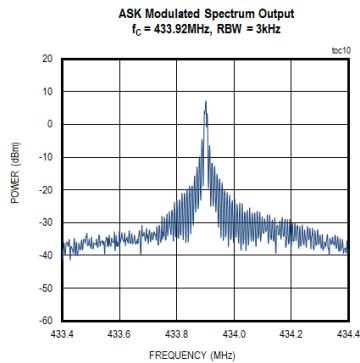

## Typical Operating Characteristics

(Typical Application Circuit, RF output terminated to 50Ω. Typical values are at  $V_{DD} = +3V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Typical Application Circuit, RF output terminated to 50Ω. Typical values are at  $V_{DD} = +3V$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

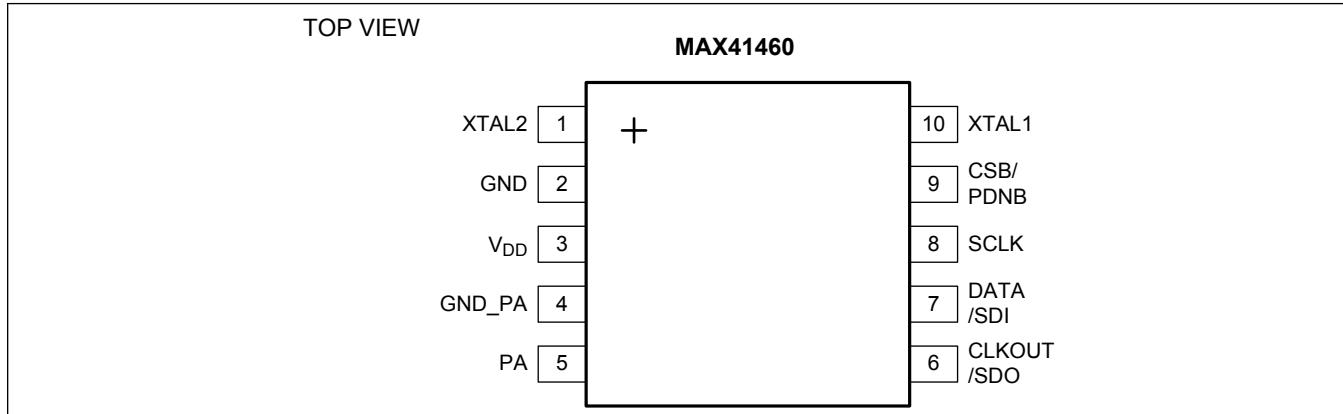

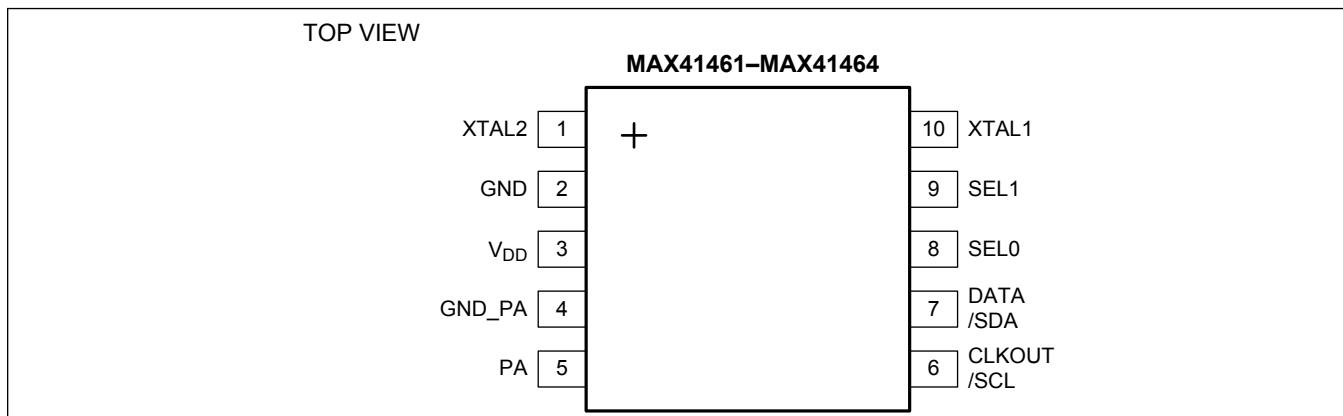

## Pin Configurations

### 10 $\mu$ MAX

### 10 $\mu$ MAX

## Pin Description

| PIN             |                           | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX4146<br>0    | MAX4146<br>1–MAX41<br>464 |      |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XTAL2           | XTAL2                     | 1    | Second Crystal Input. See <i>Crystal Oscillator</i> section.                                                                                                                                                                                                                                                                                                                                                                |

| GND             | GND                       | 2    | Ground. Connect to system ground.                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | V <sub>DD</sub>           | 3    | Supply Voltage. Bypass to GND with a 100nF capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                       |

| GND_PA          | GND_PA                    | 4    | Ground for the Power Amplifier (PA). Connect to system ground.                                                                                                                                                                                                                                                                                                                                                              |

| PA              | PA                        | 5    | Power-Amplifier Output. The PA output requires a pullup inductor to the supply voltage, which can be part of the output-matching network to an antenna.                                                                                                                                                                                                                                                                     |

| CLKOUT/<br>SDO  | CLKOUT/<br>SCL            | 6    | MAX41460: Buffered Clock Output or SPI Data Output.<br>MAX41461–MAX41464: Buffered Clock Output. I <sup>2</sup> C clock input for register programming when in Serial Interface Mode (SEL0 and SEL1 are unconnected or HIZ). The frequency of CLKOUT is 800kHz when not in Program mode.                                                                                                                                    |

| DATA/SDI        | DATA/<br>SDA              | 7    | MAX41460: Data Input. SPI bus serial data input for register programming when CSB is at logic-low.<br>MAX41461–MAX41464: Data Input. I <sup>2</sup> C serial data input for register programming when in Serial Interface mode (SEL0 and SEL1 are unconnected or HIZ). When not in Program mode, DATA also controls the power-up state (see the <i>Auto-Shutdown in Preset Mode</i> section in the appropriate data sheet). |

| SCLK            | SEL0                      | 8    | MAX41460: SPI Bus Serial Clock Input.<br>MAX41461–MAX41464: Three-state Mode Input. See <i>Preset Modes</i> section in the appropriate data sheet for details. For three-state input open, the impedance on the pin must be greater than 1MΩ.                                                                                                                                                                               |

| CSB             | SEL1                      | 9    | MAX41460: SPI Bus Chip Enable. Active Low.<br>MAX41461–MAX41464: Three-state Mode Input. See <i>Preset Modes</i> section in the appropriate data sheet for details. For three-state input open, the impedance on the pin must be greater than 1MΩ.                                                                                                                                                                          |

| XTAL1           | XTAL1                     | 10   | First Crystal Input. See <i>Crystal Oscillator</i> section.                                                                                                                                                                                                                                                                                                                                                                 |

## Detailed Description

The MAX41461/MAX41462 is part of the MAX4146x family of UHF sub-GHz ISM/SDR transmitters designed to transmit ASK data in the 286MHz to 960MHz frequency range. The MAX4146x family is available in the following versions.

**Table 1. MAX4146x Versions**

| VERSION  | MODULATION AND INTERFACE        | PRESET FREQUENCIES (MHz)                           |

|----------|---------------------------------|----------------------------------------------------|

| MAX41460 | ASK/FSK with SPI                | No presets, programmable through SPI               |

| MAX41461 | ASK (optional I <sup>2</sup> C) | 315/318/319.51/345/433.42/433.92/908/915           |

| MAX41462 | ASK (optional I <sup>2</sup> C) | 315/433/433.92/434/868/868.3/868.35/868.5          |

| MAX41463 | FSK (optional I <sup>2</sup> C) | 315/433.42/433.92/908/908.42/908.8/915/916         |

| MAX41464 | FSK (optional I <sup>2</sup> C) | 315/433.92/868.3/868.35/868.42/868.5/868.95/869.85 |

The MAX41460 uses an SPI programming interface. The MAX41461–MAX41464 feature an I<sup>2</sup>C interface, as well as preset modes (pin-selectable output frequencies using only one crystal frequency). No programming is required in preset modes and only a single-input data interface to an external microcontroller is needed. The MAX41461/MAX41462 parts are identical when put in I<sup>2</sup>C programming mode. All MAX4146x versions are fully programmable for all output frequencies, as described in the [Electrical Characteristics](#) table. The only frequency-dependent components required are for the the external antenna match.

The crystal-based architecture of the MAX41461/MAX41462 provides greater modulation depth, faster frequency settling, higher tolerance of the transmit frequency, and reduced temperature dependence. It integrates a fractional phase-locked-loop (PLL); so a single, low-cost crystal can be used to generate commonly used world-wide sub-GHz frequencies. A buffered clock-out signal make the device compatible with almost any microcontroller or code-hopping generator.

The MAX41461/MAX41462 provides +13dBm output power into a 50Ω load at 315MHz using an integrated high efficiency power amplifier (PA). The output load can be adjusted to increase power up to +16dBm and a PA boost mode can be enabled at frequencies above 850MHz to compensate for losses. The PA output power can also be controlled using programmable register settings. The MAX41461/MAX41462 feature fast oscillator wake-up upon data activity detection and has an auto-shutdown feature to extend battery life.

The MAX41461/MAX41462 operates at a supply voltage of +1.8V to +3.6V and is available in a 10-pin μMAX package that is specified over the -40°C to +105°C extended temperature range.

### Preset Modes

The MAX41461/MAX41462 contain preset settings depending on the state of pins SEL1 and SEL0. All presets must use a 16MHz crystal. The frequency of the CLKOUT pin is always 800kHz.

**Table 2. Programming and Preset Modes**

| SEL1 STATE      | SEL0 STATE      | MAX41461              | MAX41462              |

|-----------------|-----------------|-----------------------|-----------------------|

| Ground          | Ground          | I <sup>2</sup> C Mode | I <sup>2</sup> C Mode |

| Ground          | Open            | 315                   | 315                   |

| Ground          | V <sub>DD</sub> | 318                   | 433.92                |

| Open            | Ground          | 319.51                | 433                   |

| Open            | Open            | 345                   | 434                   |

| Open            | V <sub>DD</sub> | 908                   | 868.3                 |

| V <sub>DD</sub> | Ground          | 915                   | 868                   |

| V <sub>DD</sub> | Open            | 433.92                | 868.5                 |

| V <sub>DD</sub> | V <sub>DD</sub> | 433.42                | 868.35                |

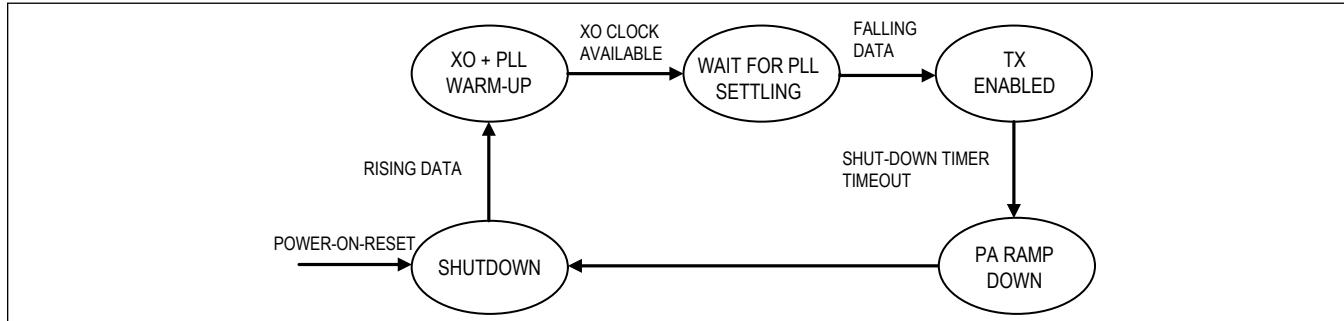

### Preset Mode Transmission

The wake-up of the device is as follows:

- 1) The microcontroller sends a wake-up pulse on DATA. The duration of the wake-up pulse should be longer than  $t_{XO} + t_{PLL}$ .

- 2) After the falling edge of wake-up pulse, the microcontroller should wait for at least  $t_{TX}$  time and start data transmission. In preset mode,  $t_{TX} = 10\mu s$ .

- 3) CLKOUT is generated 80 $\mu s$  after internal 3.2MHz clock is available.

Figure 2. Wake-Up Timing Diagram for Preset Mode

### Auto-Shutdown in Preset Mode

The MAX41461/MAX41462 in preset mode has an automatic shutdown feature that places the device in low-power shutdown mode if the DATA input stays at logic 0 for a wait time equal to  $2^{14}$  cycles of the internal 3.2MHz clock. This equates to a wait time of approximately 5.1ms.

When the device is in automatic shutdown, a pulse on DATA initiates the warm up of the crystal and PLL. See [Startup](#) section for requirements on the wake-up pulse.

When the device is operating, each occurrence of logic 1 on the data line resets an internal counter to zero and it begins to count again. If the counter reaches the end-of-count, the device enters shutdown mode.

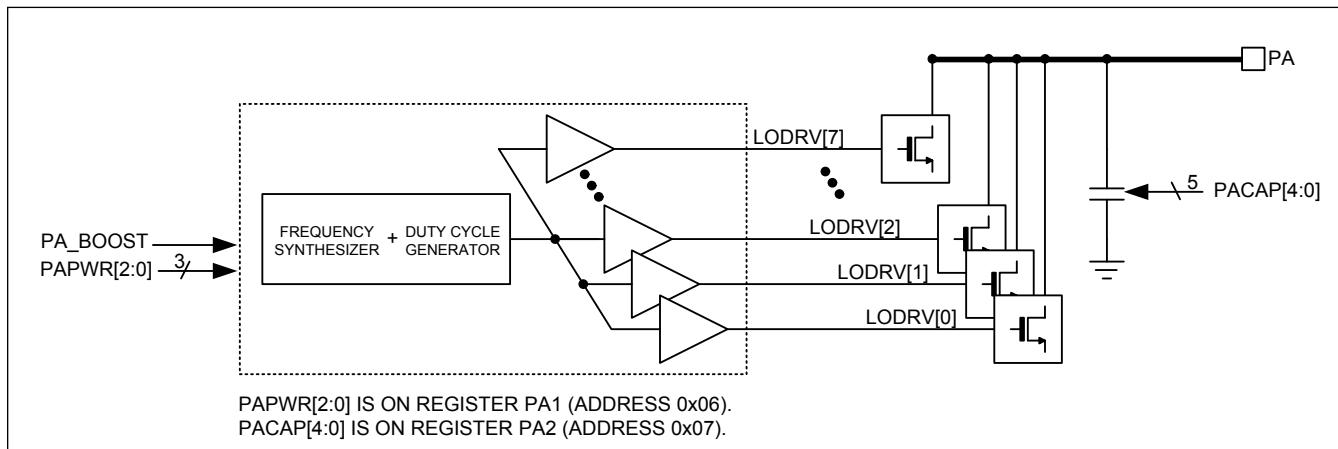

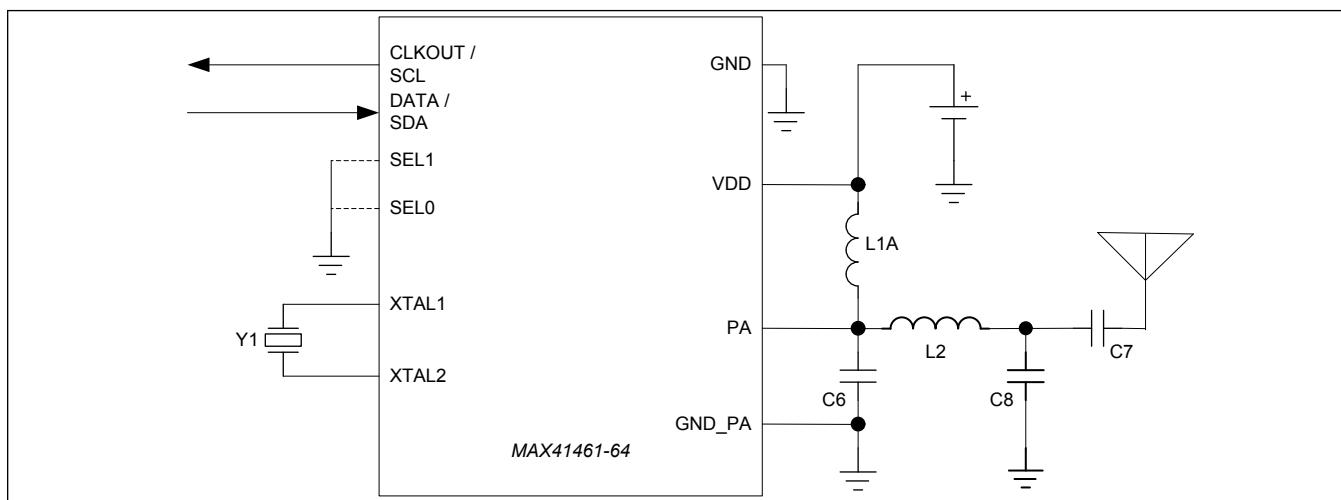

### Power Amplifier

The MAX41461/MAX41462 PA is a high-efficiency, open-drain switching-mode amplifier. In a switching-mode amplifier, the gate of the final-stage FET is driven with a 25% duty-cycle square wave at the transmit frequency. The PA also has an internal set of capacitors that can be switched in and out to present different capacitance values at the PA output using the PACAP[4:0] register values. This allows extra flexibility for tuning the output matching network. When the matching network is tuned correctly, the output FET resonates the attached tank circuit (pullup inductor from PA to V<sub>DD</sub>) with a minimum amount of power dissipated in the FET. With a proper output-matching network, the PA can drive a wide range of antenna impedances, which include a PCB trace antenna or a 50Ω antenna. The output-matching π-network suppresses the carrier harmonics and transforms the antenna impedance to an optimal impedance at the PA pin. The [Typical Application Circuit](#) can deliver an output power of +13dBm with a +3.0V supply. [Table 3](#) has approximate PA load impedances for desired output powers.

The PAPWR bits in the PA1 register control the output power of the PA. This setting adjust the number of parallel drivers used, which determine the final output power (see [Figure 3](#)).

Figure 3. Power Amplifier

### Boost Mode

The PA can deliver up to 16dBm of output power.

High output power can be achieved in two ways:

- Lower the load impedance for the PA by adjusting the output matching network,

- For frequencies over 850MHz, change the duty cycle of the square wave driving the PA from 25% to 50% by setting PA\_BOOST = 1 in register SHDN (0x05) and adjusting the output matching network.

Note that, when using PA\_BOOST = 1, the maximum supply voltage should not exceed 3V. For frequencies under 850MHz, the PA\_BOOST bit should remain at 0, the output match can be adjusted to provide higher output power.

**Table 3. PA Load Impedance for Desired Output Power**

| FREQUENCY (MHz) | OUTPUT POWER (dBm)   | PA LOAD IMPEDANCE (Ω) |

|-----------------|----------------------|-----------------------|

| 315             | 13                   | 165                   |

| 315             | 16<br>(PA_BOOST = 0) | 45                    |

| 434             | 13                   | 180                   |

| 434             | 16<br>(PA_BOOST = 0) | 57                    |

| 863–928         | 11                   | 190                   |

| 863–928         | 16<br>(PA_BOOST = 1) | 34                    |

Refer to the *MAX4146x EV Kit User's Guide* for details.

### Programmable Output Capacitance

The MAX41461/MAX41462 has an internal set of capacitors that can be switched in and out to present different capacitor values at the PA output. The capacitors are connected from the PA output to ground. This allows changing the tuning network along with the synthesizer divide ratio each time the transmitted frequency changes, making it possible to maintain maximum transmitter power while moving rapidly from one frequency to another.

The variable capacitor is programmed through register PA2 (0x07) bits 4:0 (PACAP). The tuning capacitor has a nominal resolution of 0.18pF, from 0pF to 5.4pF. In preset mode, the variable capacitor is set to 0pF.

### Transmitter Power Control

The transmitter power of the MAX41461/MAX41462 can be set in approximately 2.5dB steps by setting PAPWR[2:0] register bits using the I<sup>2</sup>C interface. The transmitted power (and the transmitter current) can be lowered by increasing the load impedance on the PA. Conversely, the transmitted power can be increased by lowering the load impedance.

### Preset Mode Output Power

The output power of the PA in Preset mode (where both SEL0 and SEL1 pins are not connected to GND) is always set for maximum power level (PAPWR[2:0] = 0x7) for a given load impedance. In order to adjust output power levels in preset mode, the load impedance must be adjusted accordingly.

### Crystal (XTAL) Oscillator

The XTAL oscillator in the MAX41461/MAX41462 is designed to present a capacitance of approximately 12pF from the XTAL1 and XTAL2 pins to ground. In most cases, this corresponds to a 6pF load capacitance applied to the external crystal when typical PCB parasitics are included. It is very important to use a crystal with a load capacitance equal to the capacitance of the MAX41461/MAX41462 crystal oscillator plus PCB parasitics. If a crystal designed to oscillate with a different load capacitance is used, the crystal is pulled away from its stated operating frequency introducing an error in the reference frequency. The crystal's natural frequency is typically below its specified frequency. However, when loaded with the specified load capacitance, the crystal is pulled and oscillates at its specified frequency. This pulling is already accounted for in the specification of the load capacitance. Accounting for typical board parasitics, a 16MHz, 12pF crystal is recommended. Please note that adding discrete capacitance on the crystal also increases the startup time and adding too much capacitance could prevent oscillation altogether.

Additional pulling can be calculated if the electrical parameters of the crystal are known. The frequency pulling is given by:

$$f_P = \frac{C_M}{2} \left( \frac{1}{C_{CASE} + C_{LOAD}} - \frac{1}{C_{CASE} + C_{SPEC}} \right) \times 10^6$$

where:

$f_P$  is the amount the crystal frequency pulled in ppm.

$C_M$  is the motional capacitance of the crystal.

$C_{CASE}$  is the case capacitance.

$C_{SPEC}$  is the specified load capacitance.

$C_{LOAD}$  is the load capacitance.

When the crystal is loaded as specified (i.e.,  $C_{LOAD} = C_{SPEC}$ ), the frequency pulling equals zero. For additional details on crystal pulling and load capacitance affects, refer to *Maxim Tutorial 5422 – Crystal Calculations for ISM RF Products*.

### Turn-On Time of Crystal Oscillator

The turn-on time of crystal oscillator (XO),  $t_{XO}$ , is defined as elapsed time from the instant of turning on XO circuit to the first rising edge of XO divider clock output. The external microcontroller turns on the XO by,

1. Sending a wakeup pulse for MAX41461–MAX41464 in the preset mode, or

2. Writing to device I<sup>2</sup>C address for MAX41461–MAX41464 in the I<sup>2</sup>C mode, or

3. Pulling CSB pin low on the MAX41460.

### Crystal Divider

The recommended crystal frequencies are 13.0MHz, 16.0MHz, and 19.2MHz. An internal clock of 3.2MHz $\pm$ 0.1MHz frequency is required. To maintain the internal 3.2MHz time base, XOCLKDIV[1:0] (register CFG1, 0x00, bit 4) must be programmed, based on the crystal frequency, as shown in [Table 4](#).

**Table 4. Required Crystal Divider Programming**

| CRYSTAL FREQUENCY (MHz) | Crystal Divider Ratio | XOCLKDIV[1:0] |

|-------------------------|-----------------------|---------------|

| 13.0                    | 4                     | 00            |

| 16.0                    | 5                     | 01            |

| 19.2                    | 6                     | 10            |

### Crystal Frequency in Preset Mode

For MAX41461/MAX41462 in preset mode (where *both* SEL0 and SEL1 pins are *not* connected to GND), crystal frequency must be 16MHz to ensure accurate output frequency.

### Phase-Locked Loop (PLL)

The MAX41461/MAX41462 utilizes a fully integrated fractional-N PLL for its frequency synthesizer. All PLL components, including loop filter, are included on-chip. The synthesizer has a 16-bit fractional-N topology with a divide ratio that can be set from 11 to 72, allowing the transmit frequency to be adjusted in increments of  $f_{XTAL}/65536$ . The fractional-N architecture also allows exact FSK frequency deviations to be programmed. FSK deviations as low as  $\pm 1\text{kHz}$  and as high as  $\pm 100\text{kHz}$  can be set by programming the appropriate registers.

The internal VCO can be tuned continuously from 286MHz to 960MHz in normal mode, and from 286MHz–320MHz, 425MHz–480MHz, and 860MHz–960MHz in low phase noise mode.

### Frequency Programming

The desired frequency can be programmed by setting bits FREQ in registers PLL3, PLL4, and PLL5 (0x0B, 0x0C, 0x0D). To calculate the FREQ bits, use:

$$\text{FREQ}[23 : 0] = \text{ROUND}\left(\frac{65536 \times f_C}{f_{XTAL}}\right)$$

See [Table 5](#) to program the LODIV bits in register PLL1 (0x08) when choosing a LO frequency. It is recommended to leave bits CPVAL and CPLIN at factory defaults. If integer-N synthesis is desired, set bit FRACMODE = 0 in register PLL1.

**Table 5. LODIV Setting**

| FREQUENCY RANGE (MHz)         | LODIV SETTING |

|-------------------------------|---------------|

| 286–960, Low Current Mode     | 0x0           |

| 286–320, Low Phase Noise Mode | 0x3           |

| 425–480, Low Phase Noise Mode | 0x2           |

| 860–960, Low Phase Noise Mode | 0x1           |

### Fractional-N Spurs

The 16-bit fractional-N, delta-sigma modulator can produce spurious that can show up on the power amplifier output spectrum. If slight frequency offsets can be tolerated, set the LSB of FREQ (register PLL5, bit 0) to logic-high. Using an odd value (logic 1 at bit 0) of the 24-bit FREQ register will produce lower PLL spurious compared to even values (logic 0 at bit 0).

### Turn-On Time of PLL

The turn-on time of PLL,  $t_{PLL}$ , is defined as the elapsed time from the instant when the XO output is available to the instant when PLL frequency acquisition is complete.

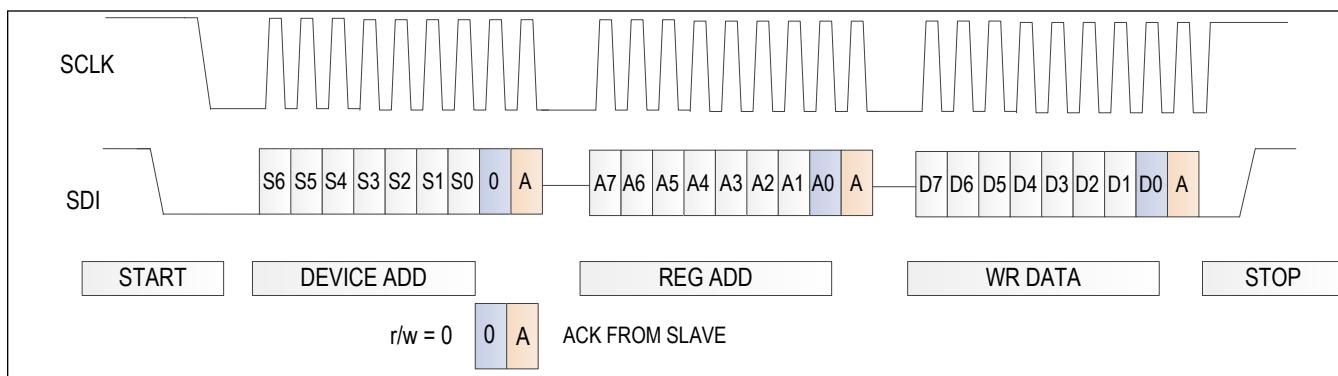

## Two-Wire I<sup>2</sup>C Serial Interface

When pins SEL0 and SEL1 are grounded, the MAX41461/MAX41462 features a 2-wire I<sup>2</sup>C-compatible serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX41461/MAX41462 and the master at clock frequencies up to 1MHz. The master device initiates a data transfer on the bus and generates the SCL signal to permit data transfer. The MAX41461/MAX41462 functions as an I<sup>2</sup>C slave device that transfers and receives data to and from the master. Pull SDA and SCL high with external pullup resistors of 1kΩ or greater, referenced to V<sub>DD</sub> for proper I<sup>2</sup>C operation.

One bit transfers during each SCL clock cycle. A minimum of nine clock cycles is required to transfer a byte into or out of the MAX41461/MAX41462 (8 bits and an ACK/NACK). The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the [START and STOP Conditions](#) section). Both SDA and SCL remain high when the bus is not busy.

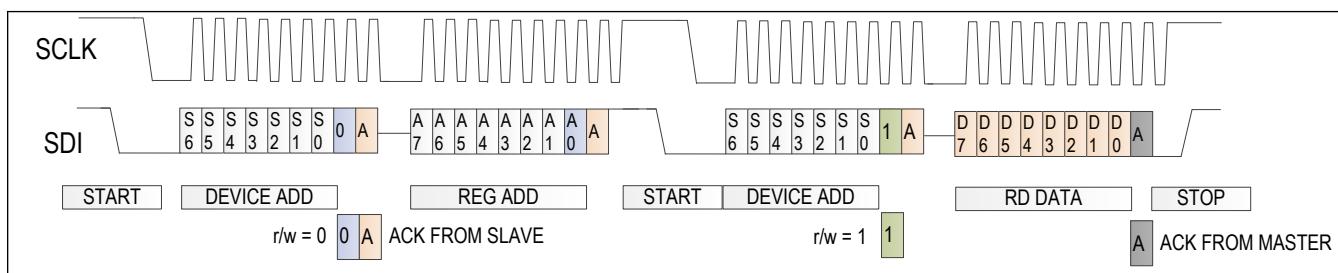

Figure 4 and Figure 5 show I<sup>2</sup>C Write transaction and I<sup>2</sup>C Read transaction protocols, respectively.

Figure 4. I<sup>2</sup>C Write

Figure 5. I<sup>2</sup>C Read

### START and STOP Conditions

The master initiates a transmission with a START condition (S), which is a high-to-low transition on SDA while SCL is high. The master terminates a transmission with a STOP condition (P), which is a low-to-high transition on SDA while SCL is high.

### Acknowledge and Not-Acknowledge Conditions

Data transfers are framed with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX41461/MAX41462 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse.

To generate a not-acknowledge condition, the receiver allows SDA to be pulled high before the rising edge of the

acknowledge-related clock pulse, and leaves SDA high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master must reattempt communication at a later time.

### Slave Address

The MAX41461/MAX41462 has a 7-bit I<sup>2</sup>C slave address that must be sent to the device following a START condition to initiate communication. The slave address is internally programmed to 0xD2 for WRITE and 0xD3 for READ. The MAX41461/MAX41462 continuously awaits a START condition followed by its slave address. When the device recognizes its slave address, it acknowledges by pulling the SDA line low for one clock period, then it is ready to accept or send data, depending on the R/W bit.

### Write Cycle

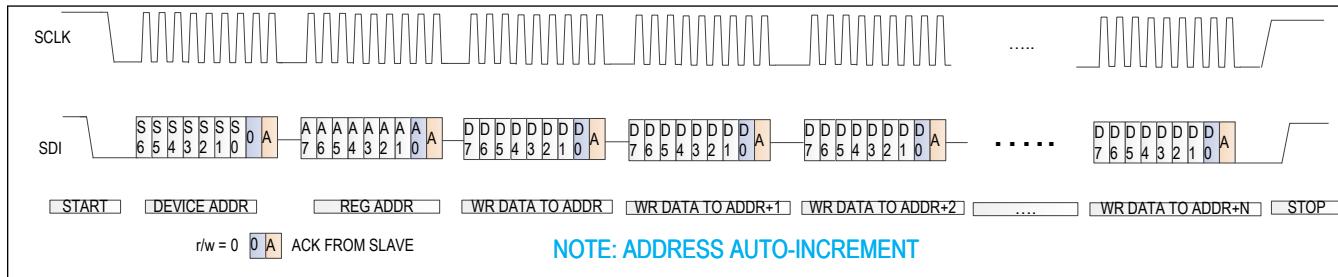

When addressed with a write command, the MAX41461/MAX41462 allows the master to write to either a single register or to multiple successive registers.

A write cycle begins with the bus master issuing a START condition, followed by the 7 slave address bits and a write bit (R/W = 0). The MAX41461/MAX41462 issues an ACK if the slave address byte is successfully received. The bus master must then send the address of the first register it wishes to write to (see [Register Map](#)). The slave acknowledges the address and the master can then write one byte to the register at the specified address. Data is written beginning with the most significant bit (MSB). The MAX41461/MAX41462 again issues an ACK if the data is successfully written to the register.

The master can continue to write data to the successive internal registers with the MAX41461/MAX41462 acknowledging each successful transfer, or the master can terminate transmission by issuing a STOP condition. The write cycle does not terminate until the master issues a STOP condition.

[Figure 6](#) illustrates I<sup>2</sup>C Burst Write transaction protocol.

Figure 6. I<sup>2</sup>C Burst Write

### Read Cycle

When addressed with a read command, the MAX41461/MAX41462 allows the master to read back a single register or multiple successive registers.

A read cycle begins with the bus master issuing a START condition, followed by the 7 slave address bits and a write bit (R/W = 0). The device issues an ACK if the slave address byte is successfully received. The bus master must then send the address of the first register it wishes to read. The slave acknowledges the address. A START condition is then issued by the master, followed by the 7 slave address bits and a read bit (R/W = 1). The device issues an ACK if the slave address byte is successfully received. The device starts sending data MSB first with each SCL clock cycle. At the 9th clock cycle, the master can issue an ACK and continue to read successive registers, or the master can terminate the transmission by issuing a NACK. The read cycle does not terminate until the master issues a STOP condition.

### Buffered Clock Output

MAX41461/MAX41462 provides a buffered clock output (CLKOUT) on pin 6 of the chip in the preset mode, and the frequency of CLKOUT is 800 kHz. In I<sup>2</sup>C mode, MAX41461/MAX41462 uses pin 6 as the SCL line of the I<sup>2</sup>C interface.

CLKOUT\_DELAY[1:0] (register CFG2, address 0x01, bits 7:6) is only used in the preset modes, with a preset value of 0x02. These two register bits are not used in programming mode.

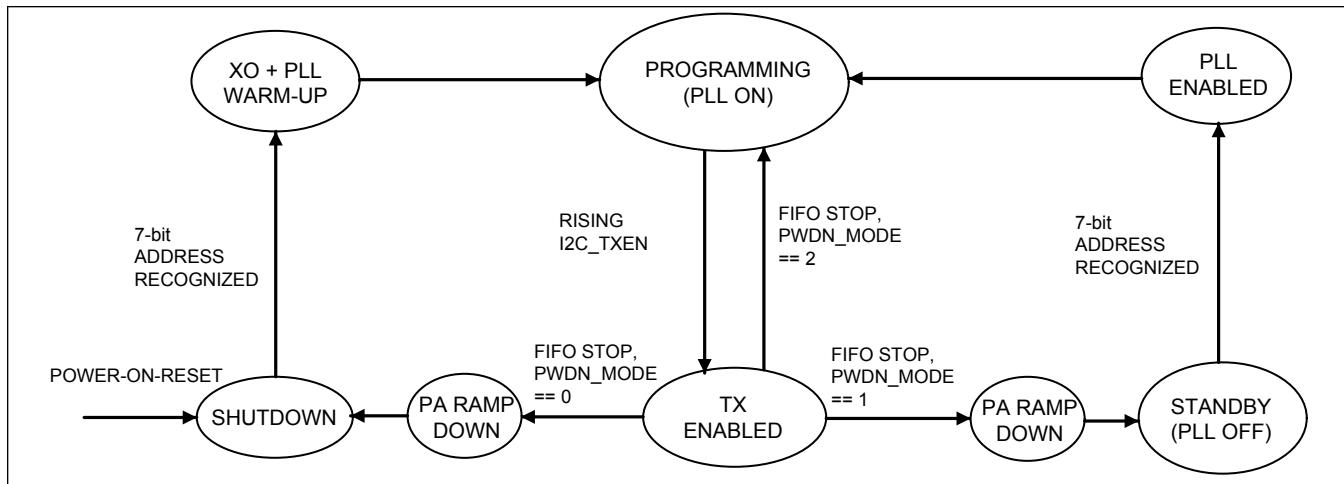

### State Diagrams

In the I<sup>2</sup>C programming mode, the device has four major states: shutdown, standby, programming, and transmitter-enabled. These states describe the power-on or power-off status of the transmitter's three primary internal circuit blocks: the crystal oscillator (XO), the PLL synthesizer, and the power amplifier (PA).

**Table 6. State Descriptions**

| State               | XO  | PLL | PA              |

|---------------------|-----|-----|-----------------|

| Shutdown            | Off | Off | Off             |

| Standby             | On  | Off | Off             |

| Programming         | On  | On  | Off             |

| Transmitter-Enabled | On  | On  | On with Ramp-up |

Configuration register values are retained in all states unless changed by programming, or if the device is powered off or undergoes a SOFTRESET.

A wake-up byte with 7-bit device address from the I<sup>2</sup>C bus initiates the warm-up of the XO and PLL.

The device can support two types of I<sup>2</sup>C transactions: register access only, and register access followed by data transmission. The event trigger of data transmission is a rising edge on I<sub>C</sub>\_TXEN, which is a special signal with two register-bit aliases I<sub>C</sub>\_TXEN1 (register CFG6, 0x0A, bit 2) and I<sub>C</sub>\_TXEN2 (register CFG7, 0x10, bit 2). A rising edge on I<sub>C</sub>\_TXEN can be generated by clearing I<sub>C</sub>\_TXEN1 and setting I<sub>C</sub>\_TXEN2 in a single I<sup>2</sup>C transaction.

I<sub>C</sub>\_TXEN is automatically cleared in two cases: 1) wake-up from shutdown, 2) return to programming state from the transmitter-enabled state. In those two cases, a rising edge on I<sub>C</sub>\_TXEN can be generated by setting I<sub>C</sub>\_TXEN2 in CFG7, without explicit clearing of I<sub>C</sub>\_TXEN1.

Data to be transmitted are written into a special register, byte I<sub>C</sub>\_TX\_DATA[7:0] (register I<sub>C</sub>3, 0x13, bits 7:0). Automatic incrementing of addresses in I<sup>2</sup>C burst write are disabled for this special register. Each data byte written into I<sub>C</sub>\_TX\_DATA will be transferred into a FIFO buffer. The device has an internal 1-bit signal FIFO\_STOP. At the end of data transmission, FIFO\_STOP is set, and the device references the PWDN\_MODE[1:0] (register CFG4, 0x03, bits 1:0) to enter shutdown, standby, or programming state. The shutdown and standby states can only be entered after the transmitter-enabled state.

In both the shutdown and standby states, programming through the I<sup>2</sup>C interface is not allowed. The device will exit the shutdown or standby state once its 7-bit I<sup>2</sup>C address is received.

Figure 7. Simplified State Diagram in Programming Mode

In the preset mode, the MAX41461/MAX41462 device has two major states: shutdown, and transmitter-enabled. After power is applied, the device enters the shutdown state, refer to [Initial Programming](#). A rising edge on DATA (pin 7) initiates the warm-up of the XO and PLL. After PLL is locked, a falling edge on DATA enables the transmitter. The device returns to shutdown state when there is no DATA activity, (i.e., DATA stays at 0 for 16384 cycles of the internal 3.2MHz clock).

Figure 8. State Diagram in Preset Mode

## Initial Programming

After turning on power supply (or a soft reset), two I<sup>2</sup>C transactions are required to initialize the PLL frequency synthesizer. The first transaction ensures register ADDL2 at address 0x1A is written to its default of 0x80. The second transaction burst-writes 20 consecutive registers from address 0x00 to 0x13.

The device needs to transmit an 8-bit dummy packet for initial programming. The initial programming must clear MODMODE (register CFG1, address 0x00, bit 0), clear I<sup>2</sup>C\_TXEN1 (register CFG6, address 0x0A, bit 2), configure FREQ[23:0] (register PLL3, PLL4 and PLL5) to desired frequency, set I<sup>2</sup>C\_TXEN2 (register CFG7, address 0x10, bit 2), and configure I<sup>2</sup>C\_TX\_DATA[7:0] (register I<sup>2</sup>C3, address 0x13) to 0x00. In addition, BCLK\_POSTDIV[2:0], BCLK\_PREDIV[7:0], and PKTLEN\_MODE should be configured to default values in the register map.

Initial programming cannot be completed by a single burst-write transaction because the I<sup>2</sup>C\_TX\_DATA register at address 0x13 is a special register that disables automatic address increment. However, two I<sup>2</sup>C transactions may be merged to a combined transaction, where each write begins with a START mark and the slave address.

After initial programming, the device will enter the shutdown, standby, or programming state according to the setting of PWDN\_MODE[1:0] (register CFG4, address 0x03, bit[1:0]).

## Startup

## Programming Mode

This section assumes that initial programming is done after power on (or soft reset). Configuration register values are retained in all states unless changed by programming, or if the device is powered off or undergoes a SOFTRESET.

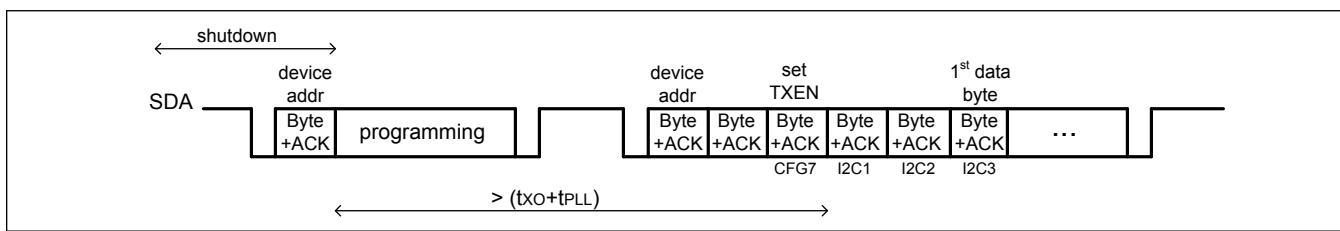

### Case 1: Using Two I<sup>2</sup>C Transactions for Startup from Shutdown

The startup of MAX41461/MAX41462 in programming mode, from shutdown state, uses two I<sup>2</sup>C transactions: one for configuration update, and the other for data transmission.

In the first I<sup>2</sup>C transaction, the master device burst-writes consecutive registers that are a portion or all of the 16 registers from address 0x00 to 0x0F. Those consecutive registers may or may not include CFG6. If CFG6 is included, the I<sup>2</sup>C\_TXEN1 bit should be cleared; otherwise, I<sup>2</sup>C\_TXEN1 is automatically cleared in the wake-up from shutdown.

In the second I<sup>2</sup>C transaction, the master device can set I<sup>2</sup>C\_TXEN2 (register CFG7, address 0x10, bit 2), configure PKTLEN\_MODE (register I<sup>2</sup>C1, address 0x11, bit 7) and PKTLEN[14:0], and write the data to be transmitted into I<sup>2</sup>C\_TX\_DATA (register I<sup>2</sup>C3, address 0x13). Automatic increment of register address during burst write is disabled at address 0x13.

The event-trigger for wake-up is the recognition of I<sup>2</sup>C address of the MAX41461/MAX41462 device. The event trigger for data transmission is the rising edge I<sup>2</sup>C\_TXEN that has two aliases of I<sup>2</sup>C\_TXEN1 and I<sup>2</sup>C\_TXEN2. The time lag between those two triggers must be longer than  $t_{XO}+t_{PLL}$ . To meet this requirement, the master device can adjust the waiting time between two I<sup>2</sup>C transactions.

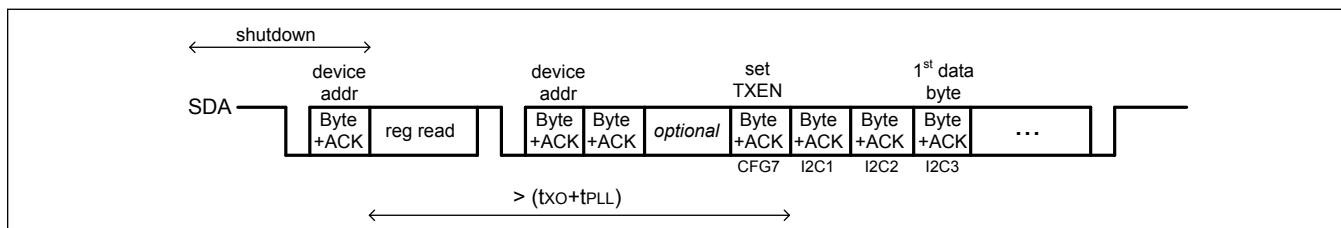

Figure 9. Using Two I<sup>2</sup>C Transactions to Start Data Transmission From the Shutdown State

### Case 2: Using a Single I<sup>2</sup>C Transactions for Startup from Shutdown (recommended for use with I<sup>2</sup>C Fast Mode)

From shutdown state, the start-up of device in programming mode may use a single I<sup>2</sup>C transaction to burst-write consecutive registers starting from address 0x00. Data to be transmitted are written into I<sub>2</sub>C\_TX\_DATA (register I<sub>2</sub>C3, address 0x13). Automatic increment of register address during burst write is disabled at address 0x13. The programming should clear I<sub>2</sub>C\_TXEN1 and set I<sub>2</sub>C\_TXEN2.

The event-trigger for wake-up is the recognition of I<sup>2</sup>C address of the device. The event-trigger for data transmission is the rising edge of I<sub>2</sub>C\_TXEN that has two aliases of I<sub>2</sub>C\_TXEN1 and I<sub>2</sub>C\_TXEN2. The time lag between those two triggers, here 162 cycles of SCL, must be longer than  $t_{XO} + t_{PLL}$ . To meet this requirement, the fast-mode I<sup>2</sup>C with 400kHz SCL is recommended.

Figure 10. Using a Single I<sup>2</sup>C Transaction to Start Data Transmission From the Shutdown State

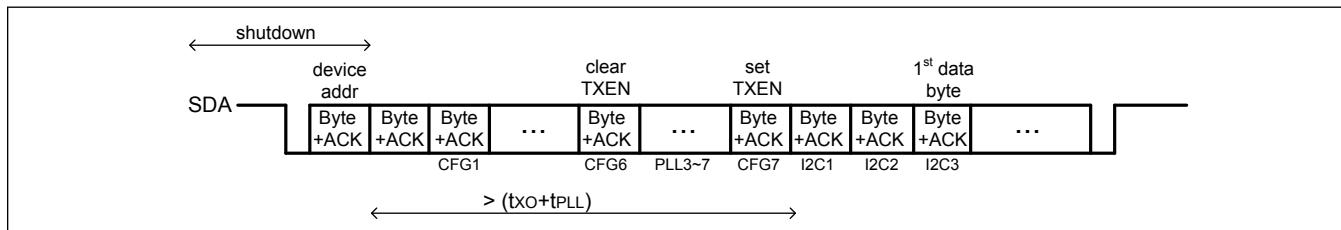

### Case 3: Using a Combined I<sup>2</sup>C Transaction for Startup from Shutdown (recommended for use with most I<sup>2</sup>C clock rates)

From shutdown state, the startup of MAX41461/MAX41462 in programming mode can use a combined I<sup>2</sup>C transaction with repeated START marks. In a combined transaction, the master device can do multiple read/write operations without losing control to other master devices on the I<sup>2</sup>C bus. For example, the combined transaction can have a burst-read operation followed by a burst-write operation.

In the burst-write operation, the master device should write consecutive registers starting from CFG7 (address 0x10) or any register preceding CFG7. Data to be transmitted are written into I<sub>2</sub>C\_TX\_DATA (register I<sub>2</sub>C3, address 0x13). Automatic incrementing of register addresses during burst-write is disabled at address 0x13. The programming should set I<sub>2</sub>C\_TXEN2 (and clear I<sub>2</sub>C\_TXEN1 if CFG6 is included in the registers to write).

The event-trigger for wake-up is the recognition of device address in the burst-read operation. The event-trigger for data transmission is the rising edge of I<sub>2</sub>C\_TXEN that has two aliases of I<sub>2</sub>C\_TXEN1 and I<sub>2</sub>C\_TXEN2. The time lag between those two triggers must be longer than  $t_{XO} + t_{PLL}$ . To meet this requirement, the master device can adjust the number of registers to read in the burst-read operation.

Figure 11. Using a Combined I<sup>2</sup>C Transaction to Start Data Transmission From the Shutdown State

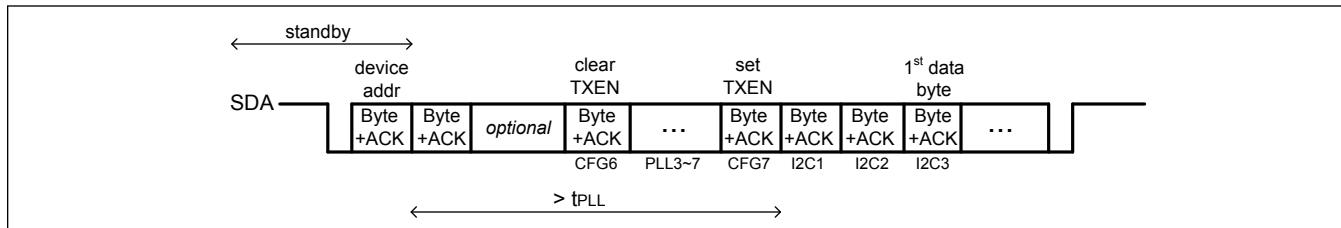

#### Case 4: Using a Single I<sup>2</sup>C Transactions for Startup from Standby (recommended for use with I<sup>2</sup>C Fast-mode and I<sup>2</sup>C Fast-mode Plus)

From standby state, the startup of MAX41461/MAX41462 in programming mode can use a single I<sup>2</sup>C transaction to burst-write consecutive registers starting from CFG6 (address 0x0A) or any register preceding CFG6. Data to be transmitted are written into I<sup>2</sup>C\_TX\_DATA (register I<sup>2</sup>C3, address 0x13). Automatic incrementing of register addresses during burst-write is disabled at address 0x13. The programming should clear I<sup>2</sup>C\_TXEN1 and set I<sup>2</sup>C\_TXEN2.

The event-trigger for wake-up is the recognition of I<sup>2</sup>C address of the device. The event-trigger for data transmission is the rising edge of I<sup>2</sup>C\_TXEN that two aliases of I<sup>2</sup>C\_TXEN1 and I<sup>2</sup>C\_TXEN2. The time lag between those two triggers, here  $\geq 72$  cycles of SCL, must be longer than  $t_{PLL}$  for startup from standby. This requirement is met for the fast-mode I<sup>2</sup>C with 400kHz SCL. In the case of Fast-mode Plus I<sup>2</sup>C with 1MHz SCL, the master device can burst-write registers starting from PLL1.

Figure 12. Using a Single I<sup>2</sup>C Transaction to Start Data Transmission From the Standby State

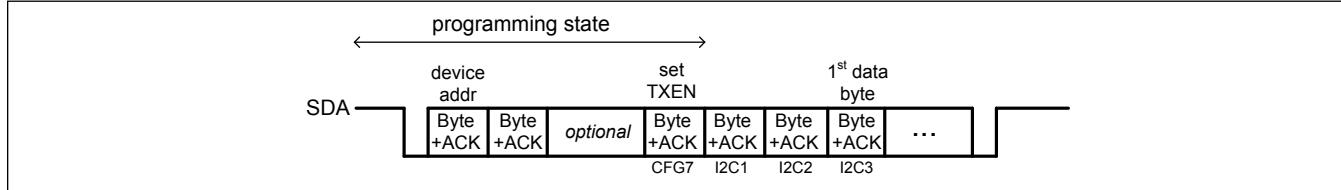

#### Case 5: Using a Single I<sup>2</sup>C Transactions for Startup from Programming

The MAX41461/MAX41462 device can transmit a data packet each time in the transmitter-enabled state. After data transmission, the device refers to the setting of PWDN\_MODE[1:0] to enter the shutdown, standby, or programming state. If the next data packet requires fast start-up, PWDN\_MODE[1:0] can be configured to 0x10 so that the device returns to the programming state.

Then, the master device can use a single I<sup>2</sup>C transaction to burst-write consecutive registers starting from CFG7 (address 0x10) or any register preceding CFG7. Data to be transmitted are written into I<sup>2</sup>C\_TX\_DATA (register I<sup>2</sup>C3, address 0x13). Automatic incrementing of register addresses during burst-write is disabled at address 0x13. The programming should set I<sup>2</sup>C\_TXEN2 (and clear I<sup>2</sup>C\_TXEN1 if CFG6 is included in the registers to write). There is no restrictions arising from  $t_{XO}$  and  $t_{PLL}$ .

Figure 13. Using a Single I<sup>2</sup>C Transaction to Start Data Transmission From the Programming State

## FIFO Buffer

The I<sup>2</sup>C interface is a bus connected to multiple master or slave devices. The microcontroller is a master device and the MAX41461/MAX41462 is a slave device. The microcontroller can initiate communication with the slave device by I<sup>2</sup>C addressing (e.g., sending a START mark followed by 7-bit device address). The slave device is required to acknowledge every byte transferred through I<sup>2</sup>C.

For data transmission, the microcontroller can burst-write consecutive registers, including CFG7 and I2C3. The purpose of writing CFG7 is to set I2C\_TXEN2 and, therefore, generate a trigger to enable the transmitter. Automatic increment of register address in I<sup>2</sup>C burst-write is disabled for the I2C3 register, which is also named I2C\_TX\_DATA. Once the transmitter is enabled, all bytes written to I2C\_TX\_DATA are moved into a FIFO buffer. The buffer size is 4 bytes. The FIFO buffer is enabled only in the transmitter-enabled state.

A programmable baud-rate clock is used for retrieving and transmitting bits from the FIFO buffer. The baud rate is programmable by BCLK\_PREDIV[7:0] (register CFG3, 0x02, bits 7:0) and BCLK\_POSTDIV[2:0] (register CFG2, 0x01, bits 2:0) as the following expression:

$$\text{BaudRate} = \frac{f_{\text{CLK}}}{2 \times (1 + \text{BCLK\_PREDIV}) \times 2^{\text{BCLK\_POSTDIV}}}$$

where  $f_{\text{CLK}}$  is the crystal-divider output clock rate (nominally, 3.2 MHz). Valid values of BCLK\_PREDIV are from 3 to 255. Valid values of BCLK\_POSTDIV are from 1 to 5.

To avoid underflow of the FIFO buffer, the baud-rate must be lower than 8/9 of the SCL clock rate. The device can support three modes of SCL clock frequencies: 100kHz, 400kHz, and 1MHz. In the 100kHz mode, it is recommended to limit baud-rate to no more than 50kbps.

A FIFO overflow is avoided by utilizing the I<sup>2</sup>C clock stretching mechanism. Clock stretching is done before the ACK bit. There is no clock-stretching timeout.

Each time before data transmission, the I2C1 and I2C2 registers are configured to specify PKTLEN\_MODE and PKTLEN[14:0]. Data transmission stops when PKTLEN\_MODE is set and the number of bauds transmitted is equal to PKTLEN[14:0]. Data transmission also stops at FIFO underflow or overflow. An internal 1-bit flag FIFO\_STOP is set at the end of data transmission. The rising edge of FIFO\_STOP serves as the event trigger to disable the transmitter. See [State Diagrams](#) section.

When the number of bauds to be transmitted is known before data transmission and less than 32768, it is recommended to set PKTLEN\_MODE and configure PKTLEN[14:0] as the number of bauds to be transmitted. Otherwise, clear PKTLEN\_MODE and utilize FIFO underflow to stop data transmission. Once the microcontroller stops writing I2C\_TX\_DATA, FIFO underflow will occur after the data stored in FIFO buffer are transmitted.

Read-only register I2C4, I2C5, and I2C6 are provided to report diagnostic information for the FIFO buffer.

## Frequency-Hopping

In programming mode, the frequency synthesizer is initialized to a frequency in a selected ISM band by initial programming. After that, for the purpose of frequency dithering or frequency hopping, the FREQ[23:0] registers can be updated to a new frequency in the same selected band for each data packet to be transmitted.

Because programming is not allowed in the transmitted-enabled state (see [State Diagrams](#) section), frequency configuration cannot be changed when PA is enabled. See [Startup](#) section for details on how to program the device for data transmission.

After transmitting a data packet, the device enters the shutdown, standby, or programming state according to the setting of PWDN\_MODE[1:0] register. The three options have different startup time for transmitting the the next data packet.

The startup time from shutdown is at least  $(t_{XO} + t_{PLL} + t_{TX})$ , where  $t_{XO}$  is the turn-on time of crystal oscillator,  $t_{PLL}$  is the turn-on time of PLL,  $t_{TX}$  is the turn-on time of transmitter.

The startup time from standby is at least  $(t_{PLL} + t_{TX})$ .

The  $t_{TX}$  time is 27 cycles of the SCL clock plus 2 cycles of the baud-rate clock. For example, the SCL clock rate is 1MHz, the baud rate is 100kb/s, the value of  $t_{TX}$  is 47 $\mu$ s. See [Electrical Characteristics](#) table for typical values of  $t_{XO}$  and  $t_{PLL}$ .

## Register Map

### Register Map

| ADDRESS   | NAME       | MSB         |                   |               |                  |                   |                   |          | LSB       |

|-----------|------------|-------------|-------------------|---------------|------------------|-------------------|-------------------|----------|-----------|

| <b>TX</b> |            |             |                   |               |                  |                   |                   |          |           |

| 0x00      | CFG1[7:0]  |             | XOCLKDELAY[1:0]   | XOCLKDIV[1:0] | –                | FSKSHAPE          | SYNC              | MODMODE  |           |

| 0x01      | CFG2[7:0]  |             | CLKOUT_DELAY[1:0] | –             | –                | –                 | BCLK_POSTDIV[2:0] |          |           |

| 0x02      | CFG3[7:0]  |             |                   |               | BCLK_PREDIV[7:0] |                   |                   |          |           |

| 0x03      | CFG4[7:0]  | –           | –                 | –             | –                | –                 | PWDN_MODE[1:0]    |          |           |

| 0x04      | CFG5[7:0]  | –           | –                 |               |                  | RESERVED[5:0]     |                   |          |           |

| 0x05      | SHDN[7:0]  | –           | –                 | –             | –                | –                 | RESERVED          | RESERVED | PA_BOOST  |

| 0x06      | PA1[7:0]   |             | RESERVED[2:0]     | –             | –                | –                 | PAPWR[2:0]        |          |           |

| 0x07      | PA2[7:0]   | –           | –                 | –             |                  |                   | PACAP[4:0]        |          |           |

| 0x08      | PLL1[7:0]  |             | CPLIN[1:0]        | FRACMODE      | RESERVED[1:0]    | LODIV[1:0]        | LOMODE            |          |           |

| 0x09      | PLL2[7:0]  | RESERVED    | RESERVED          | –             | –                | –                 | CPVAL[1:0]        |          |           |

| 0x0A      | CFG6[7:0]  | –           | –                 | –             | –                | –                 | I2C_TXE_N1        | RESERVED | RESERVED  |

| 0x0B      | PLL3[7:0]  |             |                   |               | FREQ[23:16]      |                   |                   |          |           |

| 0x0C      | PLL4[7:0]  |             |                   |               | FREQ[15:8]       |                   |                   |          |           |

| 0x0D      | PLL5[7:0]  |             |                   |               | FREQ[7:0]        |                   |                   |          |           |

| 0x0E      | PLL6[7:0]  | –           |                   |               | DELTAF[6:0]      |                   |                   |          |           |

| 0x0F      | PLL7[7:0]  | –           | –                 | –             | –                | DELTAF_SHAPE[3:0] |                   |          |           |

| 0x10      | CFG7[7:0]  | –           | –                 | –             | –                | –                 | I2C_TXE_N2        | RESERVED | RESERVED  |

| 0x11      | I2C1[7:0]  | PKTLEN_MODE |                   |               | PKTLEN[14:8]     |                   |                   |          |           |

| 0x12      | I2C2[7:0]  |             |                   |               | PKTLEN[7:0]      |                   |                   |          |           |

| 0x13      | I2C3[7:0]  |             |                   |               | I2C_TX_DATA[7:0] |                   |                   |          |           |

| 0x14      | I2C4[7:0]  | PKTCOMPLETE |                   |               | TX_PKTLEN[14:8]  |                   |                   |          |           |

| 0x15      | I2C5[7:0]  |             |                   |               | TX_PKTLEN[7:0]   |                   |                   |          |           |