## MAX25250

# Four Output Mini PMIC for Camera Applications

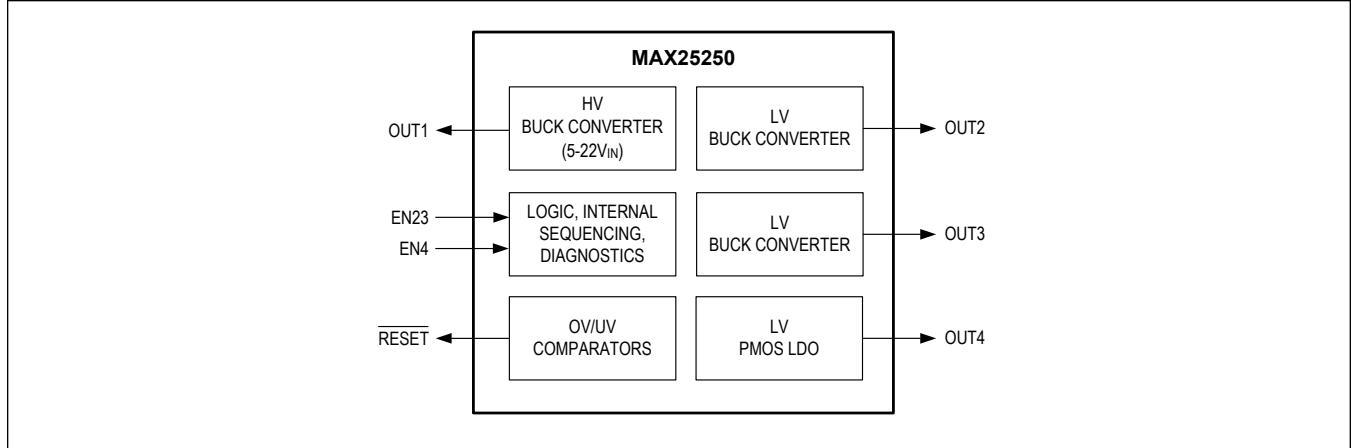

## General Description

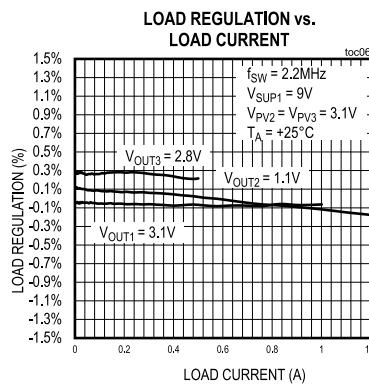

The MAX25250 is a high-efficiency, four-output PMIC that integrates three DC-DC converters and a high-PSRR LDO, with OV/UV monitoring on all outputs. OUT1 is a 1A high-voltage synchronous step-down converter operating from power over coax or car battery. OUT2 and OUT3 low-voltage synchronous step-down converters operate from OUT1 and provide a 0.8V to 3.9875V output voltage range. OUT2 can deliver 1.2A for high megapixel cameras and high-speed serializers. OUT3 can deliver 1.2A to power the secondary rails of the imager, serializer, and MCU. OUT4 is a low-voltage, low-noise, high-PSRR LDO for imager power. All buck converters achieve  $\pm 1.5\%$  output voltage accuracy over load, line, and temperature range. Overvoltage and undervoltage faults are monitored and errors are communicated through RESET.

This device features a 2.2MHz fixed-frequency PWM mode for better noise immunity and load-transient response. The high-frequency operation allows for the use of all ceramic capacitors and minimizes external components. The programmable spread-spectrum frequency modulation minimizes radiated electromagnetic emissions. Integrated low-R<sub>DSON</sub> switches improve efficiency at heavy loads and make layout simpler than discrete solutions.

Sequencing through the use of EN23 and EN4 pins and factory-settable output voltages increases flexibility for different image sensors and configurations. Other features include soft-start, overcurrent, and overtemperature protection. The MAX25250 is specified for operation over the -40°C to +125°C automotive temperature range.

## Applications

- Surround-View Cameras

- Rear-View Cameras

## Benefits and Features

- Multiple Functions for Small Size

- 1A Synchronous High-Voltage Buck Converter

- Input Voltage Range 5V to 22V

- 3V to 4V, and 5V Output Voltage in 50mV steps

- Two Synchronous Low-Voltage Buck Converters

- OUT2 and OUT3 Provide up to 1.2A

- 0.8V to 3.9875V in 12.5mV steps

- LDO for Camera Sensor; 50dB at 1kHz

- 2.2MHz Operation

- RESET Output – Open-Drain

- High-Precision

- $\pm 1.5\%$  Output Voltage Accuracy

- OV/UV Monitoring

- Robust for the Automotive Environment

- Current-Mode, Forced-PWM Operation

- Overtemperature and Short-Circuit Protection

- 3.5mm x 3.5mm 20-Pin TQFN

- -40°C to +125°C Grade 1 Automotive Temperature Range

- AEC-Q100 Qualified

[Ordering Information](#) appears at end of data sheet.

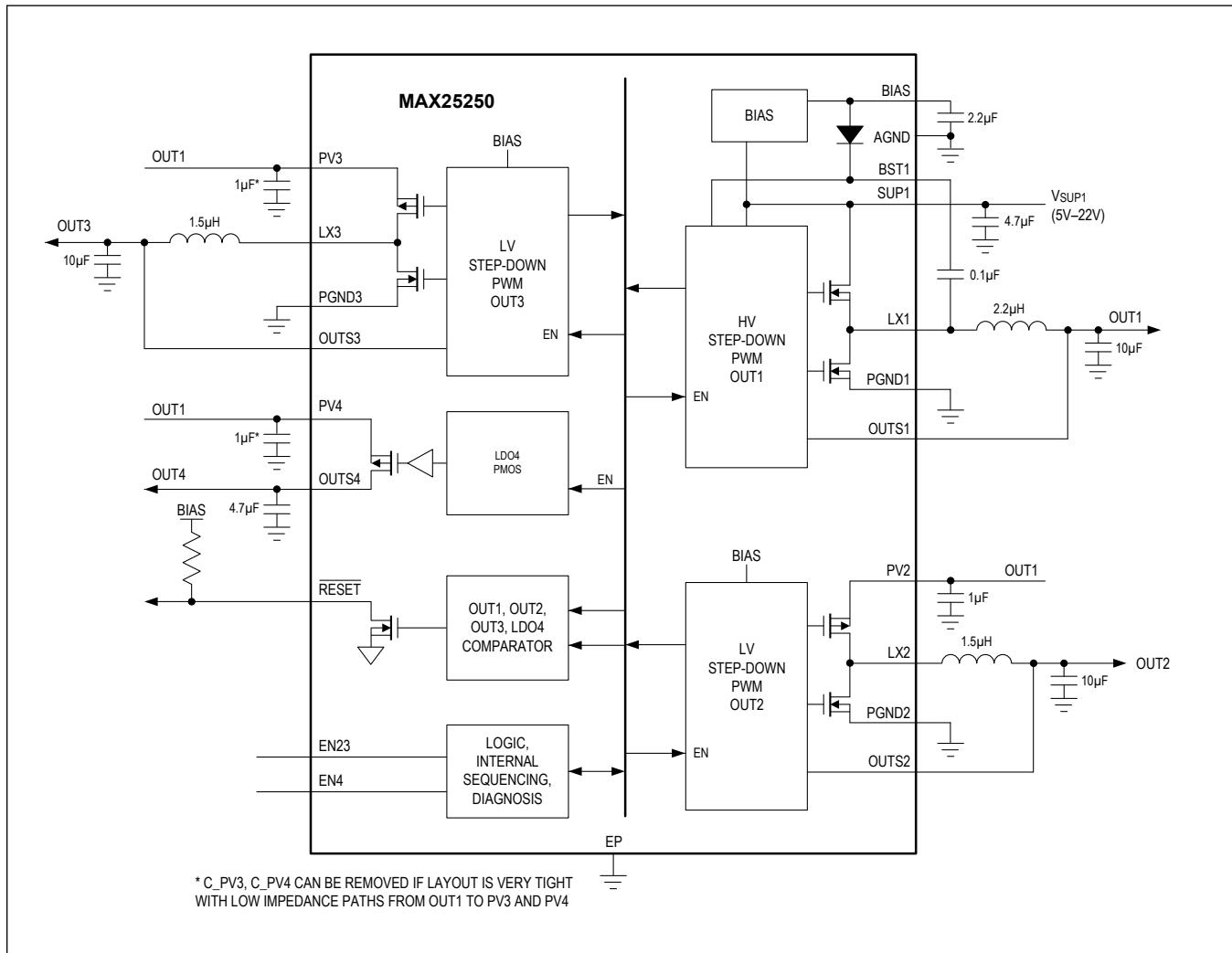

**Simplified Block Diagram**

---

**TABLE OF CONTENTS**

---

|                                         |    |

|-----------------------------------------|----|

| General Description .....               | 1  |

| Applications .....                      | 1  |

| Benefits and Features .....             | 1  |

| Simplified Block Diagram .....          | 2  |

| Absolute Maximum Ratings .....          | 6  |

| Recommended Operating Conditions .....  | 6  |

| Package Information .....               | 6  |

| 20-TQFN-EP .....                        | 6  |

| Electrical Characteristics .....        | 7  |

| Typical Operating Characteristics ..... | 10 |

| Pin Configuration .....                 | 12 |

| Pin Description .....                   | 12 |

| Functional Diagram .....                | 14 |

| Detailed Description .....              | 15 |

| Summary .....                           | 15 |

| Startup Timing and Soft-Start .....     | 15 |

| RESET Output .....                      | 16 |

| Active Pulldown .....                   | 16 |

| OV/UV Comparators .....                 | 16 |

| Spread-Spectrum Option .....            | 16 |

| Thermal Shutdown .....                  | 16 |

| Applications Information .....          | 17 |

| Output-Voltage Selection .....          | 17 |

| Input Capacitor .....                   | 17 |

| Output Capacitor .....                  | 17 |

| Inductor Selection .....                | 17 |

| PCB Layout Guidelines .....             | 17 |

| Ordering Information .....              | 18 |

| Revision History .....                  | 19 |

---

**LIST OF FIGURES**

---

|                                                |    |

|------------------------------------------------|----|

| Figure 1. Startup Timing Diagram .....         | 15 |

| Figure 2. Simplified RESET Logic Diagram ..... | 16 |

| Figure 3. RESET During Normal Operation .....  | 16 |

---

**LIST OF TABLES**

---

|                                                       |    |

|-------------------------------------------------------|----|

| Table 1. Output Voltage Options . . . . .             | 17 |

| Table 2. Minimum Output Capacitor Selection . . . . . | 17 |

| Table 3. Inductor Selection . . . . .                 | 17 |

## Absolute Maximum Ratings

|                             |                          |                                                                     |                                               |

|-----------------------------|--------------------------|---------------------------------------------------------------------|-----------------------------------------------|

| SUP1, LX1 to PGND_          | -0.3V to +24V            | AGND to PGND_                                                       | -0.3V to +0.3V                                |

| BST1 to LX1                 | -0.3V to 6V              | LX1 Short-Circuit Duration                                          | Continuous                                    |

| EN23, EN4 to AGND           | -0.3V to 6V              | LX2 Short-Circuit Duration                                          | Continuous                                    |

| PV2, PV3, PV4 to PGND_      | -0.3V to 6V              | LX3 Short-Circuit Duration                                          | Continuous                                    |

| BIAS to AGND                | -0.3V to 6V              | Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ )          |                                               |

| RESETB to AGND (MAX25250)   | -0.3V to 6V              | 20-TQFN-EP (derate 23.8 mW/ $^\circ\text{C}$ > $70^\circ\text{C}$ ) | 1904mW                                        |

| OUTS1, OUTS2, OUTS3 to AGND | -0.3V to 6V              | Operating Temperature                                               | -40 $^\circ\text{C}$ to +125 $^\circ\text{C}$ |

| OUTS4 to PGND               | -0.3V to PV4+0.3V        | Junction Temperature                                                | +150 $^\circ\text{C}$                         |

| LX1 to PGND1 (Note 1)       | -0.3V to $V_{SUP1}+0.3V$ | Storage Temperature Range                                           | -65 $^\circ\text{C}$ to +150 $^\circ\text{C}$ |

| LX2 to PGND2 (Note 1)       | -0.3V to PV2+0.3V        | Lead Temperature Range                                              | +300 $^\circ\text{C}$                         |

| LX3 to PGND3 (Note 1)       | -0.3V to PV3+0.3V        |                                                                     |                                               |

**Note 1:** Self-protected against transient voltages exceeding these limits for  $\leq 50\text{ns}$  under normal operation and loads up to the maximum rated output current.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Recommended Operating Conditions

| PARAMETER                 | SYMBOL | CONDITION | TYPICAL RANGE | UNIT             |

|---------------------------|--------|-----------|---------------|------------------|

| Ambient Temperature Range |        |           | -40 to 125    | $^\circ\text{C}$ |

**Note:** These limits are not guaranteed.

## Package Information

### 20-TQFN-EP

|                                                       |                                |

|-------------------------------------------------------|--------------------------------|

| Package Code                                          | T203A3Y+1C                     |

| Outline Number                                        | <a href="#">21-100306</a>      |

| Land Pattern Number                                   | <a href="#">90-100103</a>      |

| <b>THERMAL RESISTANCE, FOUR-LAYER BOARD</b>           |                                |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 40.4 $^\circ\text{C}/\text{W}$ |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2.4 $^\circ\text{C}/\text{W}$  |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

## Electrical Characteristics

( $V_{SUP1} = 13.5V$ ,  $V_{EN23} = V_{EN4} = V_{BIAS}$ ,  $V_{OUT1} = V_{PV2} = V_{PV3} = V_{PV4} = 3.1V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise noted, Typical values are at  $T_A = 25^{\circ}C$ . (Notes 3 and 4))

| PARAMETER                          | SYMBOL    | CONDITIONS                                                                        | MIN  | TYP  | MAX    | UNITS     |

|------------------------------------|-----------|-----------------------------------------------------------------------------------|------|------|--------|-----------|

| Supply Voltage Range               | $V_{SUP}$ | Fully Operational                                                                 | 5    | 22   |        | V         |

| Supply Current                     | $I_{SUP}$ | No load, no switching all four channels                                           |      | 3    |        | mA        |

| UVLO                               | UVLOR     | Rising                                                                            |      | 4.5  | 4.9    | V         |

|                                    | UVLOF     | Falling (default)                                                                 | 3.5  | 4    |        |           |

| BIAS Voltage                       |           | $5.5V \leq V_{SUP} \leq 22V$                                                      |      | 5    |        | V         |

| BIAS Current Limit                 |           |                                                                                   | 10   |      |        | mA        |

| <b>OUT1 (HV BUCK)</b>              |           |                                                                                   |      |      |        |           |

| Voltage Accuracy                   |           | $5V \leq V_{SUP} \leq 17V$ , $I_{OUT1} = 0$ to $1000mA$ , $V_{OUT1} = 3.1V$       | -1.5 |      | 1.5    | %         |

| Output Voltage Range               |           | 50mV steps (fixed 5V OUT1 available) (Note 2)                                     | 3    | 4    |        | V         |

| High-Side nMOS On-Resistance       |           | $V_{BIAS} = 5V$ , $I_{LX1} = 0.3A$                                                |      | 300  |        | $m\Omega$ |

| Low-Side nMOS On-Resistance        |           | $V_{BIAS} = 5V$ , $I_{LX1} = 0.3A$                                                |      | 200  |        | $m\Omega$ |

| High-Side Current- Limit Threshold |           |                                                                                   | 1.3  | 1.5  | 1.7    | A         |

| Switching Phase                    |           | (Note 2)                                                                          |      | 0    |        | Deg       |

| OUT1 Discharge Resistance          |           |                                                                                   |      | 50   |        | $\Omega$  |

| Soft-Start                         |           |                                                                                   |      | 0.75 |        | ms        |

| <b>OUT2 (LV BUCK)</b>              |           |                                                                                   |      |      |        |           |

| Voltage Accuracy                   |           | $3.0V \leq PV2 \leq 5V$ , $I_{OUT2} = 0$ to $1200mA$ , $V_{OUT2} = 1.8V$ , $1.1V$ | -1.5 |      | 1.5    | %         |

| Output Voltage Range               |           | 12.5mV steps (Note 2)                                                             | 0.8  |      | 3.9875 | V         |

| High-Side pMOS On-Resistance       |           | $I_{LX2} = 0.2A$                                                                  |      | 180  |        | $m\Omega$ |

| Low-Side nMOS On-Resistance        |           | $I_{LX2} = 0.2A$                                                                  |      | 70   |        | $m\Omega$ |

| High-Side Current- Limit Threshold |           | 1.2A OPTION                                                                       | 1.00 | 1.20 | 1.40   | A         |

|                                    |           | 2A OPTION                                                                         | 1.60 | 2.05 | 2.50   |           |

| LX2 Leakage Current                |           | $T_A = +25^{\circ}C$                                                              |      | 0.1  |        | $\mu A$   |

| Switching Phase                    |           | (Note 2)                                                                          |      | 180  |        | Deg       |

| LX2 Discharge Resistance           |           |                                                                                   |      | 50   |        | $\Omega$  |

| Soft-Start Time                    |           |                                                                                   |      | 1    |        | ms        |

| Dead Time                          |           | $I_{OUT} = 500mA$                                                                 |      | 2    |        | ns        |

| LX Rise/Fall Time                  |           | $I_{OUT} = 500mA$                                                                 |      | 2    |        | ns        |

**Electrical Characteristics (continued)**

( $V_{SUP1} = 13.5V$ ,  $V_{EN23} = V_{EN4} = V_{BIAS}$ ,  $V_{OUT1} = V_{PV2} = V_{PV3} = V_{PV4} = 3.1V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise noted, Typical values are at  $T_A = 25^{\circ}C$ . (Notes 3 and 4))

| PARAMETER                          | SYMBOL     | CONDITIONS                                                                                                                              | MIN  | TYP     | MAX    | UNITS       |

|------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|---------|--------|-------------|

| <b>OUT3 (LV BUCK)</b>              |            |                                                                                                                                         |      |         |        |             |

| Voltage Accuracy                   |            | $3.0V \leq PV3 \leq 5V$ , $I_{OUT1} = 0$ to $500mA$ , $V_{OUT1} = 1.8V$ , $1.1V$                                                        | -1.5 |         | 1.5    | %           |

| Output Range                       |            | 12.5mV steps (Note 2)                                                                                                                   | 0.8  |         | 3.9875 | V           |

| High-Side pMOS On-Resistance       |            | $I_{LX1} = 0.2A$                                                                                                                        |      | 180     |        | $m\Omega$   |

| Low-Side nMOS On-Resistance        |            | $I_{LX1} = 0.2A$                                                                                                                        |      | 70      |        | $m\Omega$   |

| High-Side Current- Limit Threshold |            | 1A OPTION                                                                                                                               | 0.80 | 1.07    | 1.40   | A           |

|                                    |            | 2A OPTION                                                                                                                               | 1.60 | 2.30    | 2.90   |             |

| LX3 Leakage Current                |            | $T_A = +25^{\circ}C$                                                                                                                    |      | 0.1     |        | $\mu A$     |

| Switching Phase                    |            | In phase with BUCK1 (Note 2)                                                                                                            |      | 0       |        | Deg         |

| LX3 Discharge Resistance           |            |                                                                                                                                         |      | 50      |        | $\Omega$    |

| Soft-Start Time                    |            |                                                                                                                                         |      | 1       |        | ms          |

| Dead Time                          |            | $I_{OUT} = 200mA$ (Note 2)                                                                                                              |      | 2       |        | ns          |

| LX Rise/Fall Time                  |            | $I_{OUT} = 200mA$                                                                                                                       |      | 2       |        | ns          |

| <b>OUT4 (LDO)</b>                  |            |                                                                                                                                         |      |         |        |             |

| Supply Voltage Range               | $V_{PV4}$  |                                                                                                                                         | 2.7  | 5.5     |        | V           |

| Output Voltage Range               | $V_{OUT4}$ | 12.5mV steps (Note 2)                                                                                                                   | 0.8  |         | 3.9875 | V           |

| Voltage Accuracy                   | $V_{OUT4}$ | $I_{OUT4} = 0A$ to $150mA$ , $3.1V \leq PV4 \leq 5V$<br>(OUT4 voltage accuracy of $\pm 1.5\%$ is guaranteed between $2.5V$ and $3.5V$ ) | -1.5 |         | 1.5    | %           |

| Dropout                            |            | $I_{OUT4} = 0.15A$ , $V_{LDO4} = 2.7V$                                                                                                  |      | 180     |        | $mV$        |

| Current-Limit Threshold            |            |                                                                                                                                         |      | 0.35    |        | A           |

| PSRR                               |            | $V_{PV4} = 3.1V$ , $V_{OUT4} = 2.8V$ , $I_{OUT4} = 0.05A$ , $f = 1kHz$ (Note 2)                                                         |      | 50      |        | dB          |

| OUT4 Discharge Resistance          |            | OUT3 Disabled                                                                                                                           |      | 70      |        | $\Omega$    |

| Soft-Start Time                    |            |                                                                                                                                         |      | 1       |        | ms          |

| <b>OSCILLATOR</b>                  |            |                                                                                                                                         |      |         |        |             |

| Frequency                          | $f_{SW}$   | Internally generated                                                                                                                    | 2    | 2.2     | 2.4    | MHz         |

| Spread Spectrum                    |            | Factory OTP                                                                                                                             |      | $\pm 3$ |        | %           |

| <b>THERMAL OVERLOAD</b>            |            |                                                                                                                                         |      |         |        |             |

| Thermal Shutdown Temperature       |            | $T_J$ rising (Note 2)                                                                                                                   |      | 175     |        | $^{\circ}C$ |

| Thermal Shutdown Hysteresis        |            | (Note 2)                                                                                                                                |      | 15      |        | $^{\circ}C$ |

## Electrical Characteristics (continued)

( $V_{SUP1} = 13.5V$ ,  $V_{EN23} = V_{EN4} = V_{BIAS}$ ,  $V_{OUT1} = V_{PV2} = V_{PV3} = V_{PV4} = 3.1V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise noted, Typical values are at  $T_A = 25^{\circ}C$ . (Notes 3 and 4))

| PARAMETER                       | SYMBOL     | CONDITIONS                            | MIN   | TYP   | MAX  | UNITS     |

|---------------------------------|------------|---------------------------------------|-------|-------|------|-----------|

| <b>RESET</b>                    |            |                                       |       |       |      |           |

| OV Threshold                    |            | Rising                                | 102.4 | 105.5 | 108  | %         |

|                                 |            | Rising (Contact Factory for Option)   | 102.4 | 103.7 | 105  |           |

| UV Threshold                    |            | Falling                               | 92    | 94.5  | 97.6 | %         |

|                                 |            | Falling (Contact Factory for Option)  | 95    | 96.3  | 97.6 |           |

| Active Hold Period              |            | Factory OTP                           |       | 18    |      | ms        |

| Output Low Level                |            | 3mA                                   |       | 0.2   |      | V         |

| Output Current Drive at Levels  |            |                                       |       | 3     |      | mA        |

| Leakage                         |            | $T_A = +25^{\circ}C$ (open-drain)     |       | 1     |      | $\mu A$   |

| Comparator Delay for Deviation  |            |                                       |       | 60    |      | $\mu s$   |

| <b>Enable Input (EN23, EN4)</b> |            |                                       |       |       |      |           |

| Input High Level                | $V_{IH}$   | Not to exceed $V_{BIAS}$              | 1.4   |       |      | V         |

| Input Low Level                 | $V_{IL}$   |                                       |       | 0.5   |      | V         |

| Input Hysteresis                | $V_{IHYS}$ |                                       | 0.1   |       |      | V         |

| Input Leakage Current           | $I_{LKG}$  | $V_{EN} = 5.5V$ , $T_A = 25^{\circ}C$ | 9.5   |       |      | $\mu A$   |

| Pulldown resistance             |            |                                       | 580   |       |      | $k\Omega$ |

**Note 2:** Guaranteed by design; not production tested.

**Note 3:** Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage are guaranteed by design and characterization.

**Note 4:** The device is designed for continuous operation up to  $T_J = +125^{\circ}C$  for 95,000 hours and  $T_J = +150^{\circ}C$  for 5,000 hours.

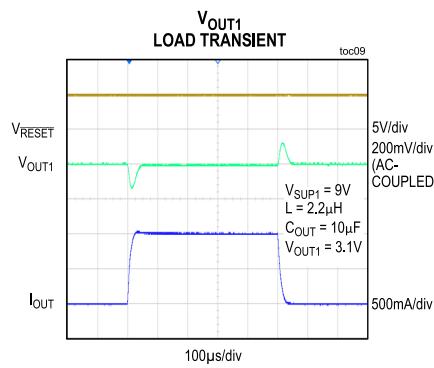

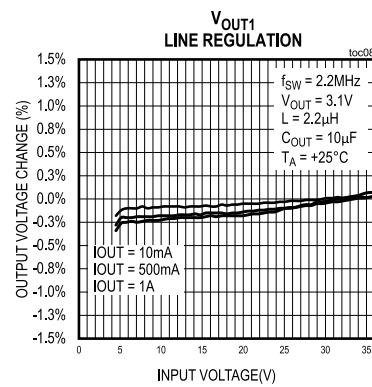

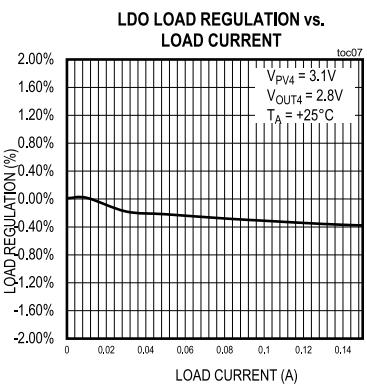

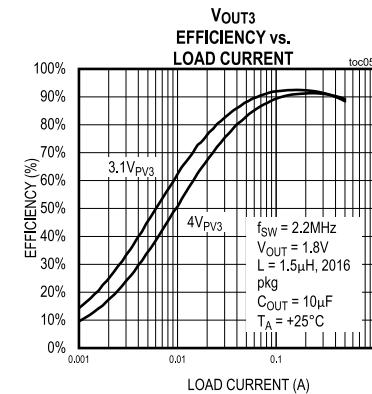

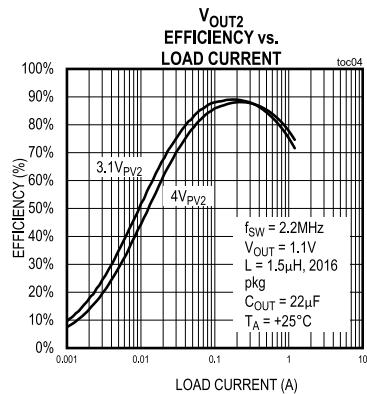

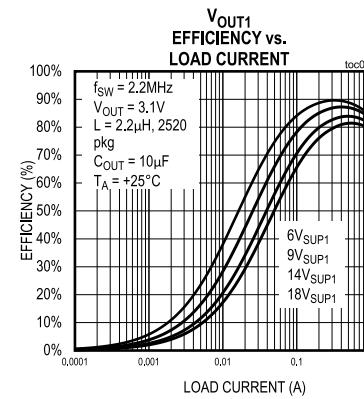

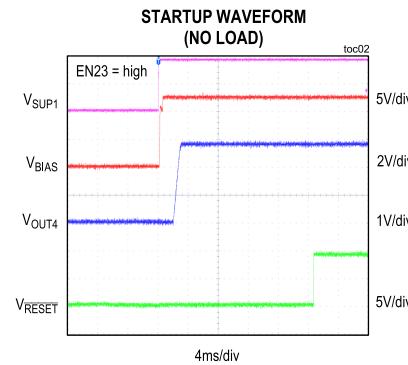

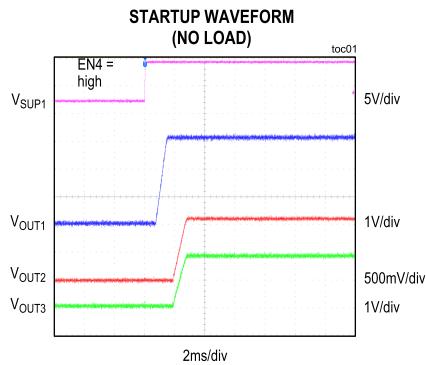

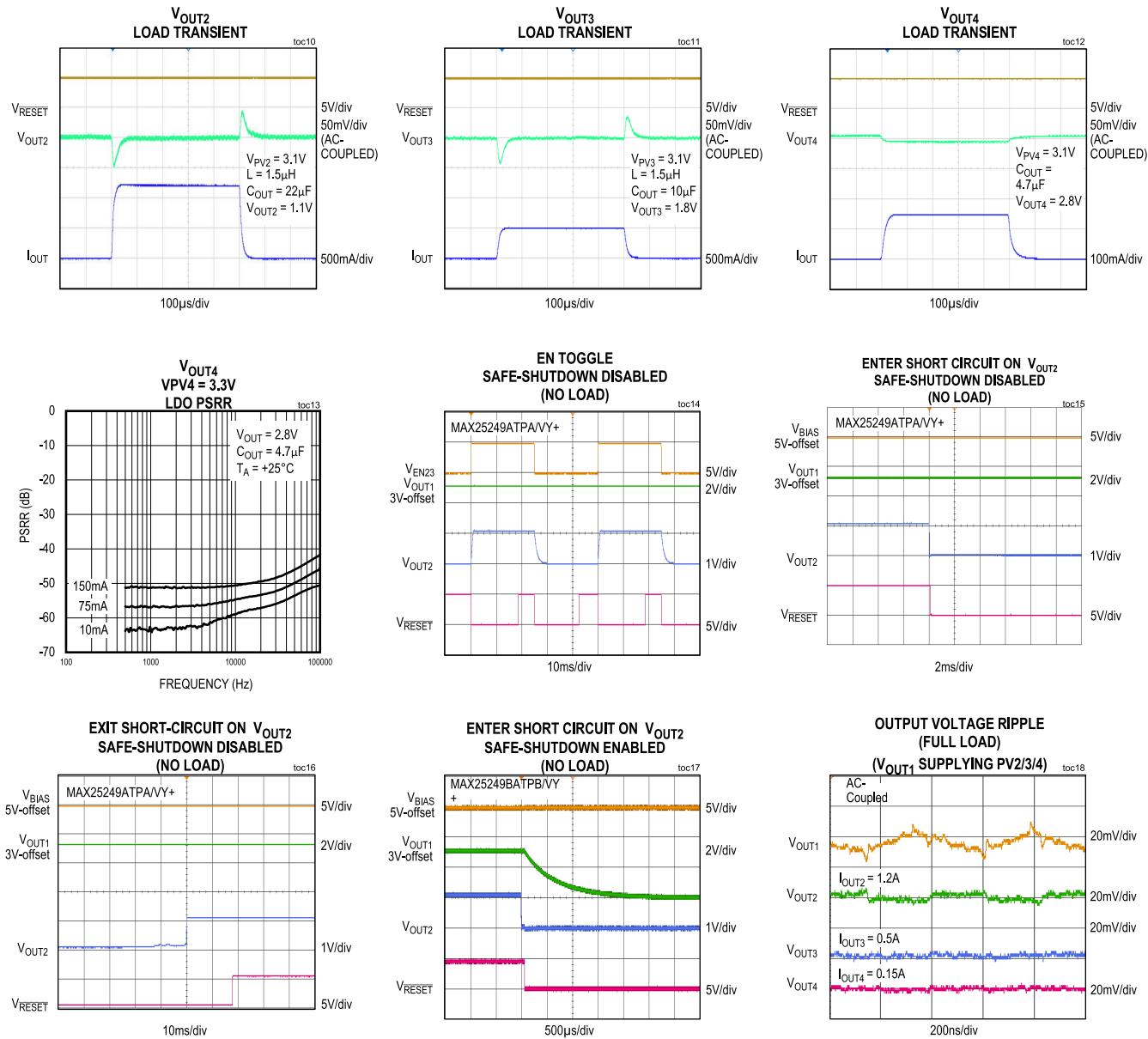

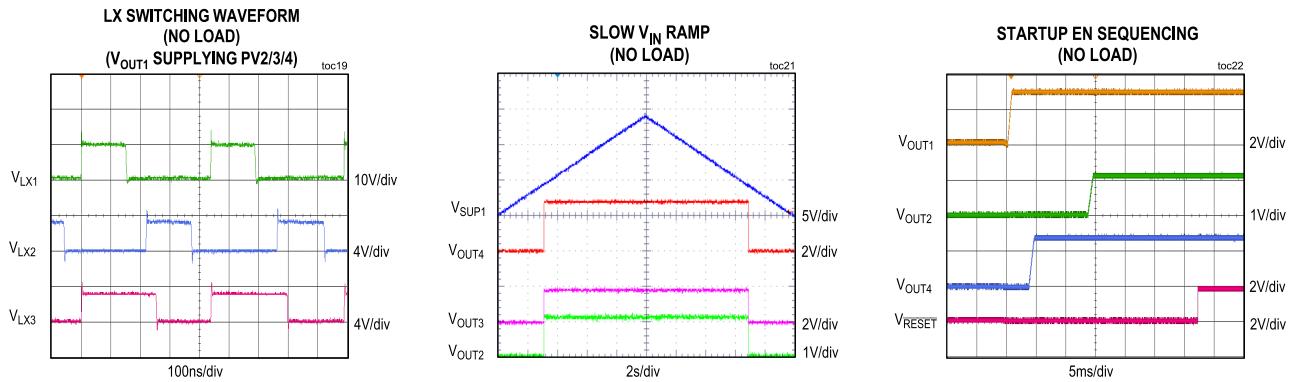

## Typical Operating Characteristics

( $V_{SUP} = 9V$ ,  $T_A = 25^\circ C$ , unless otherwise noted)

## Typical Operating Characteristics (continued)

(V<sub>SUP</sub> = 9V, T<sub>A</sub> = 25°C, unless otherwise noted)

## Typical Operating Characteristics (continued)

( $V_{SUP} = 9V$ ,  $T_A = 25^\circ C$ , unless otherwise noted)

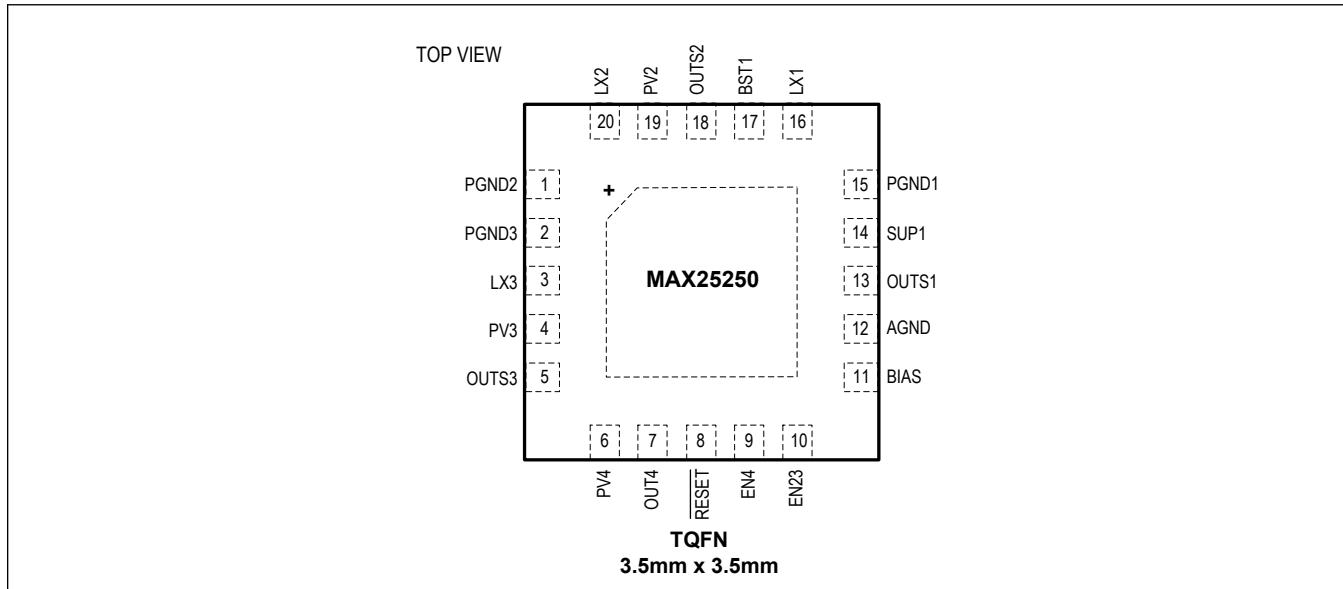

## Pin Configuration

## Pin Description

| PIN | NAME  | FUNCTION                                              |

|-----|-------|-------------------------------------------------------|

| 1   | PGND2 | Power Ground for OUT2. Connect all PGND pins together |

| 2   | PGND3 | Power Ground for OUT3. Connect all PGND pins together |

| 3   | LX3   | Inductor Connection for BUCK3                         |

| 4   | PV3   | Input Voltage for BUCK3                               |

| 5   | OUTS3 | BUCK3 Output Voltage-Sense Input                      |

| 6   | PV4   | Input Voltage for LDO4                                |

### Pin Description (continued)

| PIN | NAME                      | FUNCTION                                                                                                                                                                                                    |

|-----|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OUT4                      | LDO4 Output. Place a 4.7 $\mu$ F or larger X7R ceramic capacitor as close as possible from OUT4 to PGND.                                                                                                    |

| 8   | $\overline{\text{RESET}}$ | Open-Drain $\overline{\text{RESET}}$ Output. This output remains low for the 18ms hold time (factory OTP) after all outputs have reached their regulation level (See the Electrical Characteristics table). |

| 9   | EN4                       | Low-Voltage-Compatible Enable Input for LDO4. Pull low to turn off LDO4. Pull high to turn on LDO4.                                                                                                         |

| 10  | EN23                      | Low-Voltage-Compatible Enable Input for BUCK2 and BUCK3. Pull low to turn off both bucks. Pull high to turn on both bucks. Delay between BUCK2 and BUCK3 is factory-programmed (0ms, 1ms, 3ms, 10ms).       |

| 11  | BIAS                      | 5V Regulator Output. Bypass to AGND with a 2.2 $\mu$ F or larger X7R ceramic capacitor.                                                                                                                     |

| 12  | AGND                      | Analog Ground. Connect to the ground plane near the exposed pad.                                                                                                                                            |

| 13  | OUTS1                     | BUCK1 Output Voltage-Sense Input                                                                                                                                                                            |

| 14  | SUP1                      | IC Supply-Voltage Input and High-Side Connection for BUCK1. Connect a 4.7 $\mu$ F or larger X7R ceramic capacitor from SUP1 to PGND1.                                                                       |

| 15  | PGND1                     | Power Ground for BUCK1. Connect all PGND pins together.                                                                                                                                                     |

| 16  | LX1                       | Inductor Connection for BUCK1                                                                                                                                                                               |

| 17  | BST1                      | Bootstrap Capacitor Connection for BUCK1. Connect a 0.1 $\mu$ F X7R ceramic capacitor between BST and LX1.                                                                                                  |

| 18  | OUTS2                     | BUCK2 Output Voltage-Sense Input                                                                                                                                                                            |

| 19  | PV2                       | Voltage Input for BUCK2                                                                                                                                                                                     |

| 20  | LX2                       | Inductor Connection for BUCK2                                                                                                                                                                               |

| -   | EP                        | Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical connection point.                                                  |

## Functional Diagram

## Detailed Description

### Summary

The MAX25250 is a high-efficiency, four-output PMIC using three DC-DC converters, and a high-PSRR LDO, with OV/UV monitoring on all outputs. OUT1 is a 1A high-voltage synchronous step-down converter that operates from power over coax or car battery. OUT2 and OUT3 low-voltage synchronous step-down converters operate from OUT1 and provide a 0.8V to 3.9875V output voltage range. OUT2 can deliver 1.2A for high megapixel cameras and high-speed serializers. OUT3 can deliver 1.2A to power the secondary rails of the imager, serializer, and micro. OUT4 is a low-voltage, low-noise, high-PSRR LDO for imager power. All buck outputs achieve  $\pm 2\%$  output error over load, line, and temperature range. Overvoltage and undervoltage faults are monitored with  $\pm 1.3\%$  accuracy around the set voltage and errors are communicated through RESET.

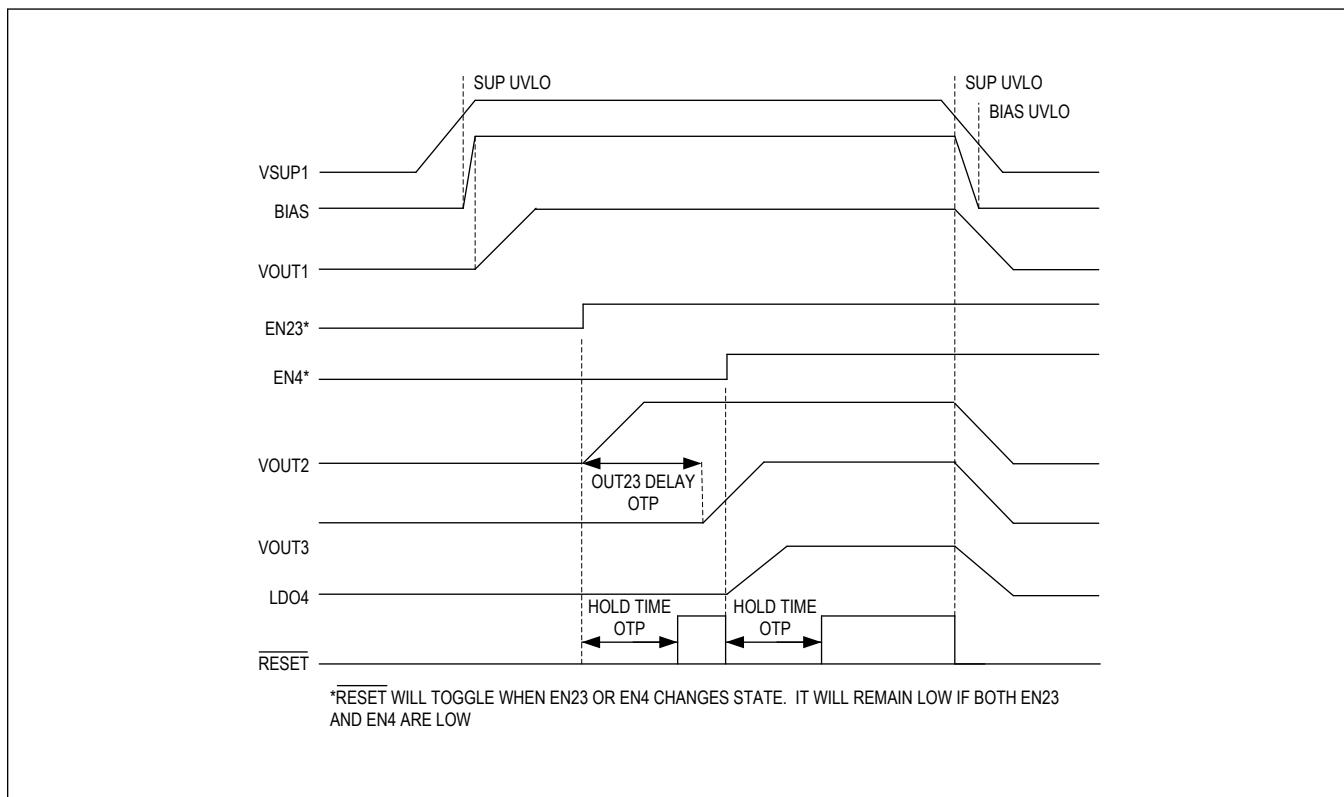

### Startup Timing and Soft-Start

V<sub>OUT1</sub> has a soft-start time of 0.75ms and the other channels start up in 1ms. The sequencing is controlled by the EN23 and EN4 pins, as well as the factory OTP set delay time between the V<sub>OUT2</sub> and V<sub>OUT3</sub>. For the MAX25250, RESET will toggle high as long as either EN23 or EN4 are high. Whenever an EN pin changes state, RESET will toggle. See [Figure 1](#).

Figure 1. Startup Timing Diagram

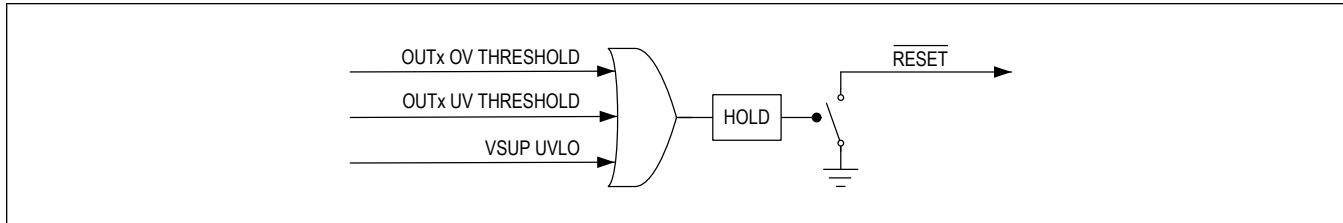

Figure 2. Simplified  $\overline{\text{RESET}}$  Logic Diagram

### RESET Output

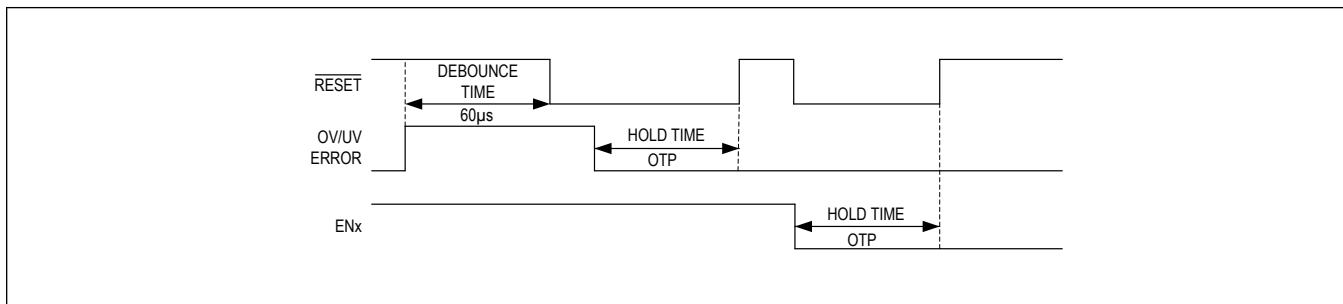

The device is configured with an open-drain  $\overline{\text{RESET}}$  output that asserts low when any of the output voltages are outside of the UV/OV window, or when the supply voltage falls below the UV threshold. After all, voltages reach the regulated voltage during startup,  $\overline{\text{RESET}}$  remains asserted low for an 18ms hold time (factory OTP option of 4.5ms, 9ms, or 18ms). Besides,  $\overline{\text{RESET}}$  is designed to toggle and remain low for the hold time when one or both of the EN pins are de-asserted. The timing is shown in [[RESET During Normal Operation]]. This pin can be used as an interrupt for an MCU or error-monitoring device to alert the system that a fault has occurred.

Figure 3. RESET During Normal Operation

### Active Pulldown

BUCK2, BUCK3, and LDO4 contain pulldown resistors that activate during shutdown when EN23 or EN4 are toggled low, or if there is a fault that triggers safe shutdown. During startup, if one of the outputs is pre-biased, the pulldown is activated until the rail drops to 0V, at which point the soft-start of the rails begins. This ensures proper sequencing of the rails if there is a long glitch on SUP1.

### OV/UV Comparators

All four rails are monitored with overvoltage and undervoltage comparators at the feedback node. These comparators are tested at startup and provide continuous monitoring of output voltages during normal operation. If an error exists, then  $\overline{\text{RESET}}$  is pulled low until the OV/UV condition is resolved. The comparators have a built-in filter time (60µs), which prevents short transient voltages that exceed OV/UV threshold from triggering  $\overline{\text{RESET}}$ .

### Spread-Spectrum Option

The IC has a factory-programmable spread spectrum that varies the internal operating frequency by  $\pm 3\%$ , relative to 2.2MHz (typ). Spread spectrum is offered to improve EMI performance of the devices.

### Thermal Shutdown

If an overtemperature condition is detected during power sequencing, the startup will cease and outputs will enter thermal shutdown. Once the temperature is reduced, power sequencing will be restarted. The startup check routine is not re-initiated. If safe shutdown is enabled, the IC will shut down when overtemperature is detected and remain in this state even if the part cools down. The device must be restarted through input power cycling.

## Applications Information

### Output-Voltage Selection

Output voltages are set at the factory. Default configurations can be found in the [Ordering Information](#).

Other options are available as follows:

**Table 1. Output Voltage Options**

| OUTPUT | VOLTAGE (V) | STEP SIZE (mV) |

|--------|-------------|----------------|

| BUCK1  | 3–4, 5      | 50             |

| BUCK2  | 0.8–3.9875  | 12.5           |

| BUCK3  | 0.8–3.9875  | 12.5           |

| LDO4   | 0.8–3.9875  | 12.5           |

### Input Capacitor

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. A 1 $\mu$ F or larger X7R ceramic capacitor is recommended for PV2, PV3, and PV4 pins. For the PV pin, a 4.7 $\mu$ F or larger X7R ceramic capacitor minimum is recommended, and it can be adjusted based on application input-voltage-ripple requirements.

### Output Capacitor

The MAX25250 is designed to be stable with low-ESR ceramic capacitors. Other capacitor types are not recommended, as the ESR zero can affect the stability of the device. The phase margin must be measured on the final circuit to verify that proper stability is achieved. The minimum recommended value for each part number is shown in [Table 2](#).

**Table 2. Minimum Output Capacitor Selection**

| PART NUMBER      | C <sub>OUT1</sub> ( $\mu$ F) | C <sub>OUT2</sub> ( $\mu$ F) | C <sub>OUT3</sub> ( $\mu$ F) | C <sub>OUT4</sub> ( $\mu$ F) |

|------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| MAX25250ATPA/VY+ | 10                           | 10                           | 10                           | 4.7                          |

### Inductor Selection

The MAX25250 is optimized to be used with inductor values shown in [Table 3](#). These were selected for power-over-coax and car-battery input voltages and common camera-output voltages. Camera systems are space-constrained and require a trade-off in saturation current, case size, and inductor ripple current. The DCR of the inductor plays a major part in the overall system efficiency.

**Table 3. Inductor Selection**

| PART NUMBER      | L1  | L2  | L3  |

|------------------|-----|-----|-----|

| MAX25250ATPA/VY+ | 2.2 | 1.5 | 1.5 |

### PCB Layout Guidelines

Careful PCB layout is critical to achieve low switching-power loss and clean, stable operation. The MAX25250 EV kit layout should be used as a reference when creating the board layout. Use a multilayer board for better noise immunity and thermal performance. Follow the guidelines below for a good PCB layout:

- Place the input capacitor immediately adjacent to the SUP1 and PV1, PV2, and PV3 pins. Since the IC operates at 2.2MHz switching frequency, this placement is critical for effective decoupling of high-frequency noise from the SUP\_ pins.

- Solder the exposed pad to a large copper-plane area under the device. To effectively use this copper area as a heat exchanger between the PCB and ambient, expose the copper area on the top and bottom side. Add vias on the copper

pad for efficient heat transfer. Connect the exposed pad to the ground plane, ideally at the return terminal of the output capacitor.

- Isolate the power components and high-current paths from sensitive analog circuitry.

- Keep the high-current paths short, especially at the ground terminals. This practice is essential for stable, jitter-free operation.

- Connect PGND and AGND together, preferably at the return terminal of the output capacitor.

- Keep the power traces and load connections short. This practice is essential for high efficiency. Use thick copper PCB to enhance full-load efficiency and power-dissipation capability.

- Route high-speed switching nodes away from sensitive analog areas. Use internal PCB layers as PGND\_ to act as EMI shields, keeping radiated noise away from the device and analog bypass capacitor.

## Ordering Information

| PART NUMBER          | V <sub>OUT1</sub><br>(V) | V <sub>OUT2</sub><br>(V) | V <sub>OUT3</sub><br>(V) | V <sub>OUT4</sub><br>(V) | ILIM<br>OUT2/<br>3<br>(A) | SPREAD<br>SPECTRUM | RESET         | SAFETY<br>MODE | EN<br>TIMER<br>(ms)<br>(1) | OUT23<br>DELAY<br>(ms) (2) | RESET<br>HOLD<br>TIME<br>(ms) (1) |

|----------------------|--------------------------|--------------------------|--------------------------|--------------------------|---------------------------|--------------------|---------------|----------------|----------------------------|----------------------------|-----------------------------------|

| MAX25250ATPA/<br>VY+ | 3.75                     | 1.2                      | 1.8                      | 3.3                      | 1.2 /<br>1.2              | ON                 | Open<br>Drain | RESET<br>only  | N/A                        | 0                          | 18                                |

/V Denotes an automotive-qualified part.

+ Denotes a lead(Pb)-free/RoHS-compliant package.

Y = Side-wettable package.

**Note:** Contact factory for custom configuration. Factory-selectable features include the following:

(1) Startup EN Timer,  $\overline{\text{RESET}}$  Hold Time: 5ms, 10ms, 18ms

(2) OUT23 Delay: 0ms, 1ms, 3ms, 10 ms

## Revision History

| REVISION NUMBER | REVISION DATE | DESCRIPTION              | PAGES CHANGED |

|-----------------|---------------|--------------------------|---------------|

| 0               | 4/21          | Release for Market Intro | —             |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at <https://www.maximintegrated.com/en/storefront/storefront.html>.

*Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.*

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[Maxim Integrated:](#)

[MAX25250ATPA/VY+](#)