## MAX20342

# USB Type-C Charger Detector with Integrated OVP

### General Description

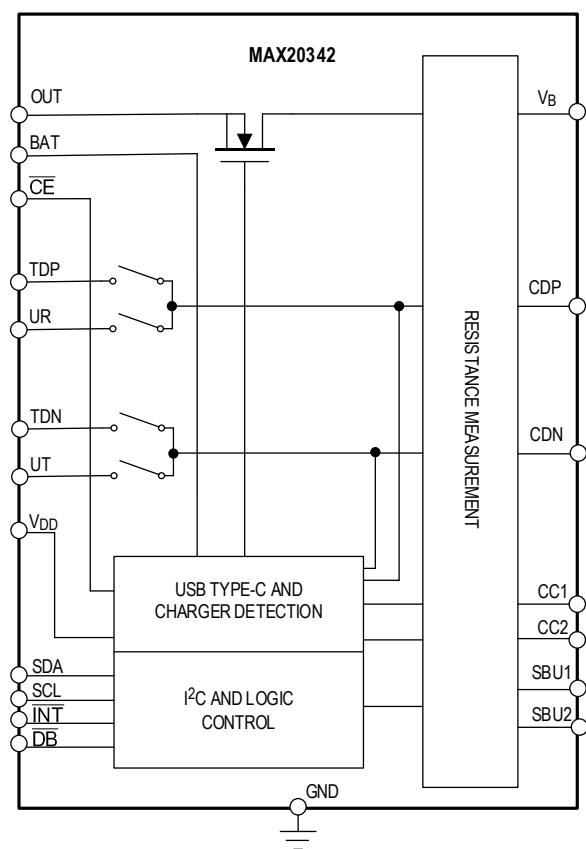

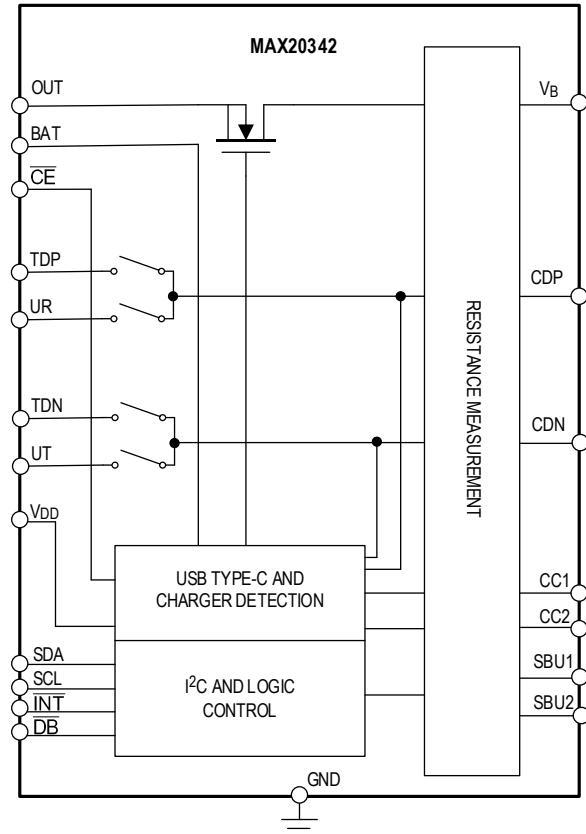

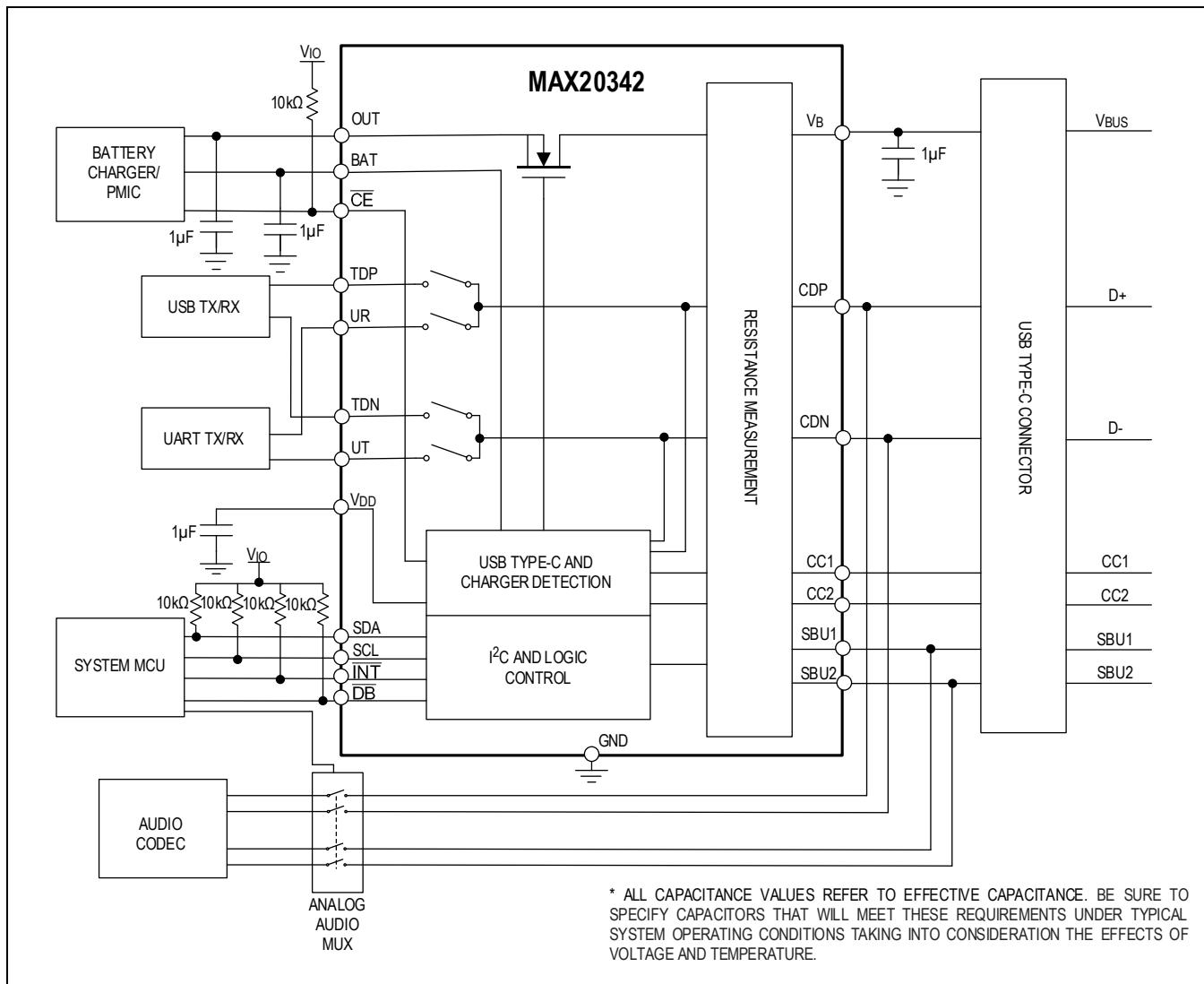

The MAX20342 is a USB Type-C® charger detector that is also capable of detecting chargers compliant with the USB Battery Charging Specification Revision 1.2. The USB Type-C charger detection circuitry functions as a UFP or DRP depending on factory configuration.

The device implements USB Type-C detection logic and enables systems to support charging based on USB Type-C ports. The device also includes charger detection capability for BC1.2 compatible chargers and detects USB standard downstream ports (SDPs), USB charging downstream ports (CDPs), dedicated charger ports (DCPs), and other proprietary chargers. GPIO outputs allow the MAX20342 to control an external lithium-ion (Li+) battery charger based on charger detection results.

The MAX20342 integrates a resistance detection block that can be used to automatically configure factory configuration states based upon attached resistors. Additionally, the resistance measurement can be configured to detect the presence of moisture in the USB Type-C connector.

The MAX20342 also features an integrated low on-resistance, low-capacitance double-pole double-throw (DPDT) USB switch that can pass Hi-Speed USB, full-speed USB, low-speed USB, and UART signals. The switch position can be automatically configured by the USB detection logic or manually controlled.

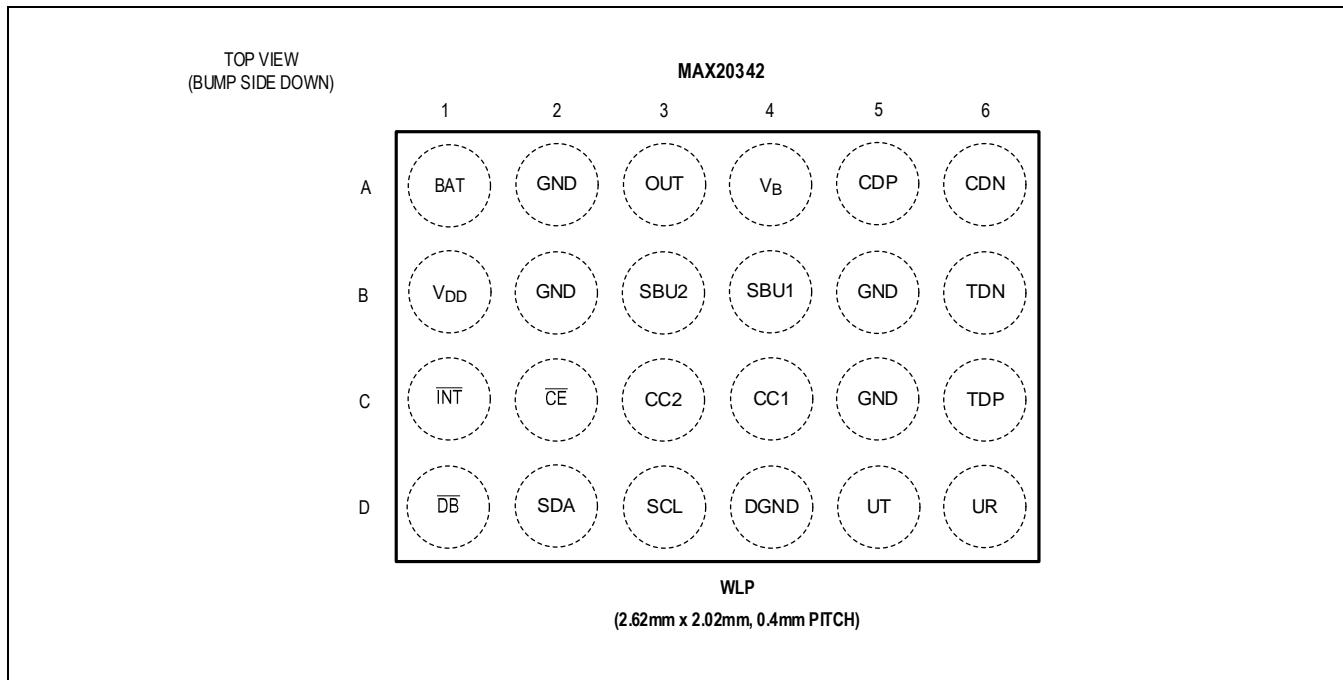

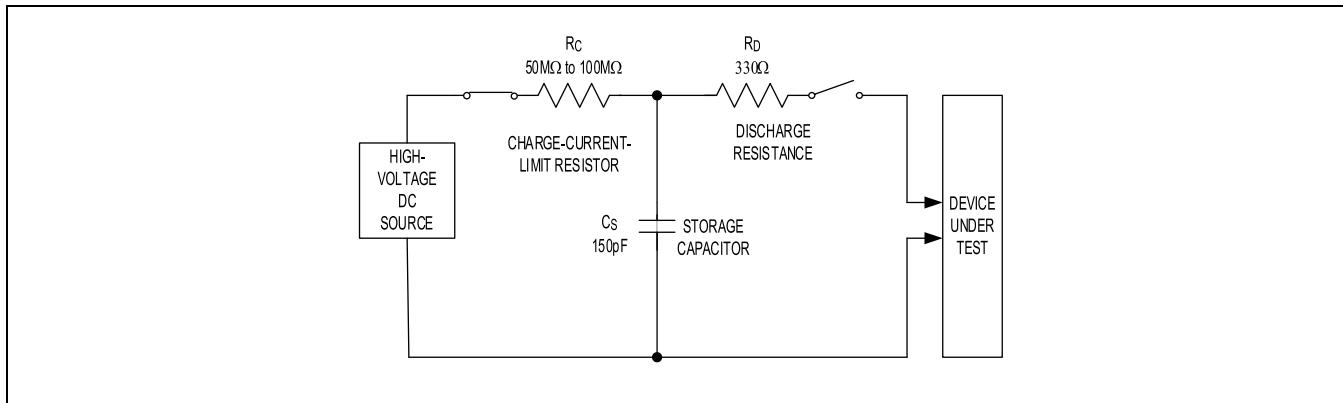

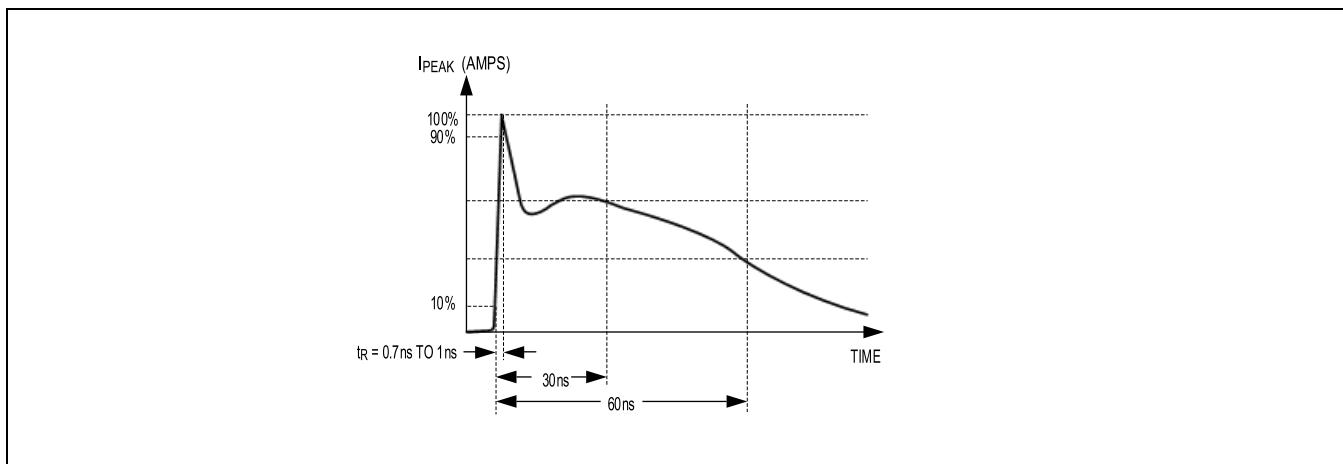

The MAX20342 features high-ESD protection up to  $\pm 15\text{kV}$  human-body model (HBM) on CC1, CC2, SBU1, and SBU2 pins. The CDP and CDN pins are protected against ESD up to  $\pm 6\text{kV}$ . The MAX20342 is specified for  $\pm 15\text{kV}$  Air-Gap and  $\pm 8\text{kV}$  Contact Discharge IEC 61000-4-2 on the CC1, CC2, SBU1, and SBU2 pins. The MAX20342 is available in a 24-bump, 0.4mm pitch, 2.62mm x 2.02mm wafer-level package (WLP) and operates over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  extended temperature range.

### Applications

- DSCs and Camcorders

- Tablets

- Smartphones

- e-Readers

USB Type-C® is a registered trademark of USB Implementers Forum.

Apple is a registered trademark of Apple Inc.

Samsung is a registered trademark of Samsung Electronics Co., Ltd

### Benefits and Features

- Low Power Consumption

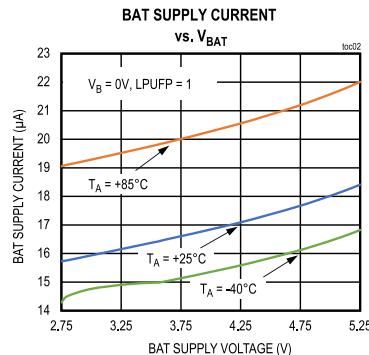

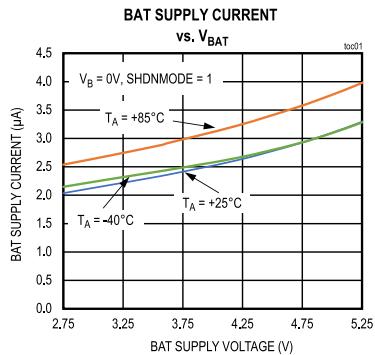

- Battery Standby Current  $17\mu\text{A}$  (typ)

- Battery Shutdown Current  $2.5\mu\text{A}$  (typ)

- Delivers USB Compliance and Flexibility

- Compliant with USB Type-C Specification Revision 1.3

- Supports USB Battery Charger Specification Revision 1.2

- Detects Proprietary Chargers such as Apple® and Samsung®

- Simplifies Complex System Designs

- Integrated Overvoltage Protection

- Negative Swing Audio Capable Hi-Speed USB/UART Switches

- Automatic Switch and Charger Interface Control

- Full Control through I<sup>2</sup>C Interface

- Interrupts for Device Status Changes

- Improves Quality and Reliability

- Automatic Factory Mode Configuration

- USB Type-C Port Moisture Detection

- Low-Corrosion DRP Mode

- Robust Protection

- $V_B$  Connection Withstands up to  $+30\text{V}$

- $V_B$  Surge Protection up to  $\pm 120\text{V}$

- $\pm 15\text{kV}$  HBM ESD Protection on CC1, CC2, SBU1 and SBU2 Pins

- $\pm 6\text{kV}$  HBM ESD Protection on CDP and CDN Pins

- $\pm 15\text{kV}$  Air-Gap IEC 61000-4-2 on CC1, CC2, SBU1, and SBU2 Pins

- $\pm 8\text{kV}$  Contact Discharge IEC 61000-4-2 on CC1, CC2, SBU1, and SBU2 Pins

- Saves Board Space

- 2.62mm x 2.02mm WLP Package

*Ordering Information appears at end of data sheet.*

## Simplified Block Diagram

**Absolute Maximum Ratings**

|                                                                             |                |

|-----------------------------------------------------------------------------|----------------|

| $V_B$ to GND .....                                                          | -0.3V to +30V  |

| $V_B$ to OUT .....                                                          | -0.3V to +26V  |

| OUT to GND .....                                                            | -0.3V to +7.5V |

| BAT to GND .....                                                            | -0.3V to +6.0V |

| $\overline{INT}$ , SDA, SCL, $\overline{CE}$ , $\overline{DB}$ to GND ..... | -0.3V to +6.0V |

| CDN, CDP to GND .....                                                       | -0.3V to +6.0V |

| CDN, CDP to GND (AudioCPEn enabled, switches off)...                        | -3.0V to +6.0V |

| SBU1, SBU2 to GND .....                                                     | -0.3V to +6.0V |

| CC1, CC2 to GND (Note 1).....                                               | -0.3V to +6.0V |

| TDN, TDP to GND.....                                                        | -0.3V to +6.0V |

| UT, UR to GND .....                                                         | -0.3V to +6.0V |

|                                                                                                                                                 |                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| $V_{DD}$ to GND .....                                                                                                                           | -0.3V to +2.2V                                |

| Continuous Power Dissipation (Multilayer Board) ( $T_A = +70^\circ\text{C}$ , derate 18.85mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ )..... | 1.508W                                        |

| Continuous Current into $V_B$ , OUT .....                                                                                                       | 2000mA                                        |

| Current into $V_B$ , OUT ( $T_A = +70^\circ\text{C}$ , 1500 hours) .....                                                                        | 3000mA                                        |

| Continuous Current into CC1, CC2 .....                                                                                                          | 600mA                                         |

| Continuous Current into any other terminal .....                                                                                                | 100mA                                         |

| Operating Temperature Range.....                                                                                                                | -40 $^\circ\text{C}$ to +85 $^\circ\text{C}$  |

| Junction Temperature Range .....                                                                                                                | -40 $^\circ\text{C}$ to +150 $^\circ\text{C}$ |

| Storage Temperature Range .....                                                                                                                 | -40 $^\circ\text{C}$ to +150 $^\circ\text{C}$ |

| Soldering Temperature (reflow).....                                                                                                             | +260 $^\circ\text{C}$                         |

**Note 1:** CC1 and CC2 pins can withstand a short to +20V with a series 10k $\Omega$  resistor (sinking 2mA). Continuous Current is guaranteed for 100,000 hours at  $T_A = 120^\circ\text{C}$ . Throughout the data sheet, Current refers to the aforementioned condition of Continuous Current.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Information****24-WLP**

|                                             |                                                |

|---------------------------------------------|------------------------------------------------|

| Package Code                                | W242A2+1                                       |

| Outline Number                              | <a href="#">21-100430</a>                      |

| Land Pattern Number                         | Refer to <a href="#">Application Note 1891</a> |

| <b>THERMAL RESISTANCE, FOUR LAYER BOARD</b> |                                                |

| Junction-to-Ambient ( $\theta_{JA}$ )       | 53.04 $^\circ\text{C}/\text{W}$                |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](#). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](#).

**Electrical Characteristics**

( $V_{BAT} = 3.6V$ ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                         | SYMBOL             | CONDITIONS                                                                                  | MIN   | TYP  | MAX | UNITS |

|---------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------|-------|------|-----|-------|

| <b>GENERAL ELECTRICAL CHARACTERISTICS</b>         |                    |                                                                                             |       |      |     |       |

| Supply Voltage Range Output                       | VBAT               |                                                                                             | 2.75  | 5.5  |     | V     |

| Supply Voltage Range Input                        | VB                 |                                                                                             | 4.4   | 28.0 |     | V     |

| Internal VB Regulator Voltage                     | VB_REG             |                                                                                             |       | 3.75 |     | V     |

| Internal VCCINT Switchover Rising Threshold       | VCCINT_SW_OVER_THR | VCCINTOnBAT = '0', measured as (VB_REG - VBAT) rising, VCCINT = VB_REG above this threshold |       | 180  |     | mV    |

| Internal VCCINT Switchover Falling Threshold      | VCCINT_SW_OVER_THF | VCCINTOnBAT = '0', measured as (VB_REG - VBAT) falling, VCCINT = VBAT below this threshold  |       | 50   |     | mV    |

| Internal VCCINT POR Rising Threshold              | VCCINT_POR         | Measured on internal VCCINT rising                                                          |       | 1.81 |     | V     |

| Internal VCCINT POR Threshold Hysteresis          | VCCINT_POR_HYS     | Measured on internal VCCINT                                                                 |       | 150  |     | mV    |

| VDD Output Voltage                                | VDD                | IDD = 20mA                                                                                  | 1.7   | 1.8  | 1.9 | V     |

| VDD Undervoltage Lockout Rising Threshold         | VDD_UVLO           | VDD rising                                                                                  |       | 1.62 |     | V     |

| VDD Undervoltage Lockout Threshold Hysteresis     | VDD_UVLO_HYS       |                                                                                             |       | 100  |     | mV    |

| BAT Shutdown Quiescent Current                    | IBAT_SHDN          | ShdnMode = '1', VBAT = 3.6V                                                                 | 2.5   | 4.2  |     | µA    |

| BAT Low-Power UFP Quiescent Current               | IBAT_LP_UFP        | LPUFP = '1', moisture detection enabled, VBAT = 3.6V, VB = 0.0V                             | 16.4  | 27.0 |     | µA    |

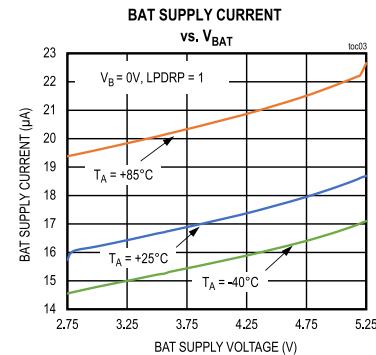

| BAT Low-Power Low-Corrosion DRP Quiescent Current | IBAT_LP_DRP        | LPDRP = '1', moisture detection enabled, DRP toggling state, VBAT = 3.6V, VB = 0.0V         | 16.7  | 28.0 |     | µA    |

| BAT UFP Quiescent Current                         | IBAT_UFP           | Moisture detection enabled, UFP state, VBAT = 3.6V, VB = 0.0V                               | 148.9 |      |     | µA    |

| BAT DFP Quiescent Current                         | IBAT_DFP           | Moisture detection enabled, DFP state, VBAT = 3.6V, VB = 0.0V                               | 181.8 |      |     | µA    |

| BAT DRP Quiescent Current                         | IBAT_DRP           | Moisture detection enabled, DRP toggling state, VBAT = 3.6V, VB = 0.0V                      | 166.3 |      |     | µA    |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                           | SYMBOL        | CONDITIONS                                                     | MIN   | TYP  | MAX  | UNITS     |

|---------------------------------------------------------------------|---------------|----------------------------------------------------------------|-------|------|------|-----------|

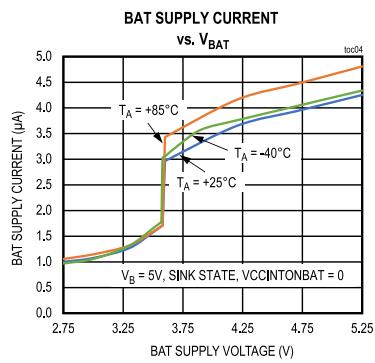

| BAT Quiescent Current with VB Present                               | IBAT_VB       | VCCINTOnBAT = '0', Attached Sink state, VBAT = 4.2V, VB = 5.0V | 3.2   |      |      | $\mu A$   |

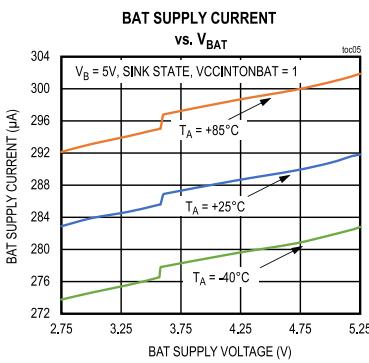

|                                                                     |               | VCCINTOnBAT = '1', Attached Sink state, VBAT = 4.2V, VB = 5.0V | 292.6 |      |      |           |

| BAT Undervoltage Lockout Rising Threshold                           | VBAT_UVLO     | VBAT rising                                                    | 2.73  | 2.80 | 2.85 | V         |

| BAT Undervoltage Lockout Threshold Hysteresis                       | VBAT_UVLO_HYS |                                                                |       | 100  |      | mV        |

| BAT Overvoltage Lockout Rising Threshold                            | VBAT_OVLO     | VBAT rising                                                    | 5.20  | 5.35 | 5.50 | V         |

| BAT Overvoltage Lockout Threshold Hysteresis                        | VBAT_OVLO_HYS |                                                                |       | 200  |      | mV        |

| Shutdown/Low-Power UFP CC1 and CC2 Pulldown Resistor                | RLP_UFP_PD    |                                                                |       | 40   |      | $k\Omega$ |

| Shutdown/Low-Power UFP CC1 and CC2 Detection Rising Threshold       | VLP_UFP_THR   | CC1/CC2 rising                                                 |       | 0.49 |      | V         |

| Shutdown/Low-Power UFP CC1 and CC2 Detection Falling Threshold      | VLP_UFP_THF   | CC1/CC2 falling                                                |       | 0.45 |      | V         |

| Low-Power Low-Corrosion CC1 and CC2 Detection Driving Resistor      | RLP_DRP_DET   |                                                                |       | 400  |      | $k\Omega$ |

| Low-Power Low-Corrosion DRP CC1 and CC2 Detection Rising Threshold  | VLP_DRPLC_THR | CC1/CC2 rising                                                 |       | 1.15 |      | V         |

| Low-Power Low-Corrosion DRP CC1 and CC2 Detection Falling Threshold | VLP_DRPLC_THF | CC1/CC2 falling                                                |       | 0.68 |      | V         |

| Shutdown CC1 and CC2 Detection Debounce Time                        | tSHDN_CCD_EB  |                                                                |       | 85   |      | $\mu s$   |

| Low-Power UFP/Low Corrosion DRP CC1                                 | tLP_CCDEB     |                                                                |       | 1    |      | ms        |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. )

| PARAMETER                                        | SYMBOL         | CONDITIONS                                                      | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------------------|----------------|-----------------------------------------------------------------|-------|-------|-------|-------|

| and CC2 Detection Debounce Time                  |                |                                                                 |       |       |       |       |

| Thermal Shutdown Rising Threshold                | TSHDN          | TJ rising                                                       |       | 165   |       | °C    |

| Thermal Shutdown Threshold Hysteresis            | TSHDN_HYS      |                                                                 |       | 15    |       | °C    |

| V <sub>B</sub> OVERVOLTAGE PROTECTOR             |                |                                                                 |       |       |       |       |

| VB Detect Threshold Rising Threshold             | VBDET          | VB rising                                                       | 4.19  | 4.30  | 4.40  | V     |

| VB Detect Threshold Hysteresis                   | VBDET_HYS      |                                                                 |       | 400   |       | mV    |

| VB Clamp Voltage                                 | VB_CLAMP       | IVB = 10mA                                                      |       | 35    |       | V     |

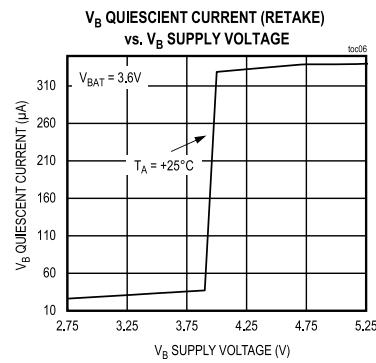

| VB Quiescent Current                             | IVB            |                                                                 |       | 360   |       | μA    |

| VB to OUT On-Resistance                          | RON_VB_OUT     | VB = 5.0V, IOUT = 100mA, TA = +25°C                             |       | 47    | 60    | mΩ    |

| VB Overvoltage Lockout Rising Threshold          | VB_OVLO        | VB rising                                                       | 5.790 | 5.852 | 5.915 | V     |

| VB Overvoltage Lockout Threshold Hysteresis      | VB_OVLO_HYS    |                                                                 |       | 25    |       | mV    |

| VB Detect Debounce Time                          | tVBDET_DEB     |                                                                 |       | 10    |       | ms    |

| VB Fault Recovering Debounce Time                | tVBFLT_DEB     | Applies to overvoltage event                                    |       | 10    |       | ms    |

| VB Soft-Start Time                               | tVB_SS         | Measured from VOUT = 10% x VB to VOUT = 90% x VB, COUT = 1000μF |       | 15    |       | ms    |

| VB-OUT Switch OK Time                            | tVB_OUT_SWT_OK | From soft-start end to VB_OUT switch interrupt OK               |       | 5     |       | ms    |

| VB Overvoltage Lockout Turn-Off Time             | tVB_OVLO_OFF   | From VB > VB_OVLO to VOUT stop rising, ROUT = 100Ω              |       | 100   |       | ns    |

| DFP MODE                                         |                |                                                                 |       |       |       |       |

| OUT Connected Current Limit Source               | IOUT_CUR_LIMIT |                                                                 |       |       | 2     | A     |

| OUT Connected Voltage Source                     | VOUT_LVL       |                                                                 |       |       | 5.5   | V     |

| USB TYPE-C                                       |                |                                                                 |       |       |       |       |

| USB TYPE-C/BC1.2 - PROPRIETARY CHARGER DETECTION |                |                                                                 |       |       |       |       |

| BC1.2 State Timeout                              | tTMO           |                                                                 | 180   | 200   | 220   | ms    |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. )

| PARAMETER                    | SYMBOL                | CONDITIONS                                                              | MIN   | TYP   | MAX  | UNITS     |

|------------------------------|-----------------------|-------------------------------------------------------------------------|-------|-------|------|-----------|

| Data Contact Detect Timeout  | tDCDtmo               | DCDCpl = 0b0                                                            | 1800  | 2000  | 2200 | ms        |

| Proprietary Charger Debounce | tPRDeb                |                                                                         | 5     | 7.5   | 10   | ms        |

| Primary to Secondary Timer   | tPDSWait              |                                                                         | 27    | 35    | 39   | ms        |

| Charger Detection Debounce   | tCDDeb                |                                                                         | 45    | 50    | 55   | ms        |

| VB64 Threshold               | VB64                  | CDP and CDN pins. Threshold in percent of VB voltage $3.8V < VB < 5.8V$ | 57    | 64    | 71   | %         |

| VB64 Hysteresis              | VB64_H                |                                                                         |       | 0.015 |      | V         |

| VB47 Threshold               | VB47                  | CDP and CDN pins. Threshold in percent of VB voltage $3.8V < VB < 5.8V$ | 43.3  | 47    | 51.7 | %         |

| VB47 Hysteresis              | VB47_H                |                                                                         |       | 0.015 |      | V         |

| VB31 Threshold               | VB31                  | CDP and CDN pins. Threshold in percent of VB voltage $3.8V < VB < 5.8V$ | 26    | 31    | 36   | %         |

| VB31 Hysteresis              | VB31_H                |                                                                         |       | 0.015 |      | V         |

| IWEAK Current                | IWEAK                 |                                                                         | 0.01  | 0.1   | 0.5  | $\mu A$   |

| RDM_DWN Resistor             | RDM_DWN               |                                                                         | 14.25 | 20    | 24.8 | $k\Omega$ |

| IDP_SRC Current              | IDP_SRC/ID_CD         | 0V to 2.5V                                                              | 7     | 10    | 13   | $\mu A$   |

| IDM_SINK Current             | IDM_SINK/I_DATSINK    | 0.15V to 3.6V                                                           | 50    | 80    | 110  | $\mu A$   |

| VLGC Threshold               | VLGC                  |                                                                         | 1.62  | 1.7   | 1.9  | V         |

| VLGC Hysteresis              | VLGC_H                |                                                                         |       | 0.015 |      | V         |

| VDAT_REF Threshold           | VDAT_REF              |                                                                         | 0.25  | 0.32  | 0.4  | V         |

| VDAT_REF Hysteresis          | VDAT_REF_H            |                                                                         |       | 0.015 |      | V         |

| VD33 Voltage                 | VDPDM_3P3_VSR/VSRC3_3 | With IDP_SRC = 0 to 200 $\mu A$                                         | 2.6   | 3.0   | 3.4  | V         |

| VSRC33ILIM Current Limit     | ILIMVSRC33            | $V_{CDP}/V_{CDN} = 1.6V$                                                |       | 1.5   | 3    | $mA$      |

| VDN_SRC Voltage              | VDN_SRC/V_SRC06       | 0 to 200 $\mu A$                                                        | 0.5   | 0.6   | 0.7  | V         |

| VDP_SRC Voltage              | VDP_SRC/V_SRC06       | 0 to 200 $\mu A$                                                        | 0.5   | 0.6   | 0.7  | V         |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                | SYMBOL          | CONDITIONS                                                   | MIN  | TYP   | MAX  | UNITS |

|------------------------------------------|-----------------|--------------------------------------------------------------|------|-------|------|-------|

| DP/DM Pulldown Resistor                  | RUSB            |                                                              | 3    | 6.1   | 12   | MΩ    |

| <b>USB TYPE-C/CC DETECTION</b>           |                 |                                                              |      |       |      |       |

| CC Pin Clamp Voltage                     | VCC_CLAMP_P     | $60\mu A \leq ICC1, ICC2 \leq 600\mu A$                      |      | 1.1   | 1.32 | V     |

| CC Pin Clamp Voltage (5.5V)              | VCC_CLAMP_P_5P5 | $ICC2, IICC2 < 2mA$                                          |      | 5.25  | 5.5  | V     |

| CC UFP Pulldown Resistance               | RPD_UFP         |                                                              | 4.59 | 5.10  | 5.61 | kΩ    |

| CC DFP 0.5A Current Source               | IDFP0.5_CC      |                                                              | -20% | 80    | +20% | μA    |

| CC DFP 1.5A Current Source               | IDFP1.5_CC      |                                                              | -8%  | 180   | +8%  | μA    |

| CC DFP 3A Current Source                 | IDFP3A_CC       |                                                              | -8%  | 330   | +8%  | μA    |

| CC RA RD Threshold                       | VRA_RD0.5       |                                                              | 0.15 | 0.2   | 0.25 | V     |

| CC RA RD Hysteresis                      | VRA_RD0.5_H     |                                                              |      | 0.015 |      | V     |

| CC UFP 0.5A RD Threshold                 | VUFP_RD0.5      |                                                              | 0.61 | 0.66  | 0.7  | V     |

| CC UFP 0.5A RD Hysteresis                | VUFP_RD0.5_H    |                                                              |      | 0.015 |      | V     |

| CC UFP 1.5A RD Threshold                 | VUFP_RD1.5      |                                                              | 1.16 | 1.23  | 1.31 | V     |

| CC UFP 1.5A RD Hysteresis                | VUFP_RD1.5_H    |                                                              |      | 0.015 |      | V     |

| CC DFP Vopen Detect Threshold            | VDFP_VOP_EN     |                                                              | 1.5  | 1.575 | 1.65 | V     |

| CC DFP Vopen Detect Hysteresis           | VDFP_VOP_EN_H   |                                                              |      | 0.030 |      | V     |

| CC DFP Vopen with 3.0A Detect Threshold  | VDFP_VOP_EN3A   |                                                              | 2.45 | 2.6   | 2.75 | V     |

| CC DFP Vopen with 3.0A Detect Hysteresis | VDFP_VOP_EN3A_H |                                                              |      | 0.030 |      | V     |

| CC V1P0 Threshold                        | VCC_V1P0        |                                                              | 0.92 | 1.00  | 1.08 | V     |

| CC V1P0 Hysteresis                       | VCC_V1P0_H      |                                                              |      | 0.015 |      | V     |

| VB Discharge Value Threshold             | VSAFE0V         | Falling voltage level where a connected UFP finds VB removed | 0.6  | 0.67  | 0.75 | V     |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. )

| PARAMETER                                        | SYMBOL           | CONDITIONS                                                                               | MIN  | TYP  | MAX | UNITS    |

|--------------------------------------------------|------------------|------------------------------------------------------------------------------------------|------|------|-----|----------|

| VB Discharge Value Hysteresis                    | VSAFE0V_H        | Rising hysteresis                                                                        |      | 45   |     | mV       |

| CC Pin Power-Up Time                             | tClampSwap       | Maximum time allowed from removal of voltage clamp till $5.1k\Omega$ resistor attached   |      | 15   |     | ms       |

| CC Detection Debounce                            | tCCDeb           |                                                                                          | 100  | 119  | 200 | ms       |

| USB Type-C Debounce                              | tPDDeb           |                                                                                          | 10   | 15   | 20  | ms       |

| USB Type-C Quick Debounce                        | tQDeb            |                                                                                          | 0.9  | 1    | 1.1 | ms       |

| VSAFE0V Debounce                                 | tVSAFE0VDebounce |                                                                                          | 9    | 10   | 11  | ms       |

| USB Type-C Error Recovery Delay                  | tErrorRecovery   |                                                                                          | 25   |      |     | ms       |

| USB Type-C DRP Toggle Time                       | tDRP             |                                                                                          | 50   | 75   | 100 | ms       |

| DFP Duty Cycle at DRP                            | DDRP_DCYC        | Programmable from 35% to 50% in 5% step, CCDRPPhase = 0b00                               |      | 35   |     | %        |

| USB Type-C DRP Try                               | tDRPtry          |                                                                                          | 90   | 100  | 110 | ms       |

| DRP Transition Time                              | tDRPTrans        | Time a role swap from DFP to UFP or reverse is completed                                 |      | 1    |     | ms       |

| VCONN Enable Time                                | tVCONNON         |                                                                                          |      | 2    |     | ms       |

| VCONN Disable Time                               | tVCONNOFF        | Time from UFP detached or as directed by I <sup>2</sup> C command until VCONN is removed |      | 35   |     | ms       |

| CC Pin Current Change Time                       | tSINKADJ         | Time from CC pin changes state in UFP mode till current drawn from DFP reaches new value |      | 60   |     | ms       |

| VB On Time                                       | tVBON            | Time from UFP is attached till VB ON                                                     |      | 275  |     | ms       |

| VB Off Time                                      | tVBOFF           | Time from UFP is detached till VB reaches VSAFE0V                                        |      | 650  |     | ms       |

| USB TYPE-C/V <sub>CONN</sub> SWITCH              |                  |                                                                                          |      |      |     |          |

| VCONN Source Requirements                        | VCONN            |                                                                                          | 3.0  | 5.5  |     | V        |

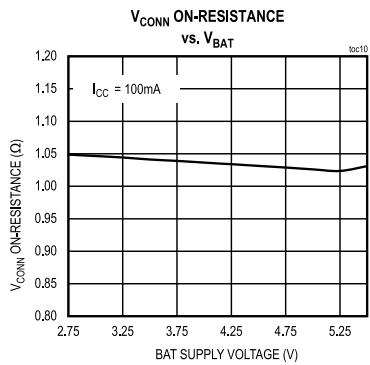

| VCONN Switch On Resistance                       | RON_VCON_SW      | VBAT = 4.2V, ICC = 0.1A                                                                  | 1.00 | 1.55 |     | $\Omega$ |

| VCONN Overcurrent Protection Thresholds Accuracy | IOCP_VCON_N_ACC  | VBAT = 4.2V, TA = +25 <sup>o</sup> C                                                     | -15  |      | +15 | %        |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                | SYMBOL           | CONDITIONS                                                                              | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-------|

| VCONN Short Circuit Current Protection Rising Threshold  | ISCCP_VCON_NN    | CC load current rising                                                                  | 0.425 | 0.500 | 0.575 | A     |

| VCONN Overcurrent Protection Threshold Programmable Step | IOCP_VCON_N_STEP | Programmable range is 200mA to 350mA                                                    |       | 50    |       | mA    |

| VCONN Overcurrent Protection Interrupt Debounce Time     | tOCP_VCON_N_DEB  | From detecting OCP to generating INT                                                    |       | 2     |       | ms    |

| VCONN Overcurrent Protection Wait Time Before Turn Off   | tOCP_VCON_N_OFF  | From generating INT to turning OFF VCONN switch                                         |       | 12    |       | ms    |

| VCONN Startup Time                                       | tVCONN_90        | Time from VCONN switch enable to CC settled at 90% of final value with $V_{BAT} = 4.2V$ |       | 12    | 35    | μs    |

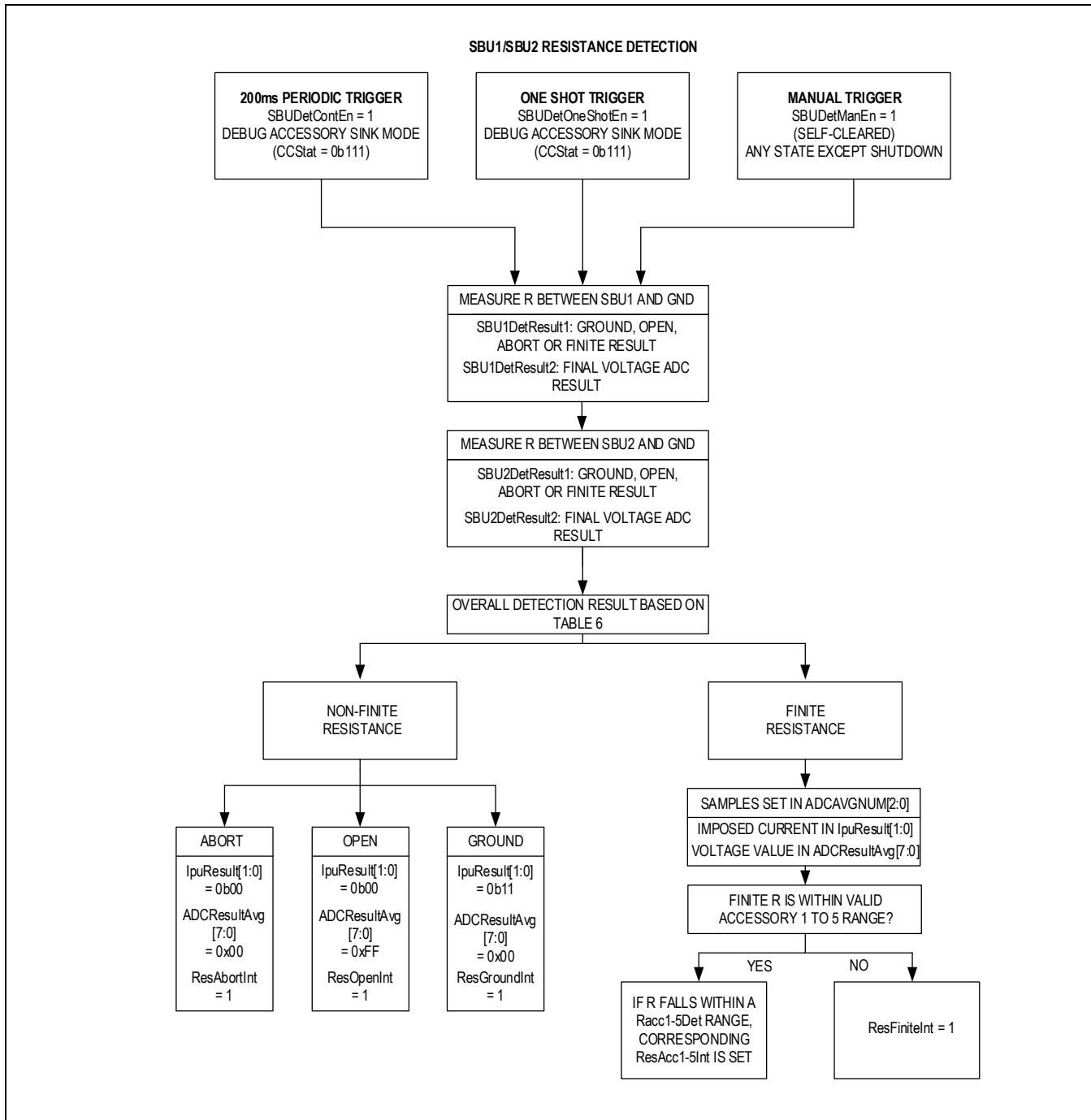

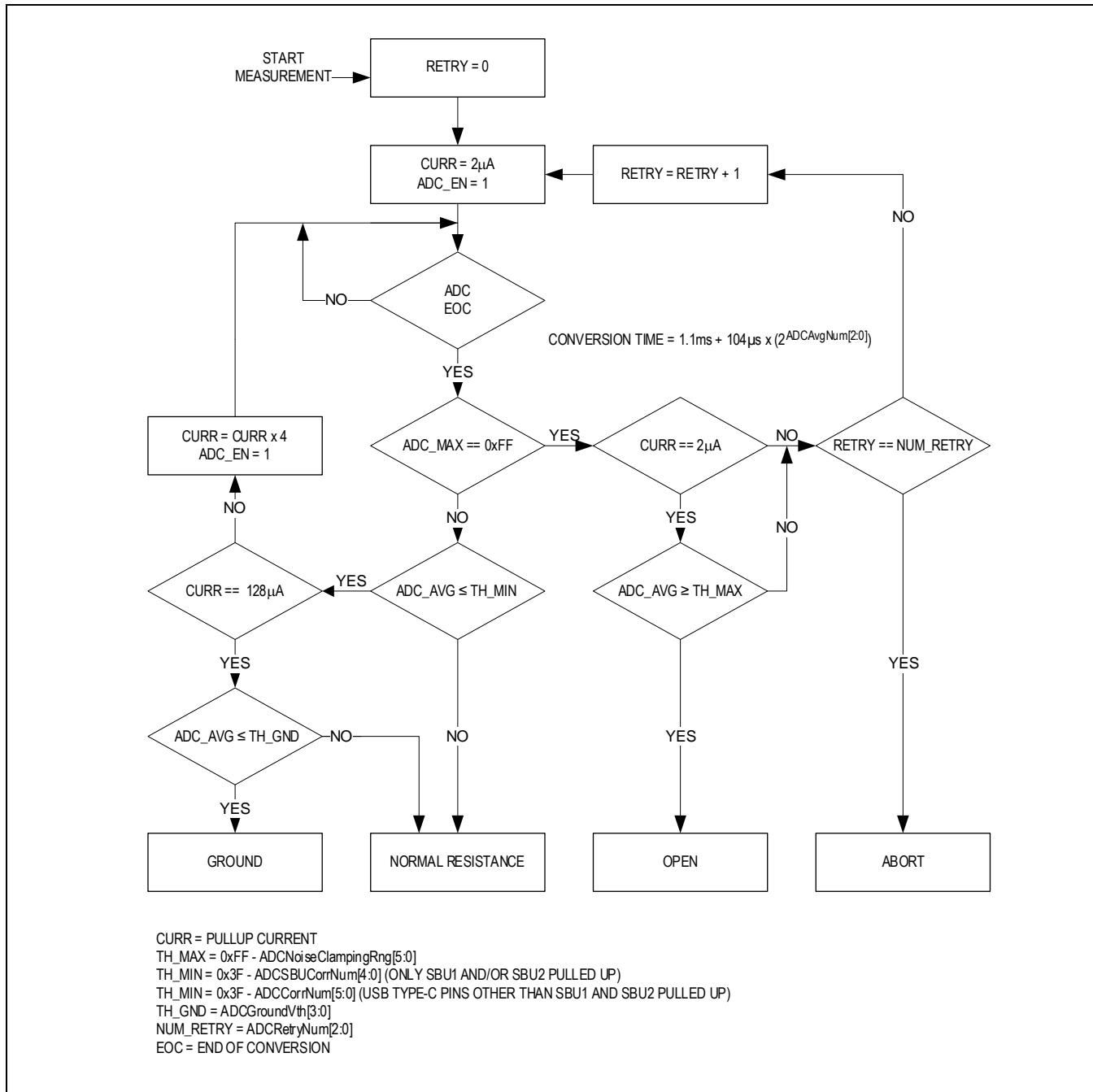

#### SBU RESISTOR AND MOISTURE DETECTION MEASUREMENT

|                                                           |                   |                                            |         |         |         |    |

|-----------------------------------------------------------|-------------------|--------------------------------------------|---------|---------|---------|----|

| SBU1/SBU2 Continuous Resistor Detection Quiescent Current | IQ_SBUDET         | 200ms period, ADCAvgNum[2:0] ≤ 3           | < 1.0   |         |         | μA |

| Periodic Moisture Detection Quiescent Current             | IQ_MOISTDET       | 10s period                                 | < 1.0   |         |         | μA |

| Pullup Current 1X                                         | IPU1X_RDE_T_SBU   | Pullup current on SBU1 or SBU2             | 1.952   | 2.000   | 2.048   | μA |

|                                                           | IPU1X_RDE_T_CCCD  | Pullup current on CC1 or CC2 or CDP or CDN | 1.840   | 2.000   | 2.160   |    |

| Pullup Current 4X                                         | IPU4X_RDE_T_SBU   | Pullup current on SBU1 or SBU2             | 7.809   | 8.000   | 8.191   | μA |

|                                                           | IPU4X_RDE_T_CCCD  | Pullup current on CC1 or CC2 or CDP or CDN | 7.720   | 8.000   | 8.280   |    |

| Pullup Current 16X                                        | IPU16X_RD ET_SBU  | Pullup current on SBU1 or SBU2             | 31.234  | 32.000  | 32.766  | μA |

|                                                           | IPU16X_RD ET_CCCD | Pullup current on CC1 or CC2 or CDP or CDN | 31.000  | 32.000  | 33.000  |    |

| Pullup Current 64X                                        | IPU64X_RD ET_SBU  | Pullup current on SBU1 or SBU2             | 124.941 | 128.000 | 131.059 | μA |

|                                                           | IPU64X_RD ET_CCCD | Pullup current on CC1 or CC2 or CDP or CDN | 124.400 | 128.000 | 131.600 |    |

| Pulldown Switches On Resistance                           | RMOIST_SWPD       | Enabled during moisture detection only     | 50      | 150     | 280     | Ω  |

| Pullup Forcing/Sensing                                    | RMOIST_SWPU       | (Note 2)                                   | 200     | 500     | 1050    | Ω  |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                       | SYMBOL         | CONDITIONS                                                                            | MIN   | TYP   | MAX    | UNITS                  |

|-------------------------------------------------|----------------|---------------------------------------------------------------------------------------|-------|-------|--------|------------------------|

| Switches On Resistance                          |                |                                                                                       |       |       |        |                        |

| SAR ADC Full Scale Voltage                      | VADC_FS        |                                                                                       | 1.485 | 1.500 | 1.515  | V                      |

| SAR ADC DAC Voltage Accuracy                    | VADC_DAC ACC   |                                                                                       | -0.3  |       | +0.3   | %                      |

| SAR ADC Comparator Static Error                 | VADC_COM PTH   |                                                                                       | -2.85 |       | +2.85  | mV                     |

| SAR ADC Comparator Maximum Dynamic Error        | VADC_COM P_DYN |                                                                                       |       | 1.5   |        | mV                     |

| SAR ADC Least Significant Bit                   | VADC LSB       | 8 bits                                                                                |       | 0.392 |        | %<br>V_ADC<br>_FS      |

| SAR ADC RC Antialiasing Filter Time Constant    | tADC_FILT      |                                                                                       |       | 90    |        | μs                     |

| SAR ADC Conversion Time                         | tADC_CONV      | 1.1ms (typ) additional delay prior to the first conversion                            |       | 104   |        | μs                     |

| ADC Worst Case Accuracy                         | VADC_ERR       | Voltage on pullup pin(s) = 0.375V                                                     | -1.47 |       | +1.47  | V_ADC<br>_LSB<br>(typ) |

|                                                 |                | Voltage on pullup pin(s) = 1.500V                                                     | -4.18 |       | +4.18  |                        |

|                                                 |                | Voltage on pullup pin(s) = 0.375V                                                     | -2.31 |       | +2.31  | %                      |

|                                                 |                | Voltage on pullup pin(s) = 1.500V                                                     | -1.64 |       | +1.64  |                        |

| Auto Detectable SBU1/SBU2 Resistance Range      | RSBU_RNG       | IPU1X_RDET_SBU pullup current applied on SBU1 or SBU2                                 | 187.5 |       | 714.7  | kΩ                     |

|                                                 |                | IPU4X_RDET_SBU pullup current applied on SBU1 or SBU2                                 | 46.88 |       | 170.2  |                        |

|                                                 |                | IPU16X_RDET_SBU pullup current applied on SBU1 or SBU2                                | 11.72 |       | 42.57  |                        |

|                                                 |                | IPU64X_RDET_SBU pullup current applied on SBU1 or SBU2                                | 2.93  |       | 10.64  |                        |

| SBU1/SBU2 Resistance Ground Condition Range     | RSBU_RNG_GND   | IPU64X_RDET_SBU pullup current applied on SBU1 or SBU2.<br>ADCGroundVth[3:0] = 0b0100 | 0     |       | 100.11 | Ω                      |

| Auto Detectable CC/CD Moisture Resistance Range | RCCCD_RNG      | IPU1X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN                    | 187.5 |       | 672.6  | kΩ                     |

|                                                 |                | IPU4X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN                    | 46.88 |       | 149.7  |                        |

( $V_{BAT} = 3.6V$ ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                 | SYMBOL          | CONDITIONS                                                                                                     | MIN    | TYP | MAX    | UNITS    |

|-------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------|--------|-----|--------|----------|

|                                           |                 | IPU16X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN                                            | 11.72  |     | 39.30  |          |

|                                           |                 | IPU64X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN                                            | 2.93   |     | 9.86   |          |

| CC/CD Resistance Ground Condition Range   | RCCCD_RN_G_GND  | IPU64X_RDET_CCCD pullup current applied on CDP and/or CDN. ADCGroundVth[3:0] = 0b0100                          | 0      |     | 99.70  | $\Omega$ |

| SBU1/SBU2 Resistance Measurement Accuracy | RSBU_ACC        | Within RSBU_RNG resistive range and under IPU1X_RDET_SBU pullup current applied on SBU1 or SBU2                | -4.70  |     | +4.70  | %        |

|                                           |                 | Within RSBU_RNG resistive range and under IPU4X_RDET_SBU pullup current applied on SBU1 or SBU2                | -4.70  |     | +4.70  |          |

|                                           |                 | Within RSBU_RNG resistive range and under IPU16X_RDET_SBU pullup current applied on SBU1 or SBU2               | -4.70  |     | +4.70  |          |

|                                           |                 | Within RSBU_RNG resistive range and under IPU64X_RDET_SBU pullup current applied on SBU1 or SBU2               | -4.70  |     | +4.70  |          |

| CC/CD Resistance Measurement Accuracy     | RCCCD_AC_C      | Within RCCCD_RNG resistive range and under IPU1X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN  | -10.31 |     | +10.31 | %        |

|                                           |                 | Within RCCCD_RNG resistive range and under IPU4X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN  | -5.81  |     | +5.81  |          |

|                                           |                 | Within RCCCD_RNG resistive range and under IPU16X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN | -5.44  |     | +5.44  |          |

|                                           |                 | Within RCCCD_RNG resistive range and under IPU64X_RDET_CCCD pullup current applied on CC1 or CC2 or CDP or CDN | -5.13  |     | +5.13  |          |

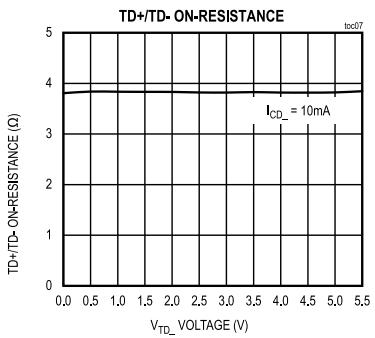

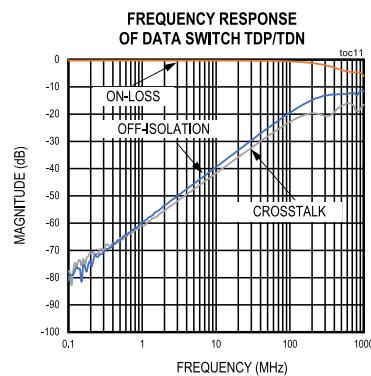

| <b>USB DATA SWITCHES (TDP/TDN)</b>        |                 |                                                                                                                |        |     |        |          |

| Analog Signal Range                       | VTDP/N          |                                                                                                                | 0      |     | 5.5    | $V$      |

| On-Resistance                             | RON_TD          |                                                                                                                | 3.7    |     | 6.0    | $\Omega$ |

| On-Resistance Match Between Channels      | $\Delta RON_TD$ | ITDP/N = 10mA, VTDP/N = 0.0V                                                                                   | 0.02   |     |        | $\Omega$ |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. )

| PARAMETER                              | SYMBOL         | CONDITIONS                                                                                    | MIN  | TYP   | MAX  | UNITS    |

|----------------------------------------|----------------|-----------------------------------------------------------------------------------------------|------|-------|------|----------|

| On-Resistance Flatness                 | RFLAT_TD       | ITDP/N = 10mA, VTDP/N = 0.0V to 5.5V                                                          |      | 0.005 |      | $\Omega$ |

| Off Leakage Current                    | IOFF_TD        | VCDP/N = 0V, VTDP/N = 2.5V                                                                    | -0.5 | 0.5   | +1.5 | $\mu A$  |

| On Leakage Current                     | ION_TD         | VTDP/N = 2.5V, VCDP/N = open                                                                  | -1   |       | +1.5 | $\mu A$  |

| Turn-On Time                           | tON_TD         | VTDP/N = 1.5V, RLOAD = 50 $\Omega$                                                            |      | 55    |      | $\mu s$  |

| Turn-Off Time                          | tOFF_TD        | VTDP/N = 1.5V, RLOAD = 50 $\Omega$                                                            |      | 20    |      | $\mu s$  |

| Output Skew Same Switch                | tSK(P)_TD      |                                                                                               |      | 40    |      | ps       |

| Output Skew Between Switch             | tSK(O)_TD      |                                                                                               |      | 40    |      | ps       |

| Break-Before-Make Time Delay           | tBBM_TD        | RLOAD = 50 $\Omega$ , delay between one side of the switch opening and the other side closing | 0    | 3     |      | $\mu s$  |

| -3dB Bandwidth                         | fBW_TD         | VD_ = 0dBm, RS = RL = 50 $\Omega$                                                             |      | 400   |      | MHz      |

| Off-Isolation                          | VISO_TD        | f = 20kHz, VD_ = 0.4Vp-p, RL = 50 $\Omega$                                                    |      | -80   |      | dB       |

| Crosstalk                              | VCRTLK_TD      | f = 20kHz, VD_ = 0.4Vp-p, RL = 50 $\Omega$                                                    |      | -80   |      | dB       |

| PSRR                                   | VPSRR_TD       | V = 400mVpp, f = 20kHz, RS = RL = 50 $\Omega$                                                 |      | -60   |      | dB       |

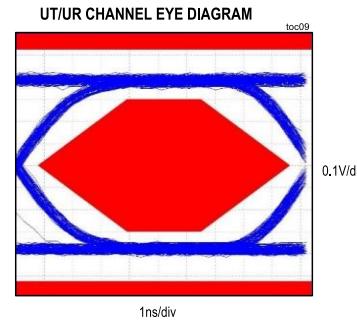

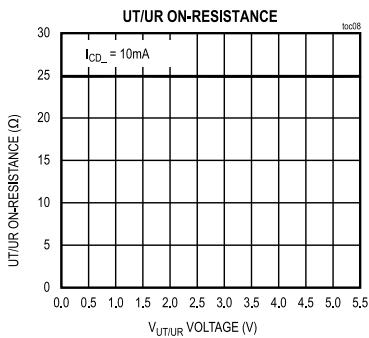

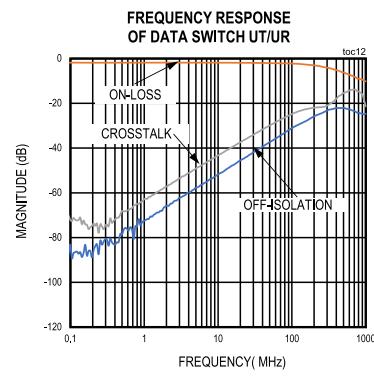

| <b>UART Switches (UR_UT)</b>           |                |                                                                                               |      |       |      |          |

| Analog Signal Range                    | VUR/T          |                                                                                               | 0    | 5.5   |      | V        |

| On-Resistance                          | RON_U          |                                                                                               | 23   | 36    |      | $\Omega$ |

| On-Resistance Match Between Channels   | $\Delta RON_U$ | IUR/T = 1mA, VUR/T = 0.0V                                                                     |      | 0.3   |      | $\Omega$ |

| On-Resistance Flatness                 | RFLAT_U        | IUR/T = 10mA, VUR/T = 0.0V to 5.5V                                                            |      | 0.01  |      | $\Omega$ |

| Off Leakage Current                    | IOFF_U         | VCDP/N = 0V, VUR/T = 2.5V                                                                     | -0.5 | 0.5   | +1.5 | $\mu A$  |

| On Leakage Current                     | ION_U          | VUR/T = 2.5V, VCDP/N = floating                                                               | -1   |       | +1.5 | $\mu A$  |

| Turn-On Time                           | tON_U          | VUR/T = 1.5V, RLOAD = 50 $\Omega$                                                             |      | 30    |      | $\mu s$  |

| Turn-Off Time                          | tOFF_U         | VUR/T = 1.5V, RLOAD = 50 $\Omega$                                                             |      | 15    |      | $\mu s$  |

| Break-Before-Make Time Delay           | tBBM_U         | RLOAD = 50 $\Omega$ , delay between one side of the switch opening and the other side closing | 0    | 38    |      | $\mu s$  |

| -3dB Bandwidth                         | fBW_U          | VD = 0dBm, RS = RL = 50 $\Omega$                                                              |      | 350   |      | MHz      |

| Off-Isolation                          | VISO_U         | f = 20kHz, VD = 0.4Vp-p, RL = 50 $\Omega$                                                     |      | -90   |      | dB       |

| Crosstalk                              | VCRTLK_U       | f = 20kHz, VD = 0.4Vp-p, RL = 50 $\Omega$                                                     |      | -70   |      | dB       |

| PSRR                                   | VPSRR_U        | V = 400mVpp, f = 20kHz, RS = RL = 50 $\Omega$                                                 |      | -60   |      | dB       |

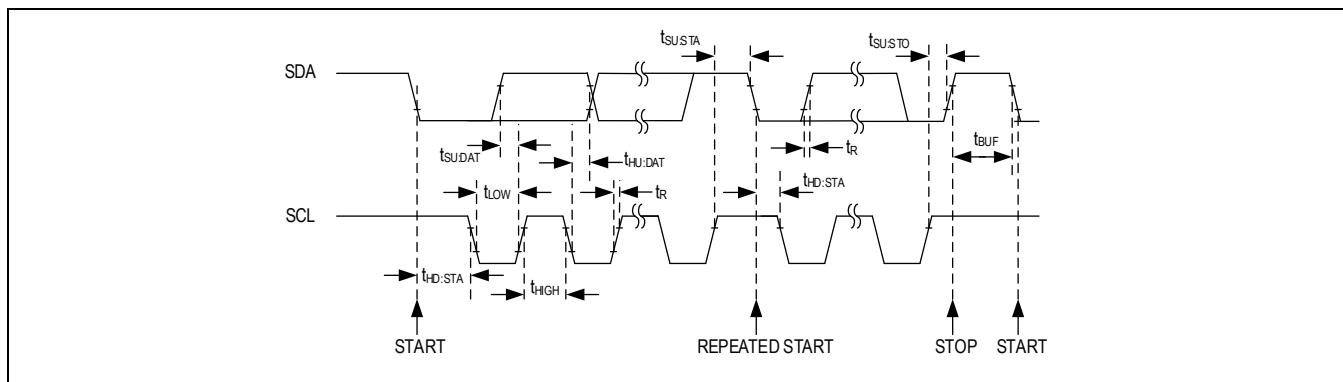

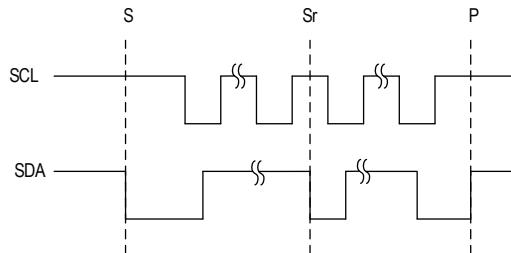

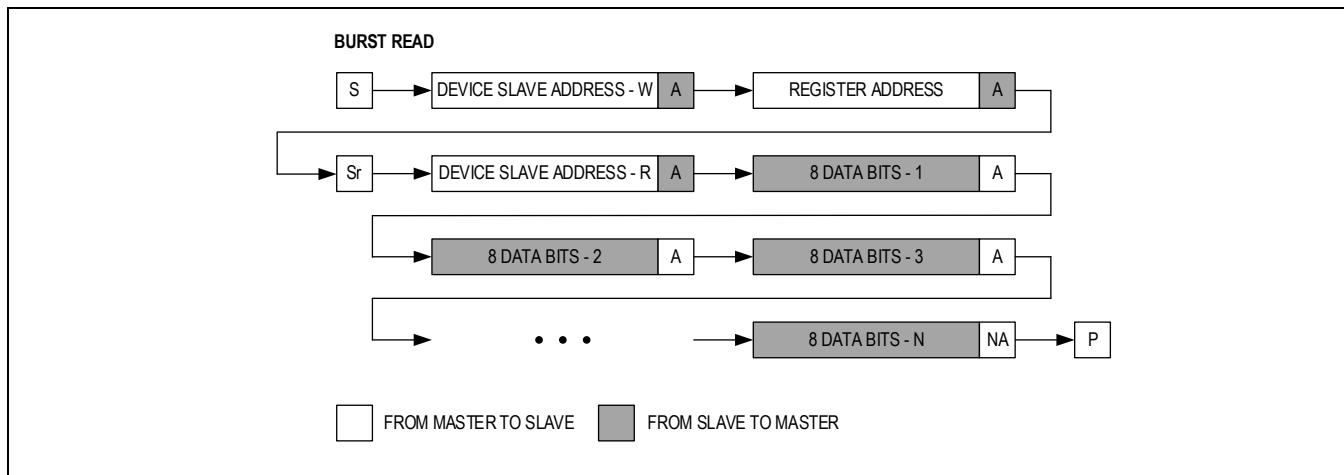

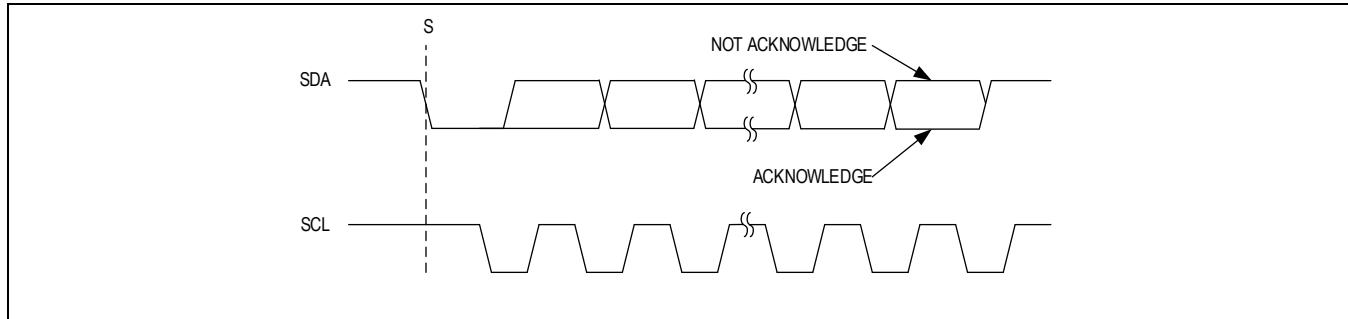

| <b>I<sup>2</sup>C INTERFACE TIMING</b> |                |                                                                                               |      |       |      |          |

| Clock Frequency                        | fSCL           |                                                                                               |      | 1000  |      | kHz      |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. )

| PARAMETER                                                         | SYMBOL  | CONDITIONS                                             | MIN  | TYP  | MAX | UNITS |

|-------------------------------------------------------------------|---------|--------------------------------------------------------|------|------|-----|-------|

| Hold Time<br>(Repeated) START Condition                           | tHD:STA |                                                        | 0.26 |      |     | μs    |

| CLK Low Period                                                    | tLOW    |                                                        | 0.5  |      |     | μs    |

| CLK High Period                                                   | tHIGH   |                                                        | 0.26 |      |     | μs    |

| Setup Time Repeated START Condition                               | tSU:STA |                                                        | 0.26 |      |     | μs    |

| DATA Hold Time                                                    | tHD:DAT |                                                        | 0    |      |     | μs    |

| DATA Valid Time                                                   | tVD:DAT |                                                        |      | 0.45 |     | μs    |

| DATA Valid Acknowledge Time                                       | tVD:ACK |                                                        |      | 0.45 |     | μs    |

| DATA Setup time                                                   | tSU:DAT |                                                        | 50   |      |     | ns    |

| Setup Time for STOP Condition                                     | tSU:STO |                                                        | 0.26 |      |     | μs    |

| Bus-Free Time Between STOP and START                              | tBUF    |                                                        | 0.5  |      |     | μs    |

| Pulse Width of Spikes that Must be Suppressed by the Input Filter | tsp     |                                                        |      | 50   |     | ns    |

| Input Logic High                                                  | VIN_IH  |                                                        | 1.5  |      |     | V     |

| Input Logic Low                                                   | VIN_IL  |                                                        |      | 0.3  |     | V     |

| Input Logic Leakage Current                                       | IIN_LKG |                                                        | -1   | +1   |     | μA    |

| OPEN DRAIN OUTPUTS (CE, DB, INT)                                  |         |                                                        |      |      |     |       |

| Open Drain Logic low                                              | VOD_OL  | IOD = 2mA                                              |      | 0.4  |     | V     |

| Open Drain Output High Leakage Current                            | IOD_LKG |                                                        | -1   | +1   |     | μA    |

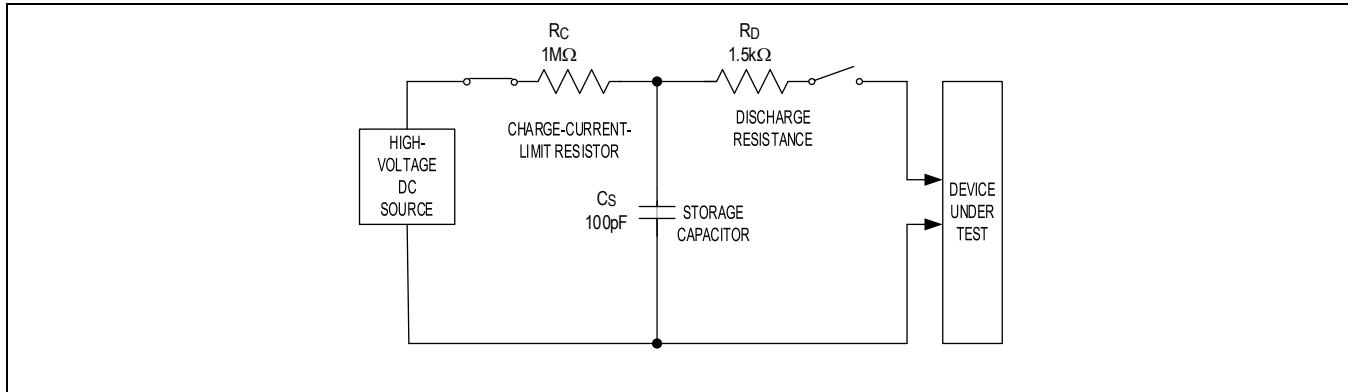

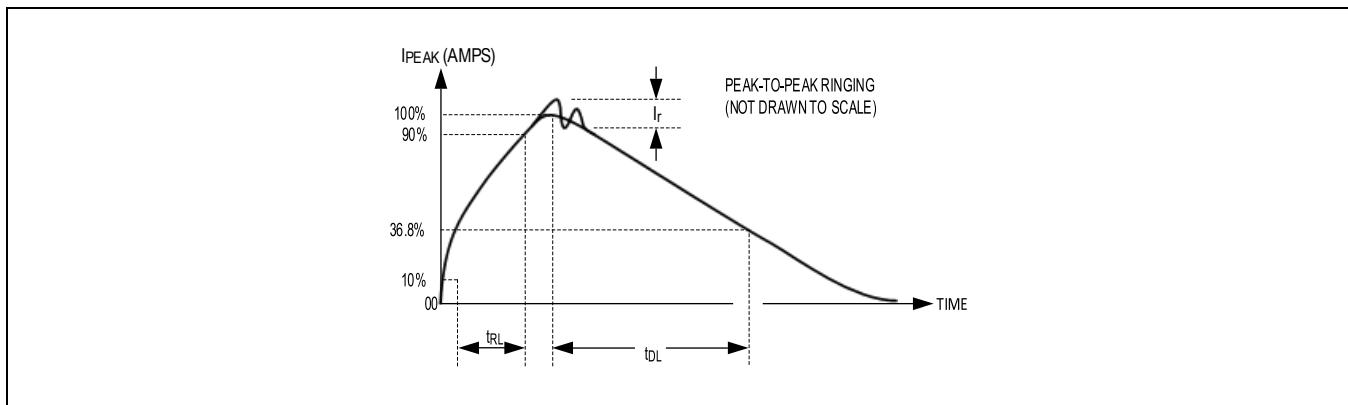

| ESD PROTECTION                                                    |         |                                                        |      |      |     |       |

| HBM                                                               |         | CDP/CDN                                                | ±6   |      |     | kV    |

|                                                                   |         | SBU1/SBU2, CC1/CC2, VB<br>(connected to 1μF capacitor) | ±15  |      |     |       |

| IEC61000-4-2 Contact Discharge                                    |         | SBU1/SBU2, CC1/CC2, VB<br>(connected to 1μF capacitor) | ±8   |      |     | kV    |

| IEC61000-4-2 Air Gap                                              |         | SBU1/SBU2, CC1/CC2, VB<br>(connected to 1μF capacitor) | ±15  |      |     | kV    |

| SURGE PROTECTION                                                  |         |                                                        |      |      |     |       |

| IEC61000-4-5 Surge                                                |         | VB                                                     | ±120 |      |     | V     |

( $V_{BAT} = 3.6V$  ,  $V_B = 5V$ ,  $C_{VDD} = 1\mu F$ ,  $C_{VB} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C_{BAT} = 1\mu F$ , limits are production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. )

| PARAMETER | SYMBOL | CONDITIONS         | MIN | TYP      | MAX | UNITS |

|-----------|--------|--------------------|-----|----------|-----|-------|

|           |        | CC1/CC2, SBU1/SBU2 |     | $\pm 45$ |     |       |

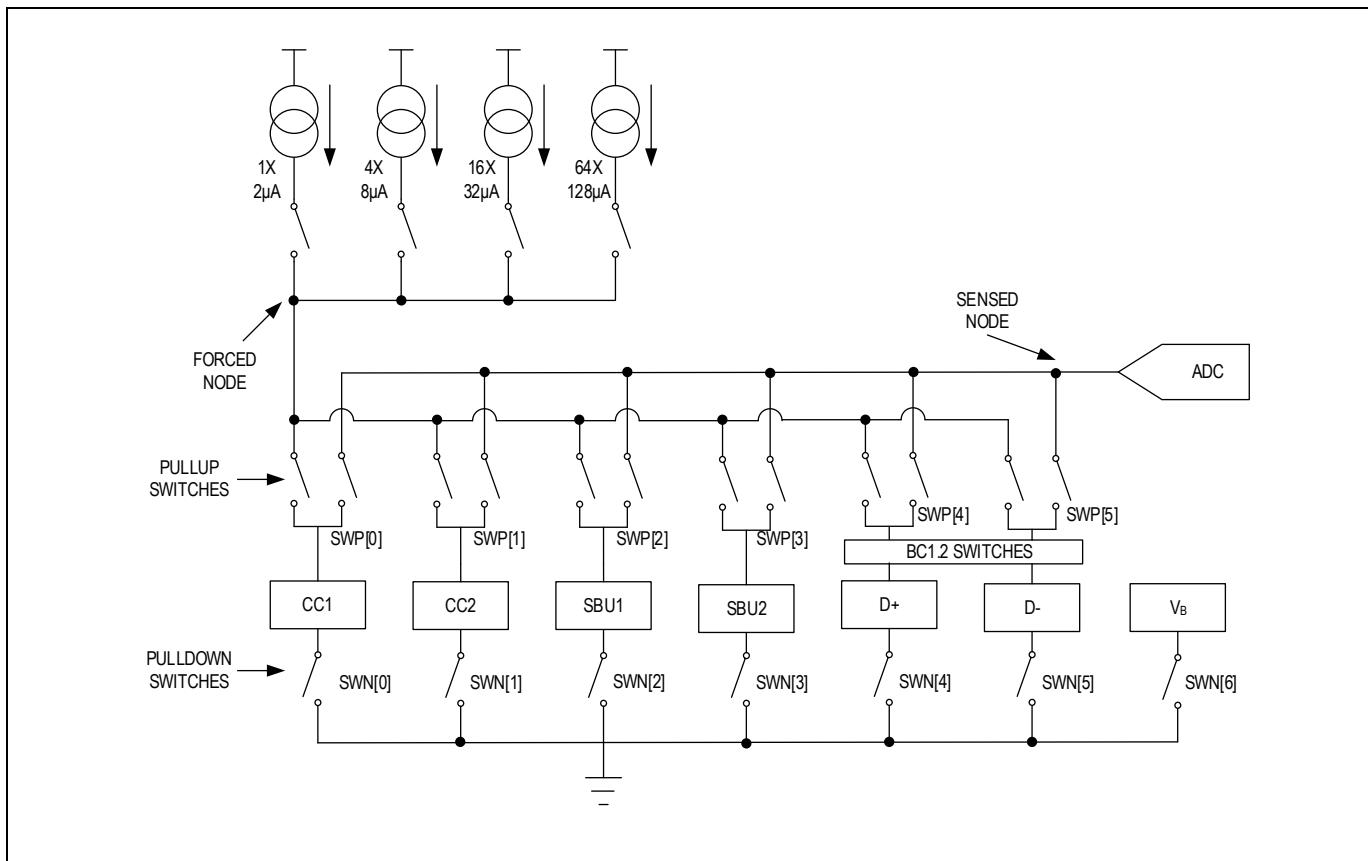

**Note 2:** During moisture detection in manual configuration, if more than one pin among SBU1, SBU2, CDP, CDN, CC1, and CC2 is pulled up at the same time, the pullup current is forced on a common internal node shared by the forcing switches, while the voltage measured by the ADC is that of another common internal node shared by the sensing switches. Both forcing and sensing switches have an  $R_{MOIST\_SWPU}$  resistance. For example, if just two pins are pulled up, an overall equivalent resistance equal to  $R_{MOIST\_SWPU}$  is applied between them. If the pullup pins are more than two, the resistive mesh internally applied between the pins is that shown in [Figure 7](#), where the SWP[n] switches are the forcing/sensing ones with  $R_{MOIST\_SWPU}$  resistance.

## Typical Operating Characteristics

(T<sub>A</sub> = +25°C, V<sub>B</sub> = 5V, unless otherwise noted.)

## MAX20342

## USB Type-C Charger Detector with Integrated OVP

( $T_A = +25^\circ\text{C}$ ,  $V_B = 5\text{V}$ , unless otherwise noted.)

## Bump Configuration

## Pin Descriptions

| PIN | NAME | FUNCTION                                                                                                                  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------|

| A1  | BAT  | Battery Connection Input. Bypass BAT to GND with a capacitor of 1 $\mu$ F effective capacitance.                          |

| A2  | GND  | Ground                                                                                                                    |

| A3  | OUT  | Overvoltage-Protected V <sub>B</sub> Power Output. Bypass OUT to GND with a capacitor of 1 $\mu$ F effective capacitance. |

| A4  | VB   | USB Type-C V <sub>BUS</sub> Connection. Bypass V <sub>B</sub> to GND with a capacitor of 1 $\mu$ F effective capacitance. |

| A5  | CDP  | USB Connector D+ Connection                                                                                               |

| A6  | CDN  | USB Connector D- Connection                                                                                               |

| B1  | VDD  | Internal Supply Input. Bypass V <sub>DD</sub> to GND with a capacitor of 1 $\mu$ F effective capacitance.                 |

| B2  | GND  | Ground                                                                                                                    |

| B3  | SBU2 | USB Type-C SBU2 Connection                                                                                                |

| B4  | SBU1 | USB Type-C SBU1 Connection                                                                                                |

| B5  | GND  | Ground                                                                                                                    |

| B6  | TDN  | USB Transceiver D- Connection                                                                                             |

| C1  | INT  | Active-Low, Open-Drain Interrupt Output. Connect INT to an external pullup resistor.                                      |

| C2  | CE   | Active-Low, Open-Drain Charger Control Enable Output. Connect CE to an external pullup resistor.                          |

| C3  | CC2  | USB Type-C CC2 Connection                                                                                                 |

| C4  | CC1  | USB Type-C CC1 Connection                                                                                                 |

|    |      |                                                                                                                                                                           |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5 | GND  | Ground                                                                                                                                                                    |

| C6 | TDP  | USB Transceiver D+ Connection                                                                                                                                             |

| D1 | DB   | Active-Low, Open-Drain Output. This pin is driven low when an 80k $\Omega$ resistor is connected to SBU1 or SBU2. Connect $\overline{DB}$ to an external pullup resistor. |

| D2 | SDA  | I <sup>2</sup> C Serial-Data Input/Output. Connect SDA to an external pullup resistor.                                                                                    |

| D3 | SCL  | I <sup>2</sup> C Serial-Clock Input. Connect SCL to an external pullup resistor.                                                                                          |

| D4 | DGND | Digital Ground                                                                                                                                                            |

| D5 | UT   | UART Tx Device Connection                                                                                                                                                 |

| D6 | UR   | UART Rx Device Connection                                                                                                                                                 |

## Functional Diagram

## Detailed Description

### USB BC1.2 Charger Detection

The MAX20342 USB charger detection block supports USB BC1.2 with the additional capability to automatically detect some common proprietary charger types. Note that after the secondary detection of USB BC1.2 finishes, the device does not keep  $V_{DP\_SRC}$  enabled if DCP is detected. While this behavior can cause the device to fail the DCP test in USB BC1.2 compliance, this is not expected to cause any issue in the detection of BC1.2 chargers.

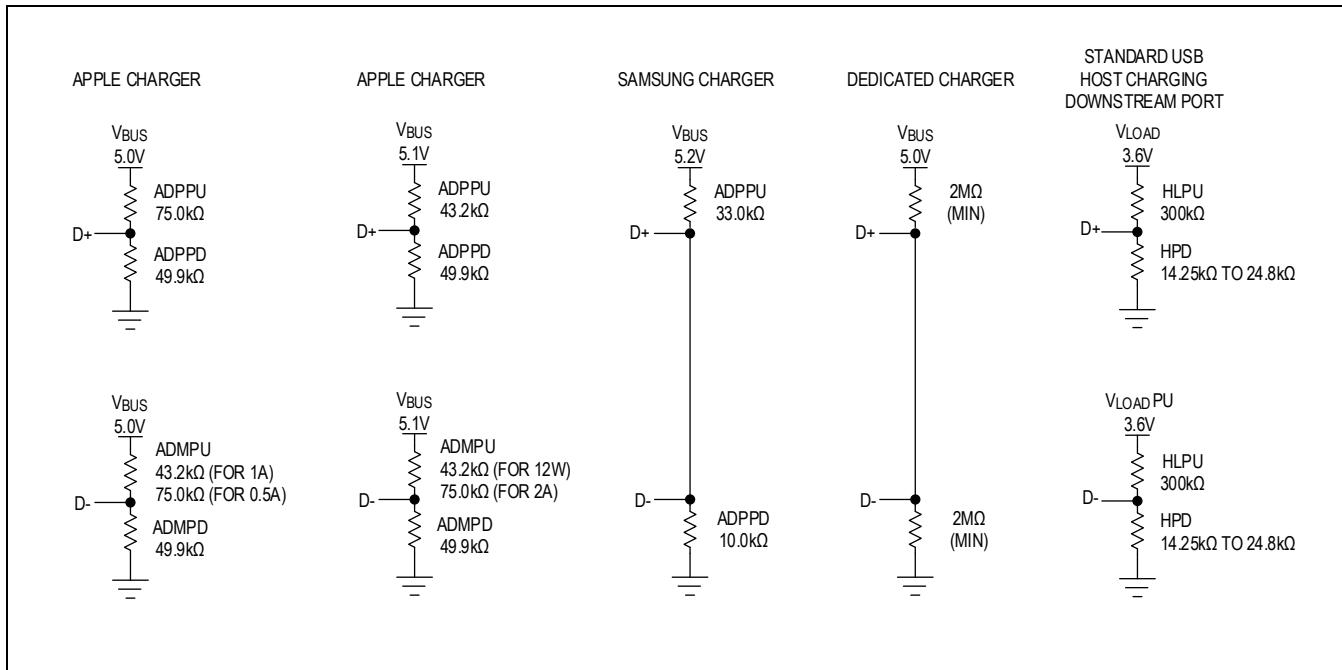

The Charger Detection State Machine follows USB BC1.2 requirements and detects SDP, CDP, and DCP charger types (see [Table 1](#)) In addition to the USB BC1.2 State Machine, the MAX20342 also detects a limited number of proprietary charger types (Apple, Samsung, and generic 500mA). The MAX20342 always reports SDP/CDP/DCP in addition to a detected proprietary type. For example, the Samsung proprietary charger uses D+/D- short and bias on D+/D-. The bias voltage is chosen so that, with a USB BC1.2 compliant state machine, it is detected as a DCP. The device reports this charger detected as both a DCP and a Samsung charger. See [Table 2](#) and [Table 3](#) for more details.

The MAX20342 also reports the operation status of the Charger Detection State Machine in the ChgTypRun interrupt bit in the register map.

**Table 1. USB BC1.2 Charger Type Detection**

| CHGTYP[1:0] | CHARGER DETECTED |

|-------------|------------------|

| 0b00        | No CHGIN         |

| 0b01        | SDP              |

| 0b10        | CDP              |

| 0b11        | DCP              |

**Note:** Charge Detect running state is indicated until the Charger Detection State Machine is complete.

**Table 2. Proprietary Detection Table**

|    |                    | D+         |                    |                  |                  |                   |

|----|--------------------|------------|--------------------|------------------|------------------|-------------------|

|    |                    | 0 TO 0.32V | 0.32V TO 31% OF VB | 31% TO 47% OF VB | 47% TO 64% OF VB | 64% TO 100% OF VB |

| D- | 0 TO 0.32V         | Unknown    | Unknown            | Unknown          | Unknown          | Unknown           |

|    | 0.32V TO 31% OF VB | Unknown    | Samsung            | Unknown          | Unknown          | Unknown           |

|    | 31% TO 47% OF VB   | Unknown    | Unknown            | Apple 0.5A       | Apple 2.0A       | Unknown           |

|    | 47% TO 64% OF VB   | Unknown    | Unknown            | Apple 1.0A       | Apple 12W        | Unknown           |

|    | 64% TO 100% OF VB  | Unknown    | Unknown            | Unknown          | Unknown          | Unknown           |

Examples of ChgTyp[1:0] and PrChgTyp[2:0] values found for common chargers on the market are listed in [Table 3](#). When the MAX20342 detects the charger, it sets the  $\overline{CE}$  output based on the charger type found. [Table 4](#) shows D+/D-termination for Apple chargers, Samsung charger, dedicated charger, and a standard USB host charging downstream port.

**Table 3. Charger Control Table**

| ADAPTER TYPE      | CHGTYP[1:0] | PRCHGTYP[2:0]   | CE OUTPUT        |                  |

|-------------------|-------------|-----------------|------------------|------------------|

|                   |             |                 | NOTUSBCMPL = 0b0 | NOTUSBCMPL = 0b1 |

| Nothing connected |             |                 | High             | High             |

| DCP               | 0x03 DCP    | 0x00 unknown    | Low              | Low              |

| SDP               | 0x01 SDP    | 0x00 unknown    | High             | Low              |

| CDP               | 0x02 CDP    | 0x00 unknown    | Low              | Low              |

| Samsung 2A DCP    | 0x03 DCP    | 0x01 Samsung 2A | Low              | Low              |

| Apple 500mA       | 0x01 SDP    | 0x02 Apple 0.5A | Low              | Low              |

| Apple 1A          | 0x02 CDP    | 0x03 Apple 1A   | Low              | Low              |

| Apple 2A          | 0x01 SDP    | 0x04 Apple 2A   | Low              | Low              |

| Apple 12W         | 0x03 DCP    | 0x05 Apple 12W  | Low              | Low              |

Figure 1. Apple Chargers, Samsung Charger, Dedicated Charger, and Standard USB Host Charging Downstream Port

### Autoconfiguration Mode

The MAX20342 is capable of automatically setting the position of the internal analog switches, and  $\overline{CE}$  and  $\overline{DB}$  outputs based on the state of  $V_B$  voltage, CC resistor value, and SBU resistor value. See [Table 4](#) for more details.

The autoconfiguration state machine starts when either the device is in Debug Accessory Sink Mode and FactAuto = 1, or the device is connected to the valid  $V_B$  voltage and USBAuto = 1. If FactAuto = 0 and USBAuto = 0, the autoconfiguration cannot start.

**Table 4. Autoconfiguration Mode Table**

| MAX20342 DEVICE CONFIGURATION BASED ON VB, CC PINS, AND SBU PINS |                  |                           |                                    |                                 |                                 |                                                                   |                                                                   |                                                                   |                                 |                                                                                                                                                                                                           |

|------------------------------------------------------------------|------------------|---------------------------|------------------------------------|---------------------------------|---------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                  | RESET            | INVALID                   | UART                               | USB/<br>FACTORY                 | UART/<br>FACTORY                | USB<br>CHARGER<br>(OTHER<br>THAN<br>SDP<br>FOUND)                 | USB<br>HOST<br>(SDP<br>FOUND)                                     | USB<br>DEVICE<br>(SOURCE<br>MODE,<br>DRP<br>ONLY)                 | ANALOG<br>AUDIO<br>ACCESSORY    | V <sub>CONN</sub><br>POWERED<br>DEVICE<br>(E.G.,<br>DIGITAL<br>HEADSET)                                                                                                                                   |

| FACTAUTO/<br>USBAUTO                                             | -                | -                         | FactAuto<br>= 1                    | FactAuto<br>= 1                 | FactAuto<br>= 1                 | USBAuto<br>= 1                                                    | USBAuto<br>= 1                                                    | USBAuto<br>= 1                                                    | USBAuto<br>= 1                  | USBAuto<br>= 1                                                                                                                                                                                            |

| V <sub>B</sub>                                                   | Not<br>connected | Outside<br>valid<br>range | Valid                              | Valid                           | Valid                           | Valid                                                             | Valid                                                             | -                                                                 | Not<br>Connected                | Not<br>Connected                                                                                                                                                                                          |

| CC PINS                                                          | -                | -                         | CC1 and<br>CC2 =<br>R <sub>p</sub> | CC1 and<br>CC2 = R <sub>p</sub> | CC1 and<br>CC2 = R <sub>p</sub> | Only CC1<br>= R <sub>p</sub> , or<br>only CC2 =<br>R <sub>p</sub> | Only CC1<br>= R <sub>d</sub> , or<br>only CC2<br>= R <sub>d</sub> | Only CC1<br>= R <sub>d</sub> , or<br>only CC2<br>= R <sub>d</sub> | CC1 and CC2<br>= R <sub>a</sub> | CC1 = R <sub>d</sub><br>and CC2 =<br>R <sub>a</sub> , or CC1<br>= R <sub>a</sub> and<br>CC2 = R <sub>d</sub><br>Connect<br>BAT<br>(V <sub>CONN</sub> ) to<br>CC_ with<br>R <sub>a</sub> through<br>switch |

| SBU PINS                                                         | -                | -                         | SBU1 or<br>SBU2 =<br>30kΩ          | SBU1 or<br>SBU2 =<br>80.2kΩ     | SBU1 or<br>SBU2 =<br>150kΩ      | -                                                                 | -                                                                 | -                                                                 | -                               | -                                                                                                                                                                                                         |

| OUT                                                              | High-Z           | High-Z                    | High-Z                             | V <sub>B</sub>                  | V <sub>B</sub>                  | V <sub>B</sub>                                                    | V <sub>B</sub>                                                    | OVP<br>switch<br>requires<br>manual<br>setting<br>(**)            | High-Z                          | High-Z                                                                                                                                                                                                    |

| CDP/CDN<br>SWITCH<br>POSITION                                    | -                | -                         | UR/UT                              | TDP/TDN                         | UR/UT                           | OPEN                                                              | TDP/TDN                                                           | TDP/TDN                                                           | OPEN                            | TDP/TDN                                                                                                                                                                                                   |

| CE                                                               | High-Z           | High-Z                    | High-Z                             | GND                             | GND                             | GND                                                               | High-Z or<br>GND (*)                                              | High-Z                                                            | High-Z                          | High-Z                                                                                                                                                                                                    |

| DB                                                               | High-Z           | High-Z                    | High-Z                             | GND                             | High-Z                          | High-Z                                                            | High-Z                                                            | High-Z                                                            | High-Z                          | High-Z                                                                                                                                                                                                    |

| INT                                                              | High-Z           | GND                       | GND                                | High-Z                          | High-Z                          | High-Z                                                            | High-Z                                                            | High-Z                                                            | High-Z                          | High-Z                                                                                                                                                                                                    |

(\*) CE setting depends on NotUSBCmpl bit.

(\*\*) If a USB device is detected, the OVP switch must be manually set as described in the [OVP Manual Setting](#) section.

### OVP Manual Setting

In the case where a USB device is detected and the MAX20342 needs to source power from OUT to  $V_B$ , and then to the USB Type-C receptacle, the OVP switch needs to be manually set. When the MAX20342 has detected through the USB Type-C that a USB device has been attached, the user must follow the procedure to source power from OUT to  $V_B$ .

1. Manually close the OVP switch setting (VBOVPEn = 0x3). At this point, no power source must be attached to OUT.

2. Wait for SwtClosedInt interrupt request. At this point the OVP switch is closed and power can be attached to OUT.

3. Enable power source on OUT.

The user must follow the procedure to stop power sourcing to  $V_B$ .

1. Disable power source on OUT.

2. Manually open the OVP switch setting (VBOVPEn = 0x0). Wait for SwtClosedInt interrupt request. At this point the OVP switch is actually open.

The power source on OUT must not exceed 2A and 5.5V to avoid triggering the OVLO threshold. This restriction avoids a voltage drop between OUT and  $V_B$  ( $OUT - V_B = R_{ON} \times I_{MAX}$ ) that is greater than the diode forward voltage (0.3V), which prevents current flow through the diode.

### USB Type-C Detection

The MAX20342 is a complete solution for USB Type-C port charger detection and multiplexing USB and UART on a single USB Type-C connector.