## DATASHEET

# Apollo4 Blue Lite SoC

Ultra-low Power Apollo SoC Family

Doc. ID: DS-A4BL-0p9p0

Doc. Revision: 0.9.0, July 2023

### IMPORTANT NOTICE:

This datasheet includes content which is accurate to the extent possible, but is preliminary and certain content may not be fully validated. Please contact [Sales@Ambiq.com](mailto:Sales@Ambiq.com) for more information.

## Features

### Ultra-low supply current:

- 4.6  $\mu$ A/MHz executing “while” from NVM with cache at 3.3V

- Low-power sleep and deep sleep modes with selectable levels of RAM/cache retention

### High-performance Arm Cortex-M4 Processor with FPU:

- 96/192 MHz operating mode

- Floating Point Unit, Memory Protection Unit

- Secure boot

### Bluetooth Low Energy 5.1<sup>1</sup>:

- Data rate: 1 Mbps and 2 Mbps

- Extended advertising packets

- Angle of Arrival (AoA) and Angle of Departure (AoD)

- Tx output power: -10 dBm to +6 dBm

- Rx sensitivity: -95.5 dBm at 1 Mbps, -92 dBm at 2 Mbps

### Ultra-low-power memory:

- Up to 2 MB of non-volatile memory (NVM) for code/data

- Up to 1.375 MB of low power RAM for code/data

### Ultra-low-power interface for off-chip sensors:

- 8-bit, 10-bit and 12-bit ADC modes, 11 selectable channels

- Temperature sensor with  $\pm 3^\circ$ C accuracy

### Ultra-low-power flexible serial peripherals:

- 2x QSPI/OSPI; 1x QSPI/OSPI/HexSPI

- 7x I<sup>2</sup>C / SPI masters for peripheral communication

- I<sup>2</sup>C/SPI slave for host communications

- 4x UART modules with flow control

- SDIO (SD3.0) / eMMC (v4.51)

### Display:

- Up to 390x390x24-bit resolution at 30 FPS (using NemaGUI over MSPI interface)

### Graphics:

- 2D/2.5D graphics accelerator

- Texture mapping

- Anti-aliasing / dithering / vector graphics processing

### Audio Processing:

- 1x PDM Interface

- 1x full duplex I<sup>2</sup>S port

### Rich set of clock sources:

- 32 MHz and 32.768 kHz crystal oscillators

- 900 Hz low-frequency RC oscillator

- 2x high-frequency RC oscillators - 192/384 MHz

### Power Management:

- Operating Voltage: 1.71 - 2.2 V

- Temp Range: -20°C to 60°C

- SIMO buck / BLE buck

- Multiple I/O voltages supported

## Applications

- Smart watches/bands

- Consumer electronics

- Home automation

- Consumer medical devices

- Activity and fitness monitors

- Motion and tracking devices

- Alarms and security system

## Package

- 4.7 mm x 4.7 mm, 12 x 12 BGA (131 pins / 75 GPIO)

## Description

The Apollo4 Blue Lite family derivatives are the latest addition to the ever-growing Apollo4 product family. The Lite members are cost-reduced variations based on the Apollo4 and Apollo4 Plus SoCs, and are targeted for mid-range and mid-low range consumer wearables as host processor as well as higher end wearables as a sensor HUB. The design benefits for Apollo4 Lite are low die cost and deep sleep power (needed to support sensor HUB applications and expansion into adjacent market opportunities). With 2 MB of NVM and 1.375 MB of SRAM, the Apollo4 Lite and Blue Lite have more than enough compute and storage to handle complex algorithms and neural networks while displaying vibrant, crystal clear, and smooth graphics. The Apollo4 Lite is packaged standalone while the Apollo4 Blue Lite has a System-in-Package (SiP) configuration with the BLE 5.1 controller module used in other “Blue” variants of the Apollo4 family.

1. The *Bluetooth*<sup>®</sup> word mark and logos are registered trademarks owned by the Bluetooth SIG, Inc. and any use of such marks is under license. Other trademarks and trade names are those of their respective owners.

## Table of Contents

|                                                    |           |

|----------------------------------------------------|-----------|

| <b>1. Apollo4 Blue Lite SoC Package Pins .....</b> | <b>10</b> |

| 1.1 Pin Configuration .....                        | 10        |

| 1.2 Pin Connections .....                          | 11        |

| <b>2. SoC Product Introduction .....</b>           | <b>38</b> |

| 2.1 Features .....                                 | 39        |

| 2.2 Functional Overview .....                      | 41        |

| <b>3. MCU Core .....</b>                           | <b>43</b> |

| 3.1 Functional Overview .....                      | 43        |

| 3.2 CPU Subsystem .....                            | 45        |

| 3.3 Interrupts .....                               | 46        |

| 3.4 Memory Map .....                               | 47        |

| 3.5 Memory Protection Unit (MPU) .....             | 48        |

| 3.6 System Buses .....                             | 49        |

| 3.7 Power Management .....                         | 50        |

| 3.7.1 Cortex-M4 Power Modes - Overview .....       | 50        |

| 3.7.2 CPU Power Management .....                   | 51        |

| 3.8 Debug Interfaces .....                         | 55        |

| 3.8.1 Embedded Trace Macrocell (ETM) .....         | 55        |

| 3.8.2 Instrumentation Trace Macrocell (ITM) .....  | 55        |

| 3.8.3 Trace Port Interface Unit (TPIU) .....       | 55        |

| 3.8.4 Faulting Address Trapping Hardware .....     | 55        |

| <b>4. Memory Subsystem .....</b>                   | <b>56</b> |

| 4.1 Functional Overview .....                      | 57        |

| 4.2 Memory Controller .....                        | 58        |

| 4.2.1 DAXI .....                                   | 60        |

| 4.2.2 NVM Cache .....                              | 65        |

| 4.3 Wait States for Accesses to Memory Types ..... | 67        |

| 4.4 One-Time Programmable (OTP) Memory .....       | 70        |

| <b>5. Reset Generator (RSTGEN) .....</b>           | <b>71</b> |

| 5.1 Functional Overview .....                      | 71        |

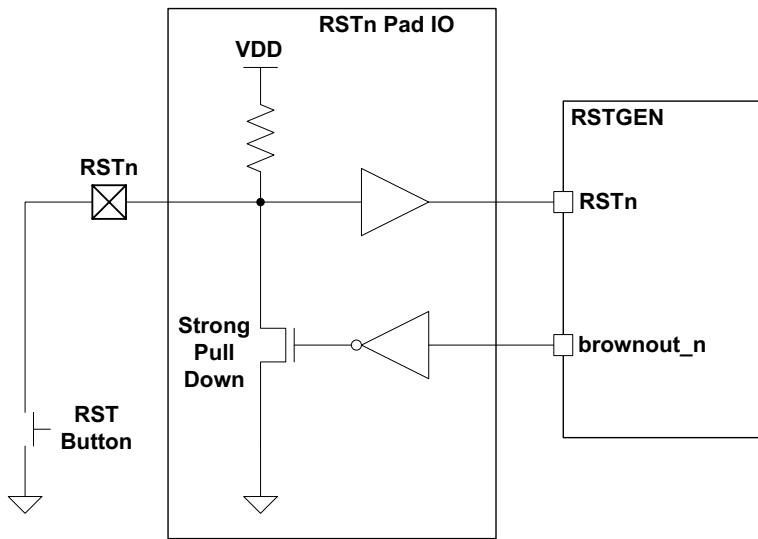

| 5.2 External Reset Pin .....                       | 71        |

| 5.3 Power-on Event .....                           | 72        |

| 5.4 Brown-out Events .....                         | 72        |

| 5.5 Software Reset .....                           | 73        |

| 5.6 Watchdog Reset .....                           | 73        |

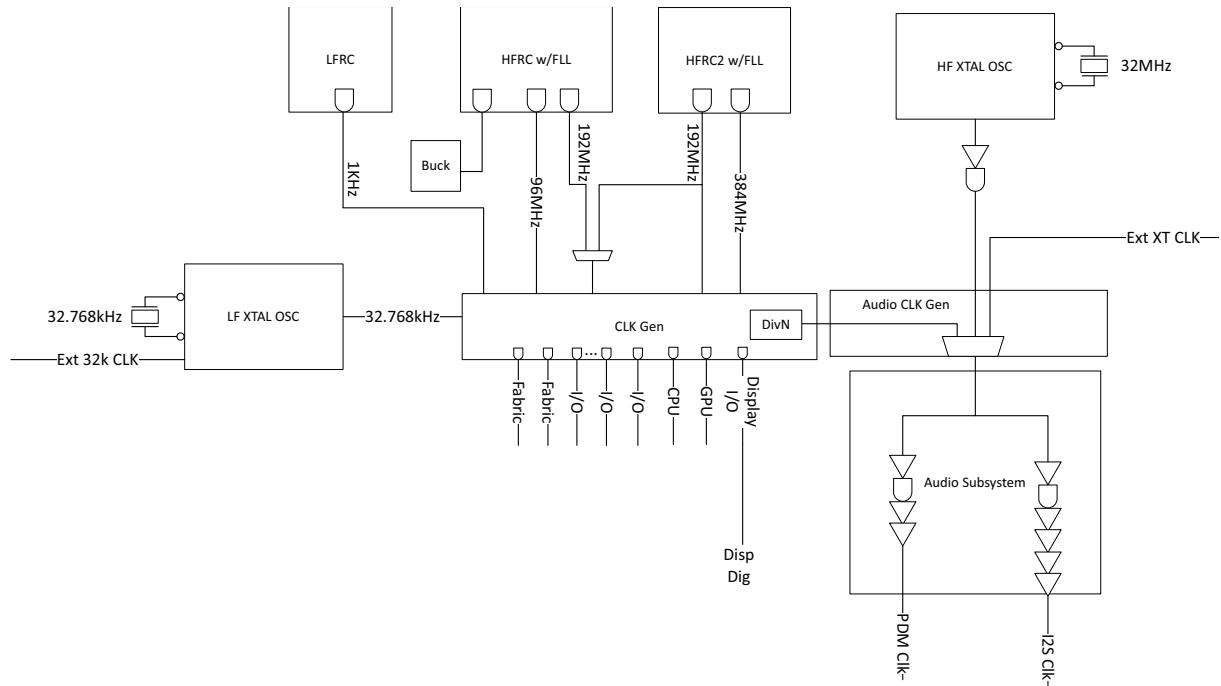

| <b>6. Clock Generator (CLKGEN) .....</b>           | <b>74</b> |

| 6.1 Features .....                                 | 74        |

| 6.2 Functional Overview .....                      | 75        |

| 6.3 Low Frequency RC Oscillator (LFRC) .....       | 76        |

| 6.4 High Precision XT Oscillator (XT) .....        | 76        |

| 6.5 High Frequency RC Oscillator (HFRC) .....      | 76        |

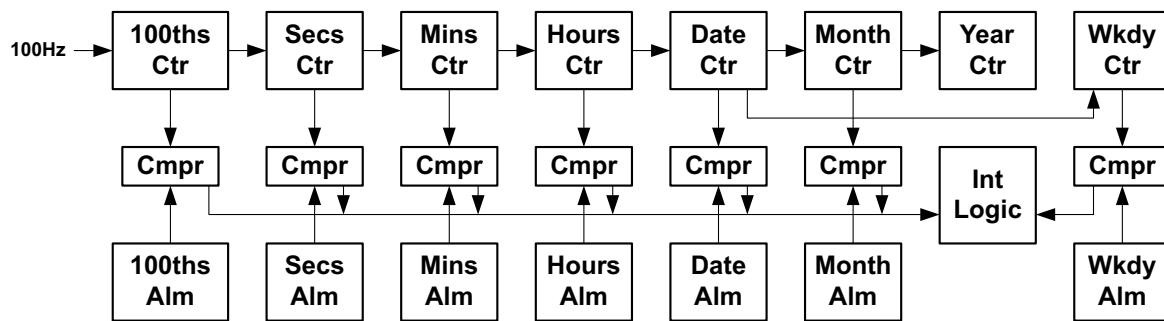

| <b>7. Real Time Clock (RTC) .....</b>              | <b>78</b> |

| 7.1 Functional Overview .....                      | 78        |

| 7.2 Additional Information .....                   | 78        |

| <b>8. Security .....</b>                           | <b>79</b> |

| 8.1 Functional Overview .....                      | 79        |

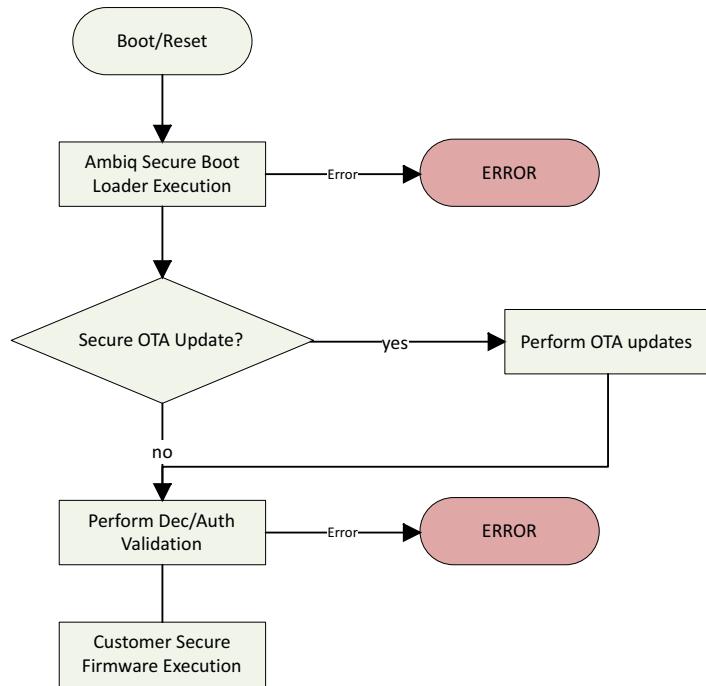

| 8.2 Secure Boot .....                              | 80        |

| 8.3 Secure OTA .....                               | 81        |

|                                                                    |            |

|--------------------------------------------------------------------|------------|

| 8.4 Secure Key Storage .....                                       | 81         |

| 8.5 External Flash In-line Encrypt/Decrypt .....                   | 82         |

| 8.6 Secure Life Cycle States .....                                 | 82         |

| 8.7 Crypto Subsystem .....                                         | 83         |

| <b>9. Bluetooth Low Energy Controller .....</b>                    | <b>84</b>  |

| 9.1 Feature Set .....                                              | 84         |

| 9.2 Functional Overview .....                                      | 85         |

| 9.3 Clocking .....                                                 | 85         |

| 9.4 Power Management .....                                         | 85         |

| 9.5 Hardware Reference .....                                       | 85         |

| 9.5.1 Power Delivery .....                                         | 85         |

| 9.6 Antenna .....                                                  | 86         |

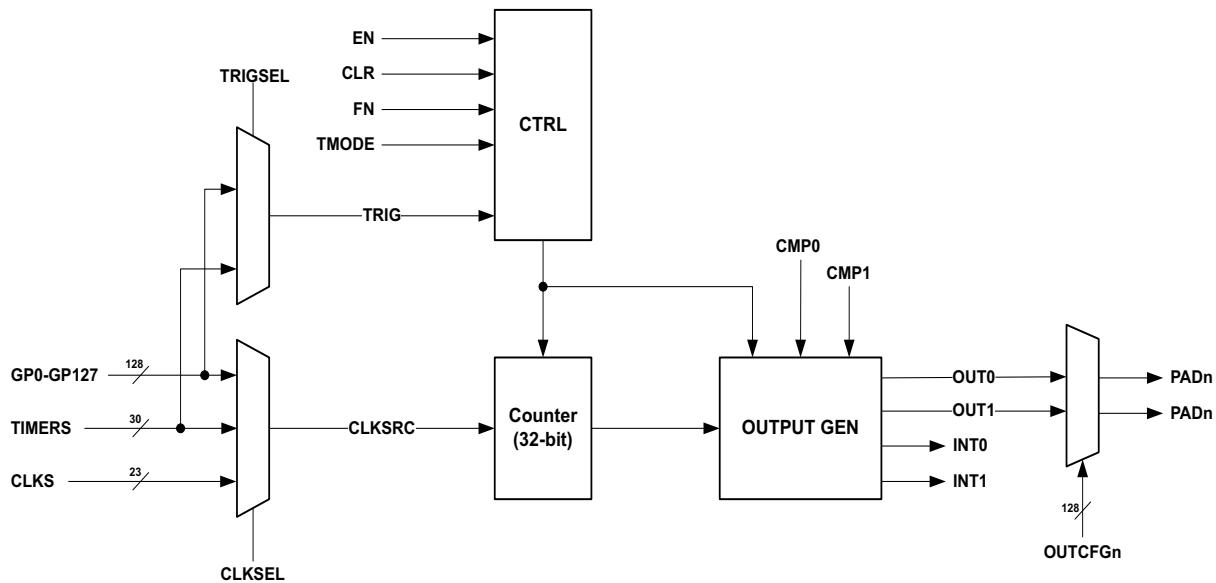

| <b>10. Counter/Timer Module (TIMER) .....</b>                      | <b>87</b>  |

| 10.1 Functional Overview .....                                     | 87         |

| 10.2 Additional Information .....                                  | 88         |

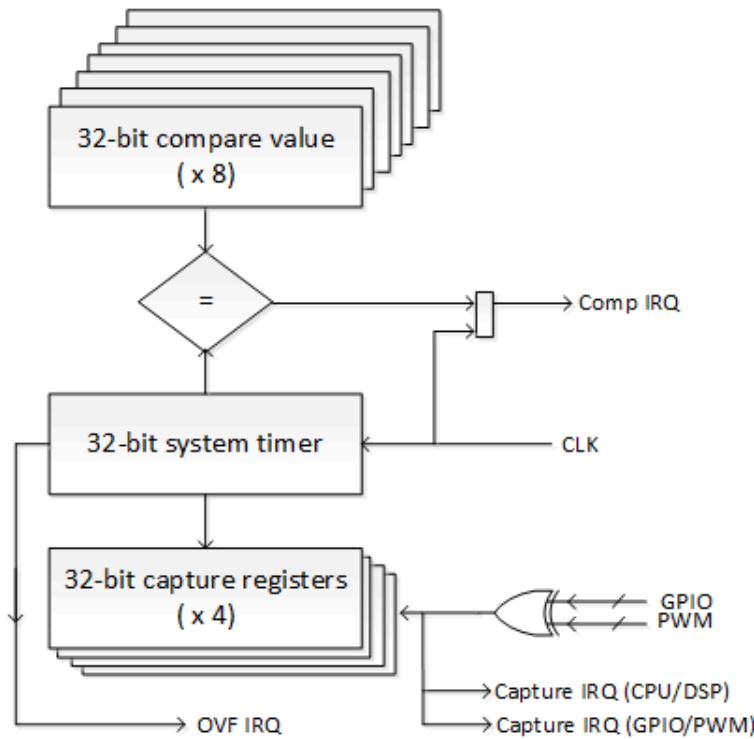

| <b>11. System Timer (STIMER) .....</b>                             | <b>89</b>  |

| 11.1 Functional Overview .....                                     | 89         |

| 11.2 Additional Information .....                                  | 90         |

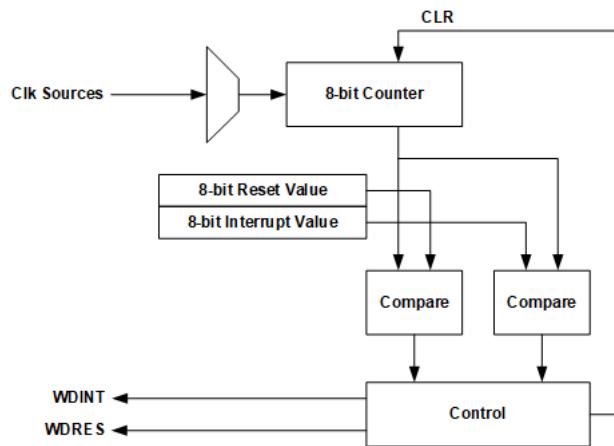

| <b>12. Watchdog Timer (WDT) .....</b>                              | <b>91</b>  |

| 12.1 Functional Overview .....                                     | 91         |

| 12.2 Additional Information .....                                  | 91         |

| <b>13. General Purpose Input/Output (GPIO) .....</b>               | <b>92</b>  |

| 13.1 Functional Overview .....                                     | 92         |

| 13.2 Pad Configuration Functions .....                             | 93         |

| 13.3 Fast GPIO (FPIO) .....                                        | 97         |

| 13.4 Additional Information .....                                  | 97         |

| <b>14. General Purpose ADC and Temperature Sensor Module .....</b> | <b>98</b>  |

| 14.1 Features .....                                                | 98         |

| 14.2 Functional Overview .....                                     | 99         |

| 14.3 Voltage Reference Source .....                                | 99         |

| 14.4 Voltage Divider and Switchable Battery Load .....             | 100        |

| 14.5 Additional Information .....                                  | 100        |

| <b>15. Multi-bit Serial Peripheral Interface (MSPI) .....</b>      | <b>101</b> |

| 15.1 Features .....                                                | 101        |

| 15.2 Functional Overview .....                                     | 101        |

| 15.3 MSPI Transfers .....                                          | 102        |

| 15.4 Pad Configuration and Enables .....                           | 104        |

| 15.5 Additional Information .....                                  | 107        |

| <b>16. I2C/SPI Master (IOM) .....</b>                              | <b>108</b> |

| 16.1 Features .....                                                | 108        |

| 16.1.1 Features common to all submodules .....                     | 108        |

| 16.1.2 I2C Master features .....                                   | 109        |

| 16.1.3 SPI Master features .....                                   | 109        |

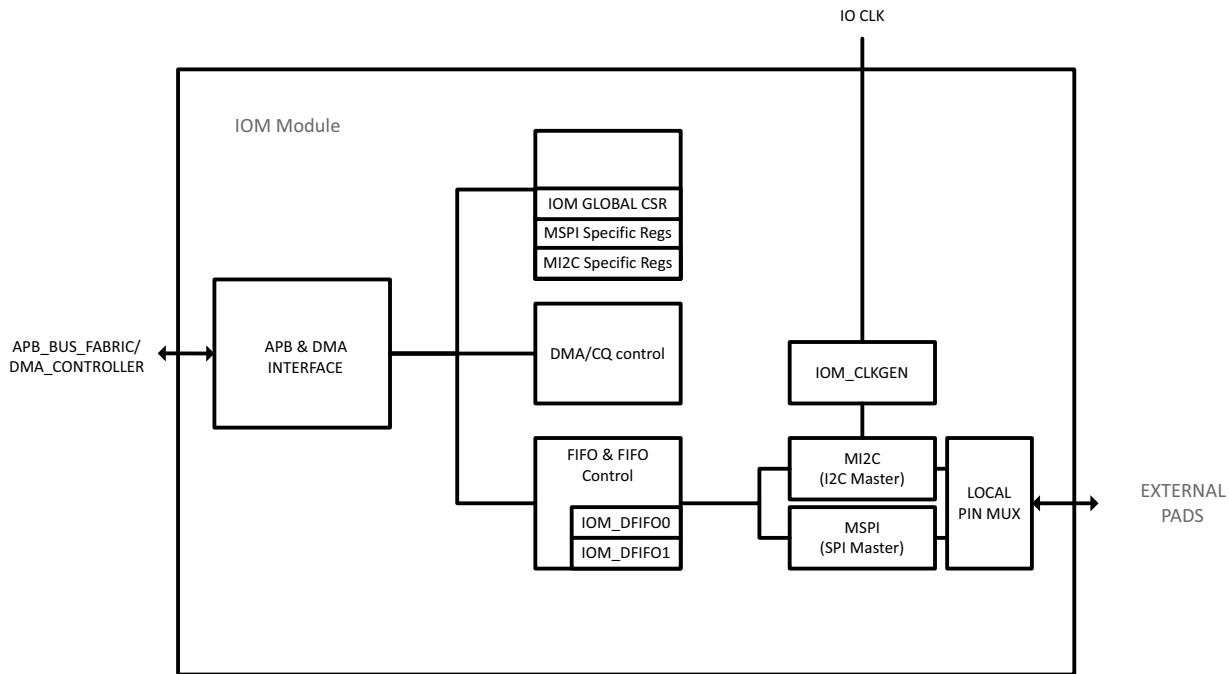

| 16.2 Functional Overview .....                                     | 109        |

| 16.3 Power Control .....                                           | 109        |

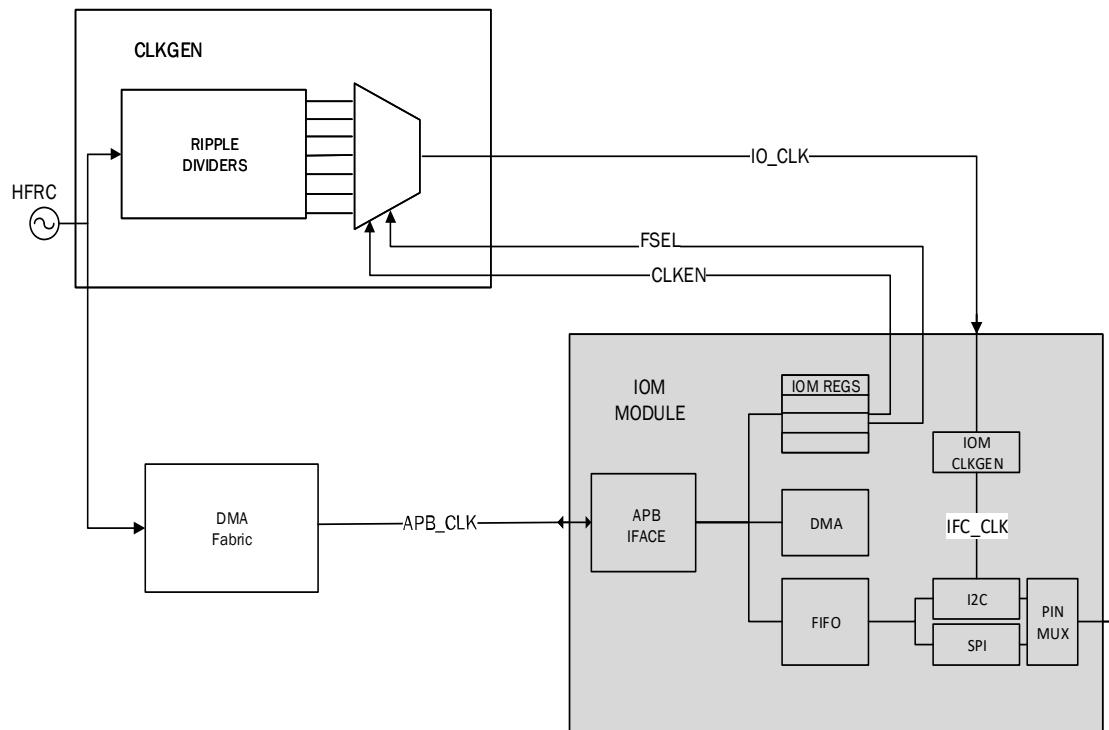

| 16.4 Clocking and Resets .....                                     | 110        |

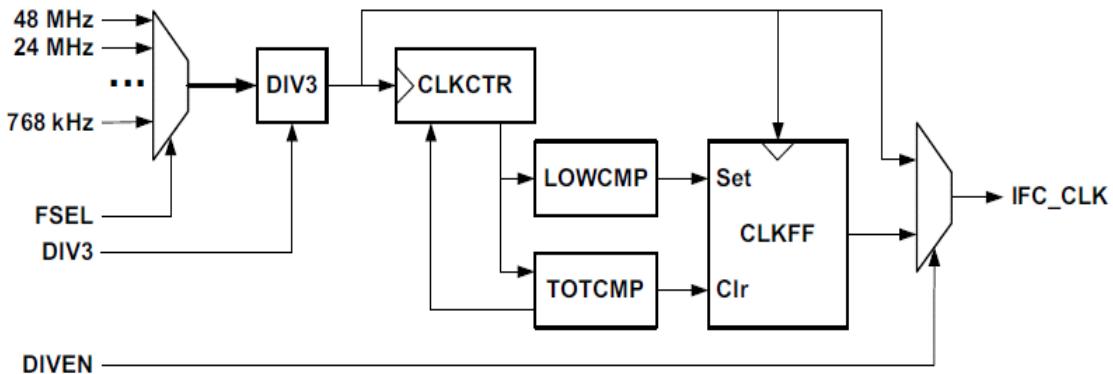

| 16.5 I2C Clock Generation .....                                    | 111        |

| 16.5.1 SPI Clock Generation .....                                  | 112        |

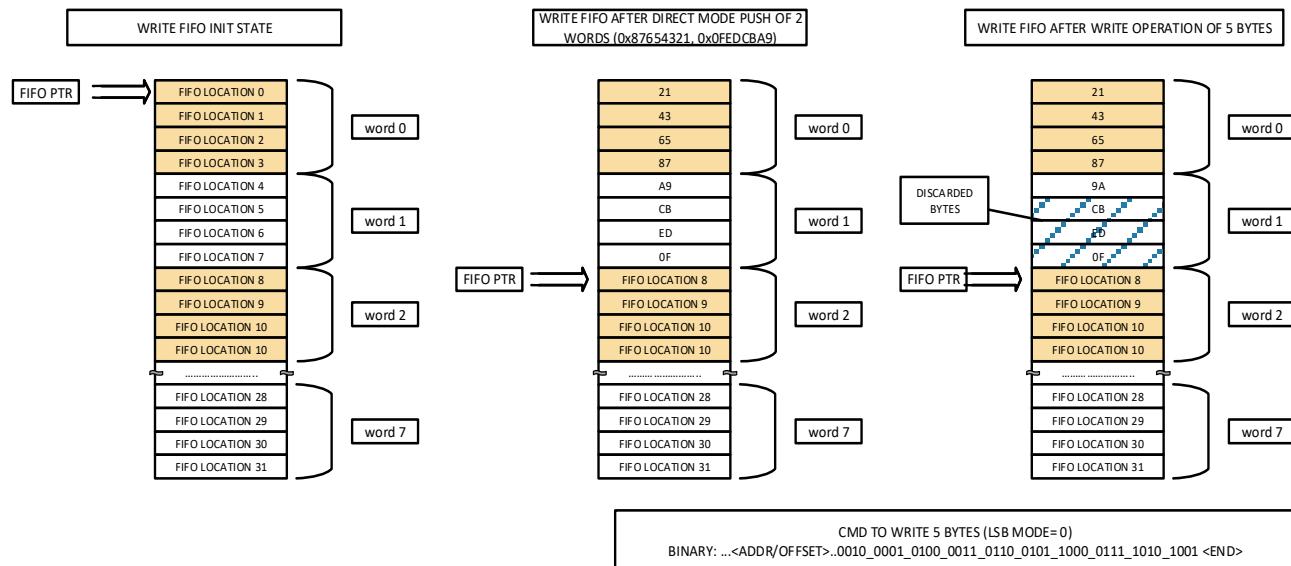

| 16.6 FIFO .....                                                    | 112        |

|                                                                     |            |

|---------------------------------------------------------------------|------------|

| 16.7 Data Alignment .....                                           | 113        |

| 16.7.1 Direct Mode Data Transfers .....                             | 113        |

| 16.7.2 DMA Data transfers .....                                     | 114        |

| 16.8 Transaction Initiation .....                                   | 115        |

| 16.9 Command Queue .....                                            | 115        |

| 16.9.1 CQ Programming Notes .....                                   | 118        |

| 16.10 Additional Information .....                                  | 119        |

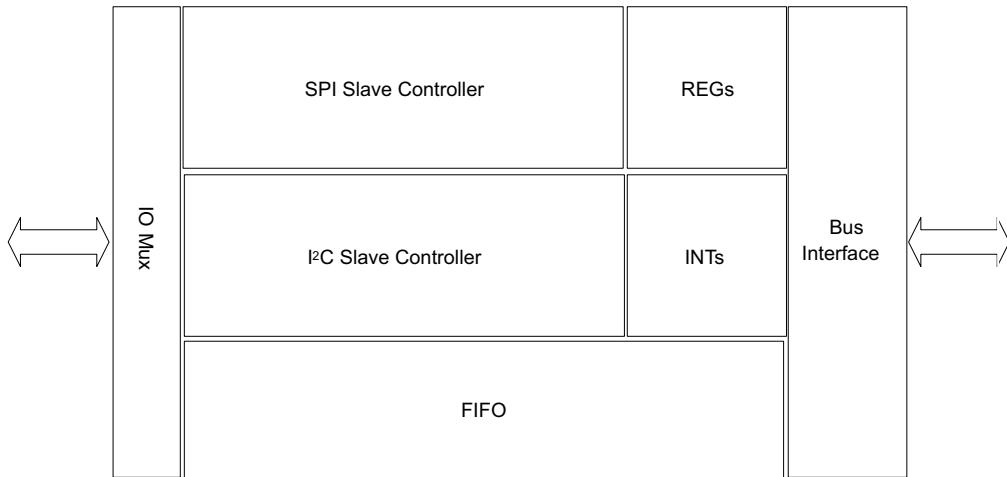

| <b>17. I2C/SPI Slave (IOS) .....</b>                                | <b>120</b> |

| 17.1 Functional Overview .....                                      | 120        |

| 17.2 Additional Information .....                                   | 120        |

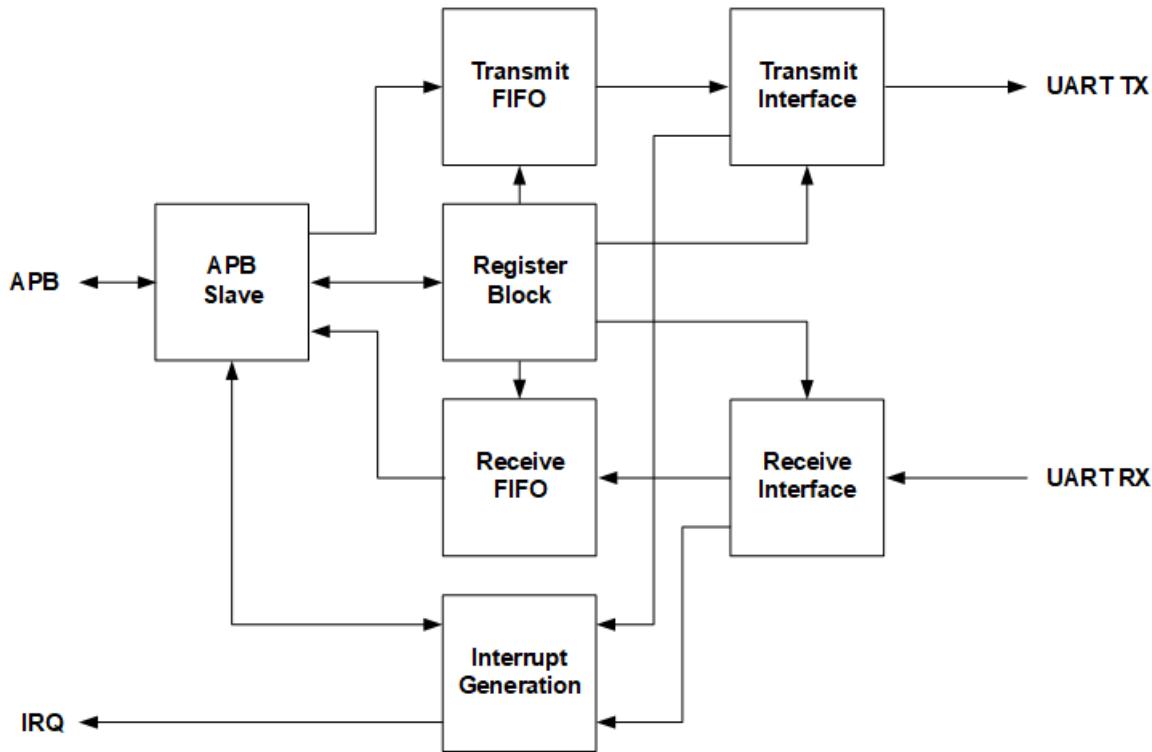

| <b>18. Universal Asynchronous Receiver/Transmitter (UART) .....</b> | <b>122</b> |

| 18.1 Features .....                                                 | 122        |

| 18.2 Functional Overview .....                                      | 122        |

| 18.3 Power Control .....                                            | 123        |

| 18.4 Additional Information .....                                   | 123        |

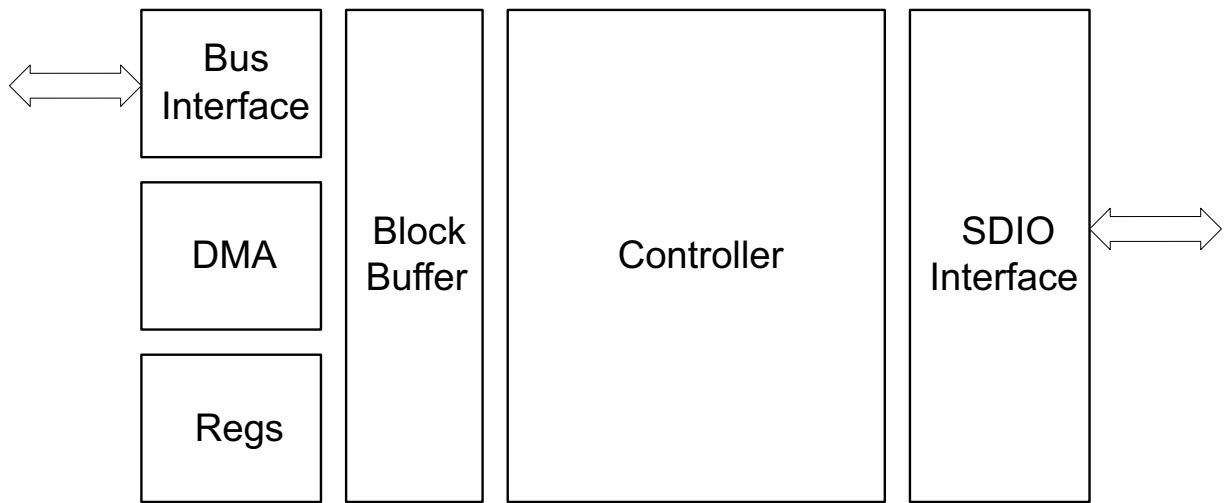

| <b>19. Secure Digital Input Output (SDIO) .....</b>                 | <b>125</b> |

| 19.1 Features .....                                                 | 125        |

| 19.2 Functional Overview .....                                      | 125        |

| 19.3 Additional Information .....                                   | 125        |

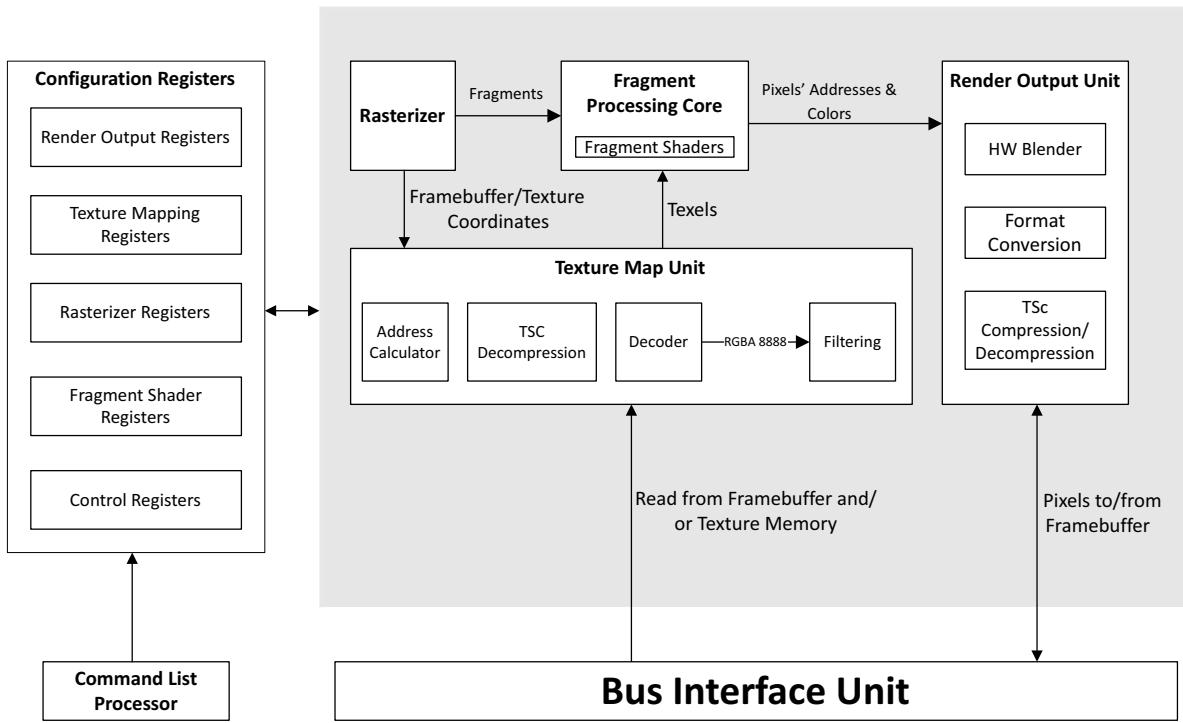

| <b>20. Graphics Processing Unit (GPU) .....</b>                     | <b>127</b> |

| 20.1 Features .....                                                 | 127        |

| 20.2 Functional Overview .....                                      | 128        |

| 20.3 Architecture .....                                             | 128        |

| 20.3.1 I/O Interfaces .....                                         | 128        |

| 20.3.2 Graphics Pipeline .....                                      | 129        |

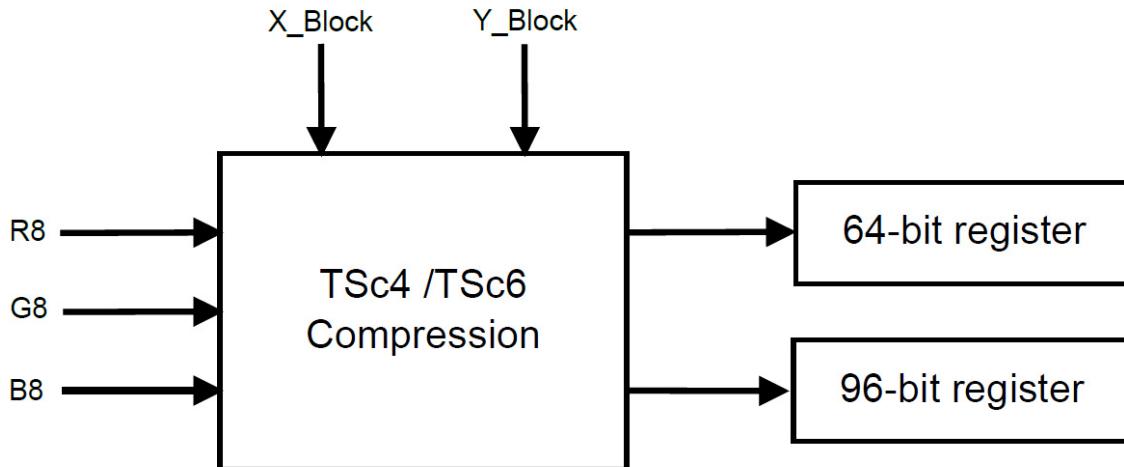

| 20.3.3 Frame buffer Compression .....                               | 132        |

| 20.3.4 Color Modes .....                                            | 133        |

| 20.4 Additional Information .....                                   | 140        |

| <b>21. PDM-to-PCM Converter Module (PDM) .....</b>                  | <b>142</b> |

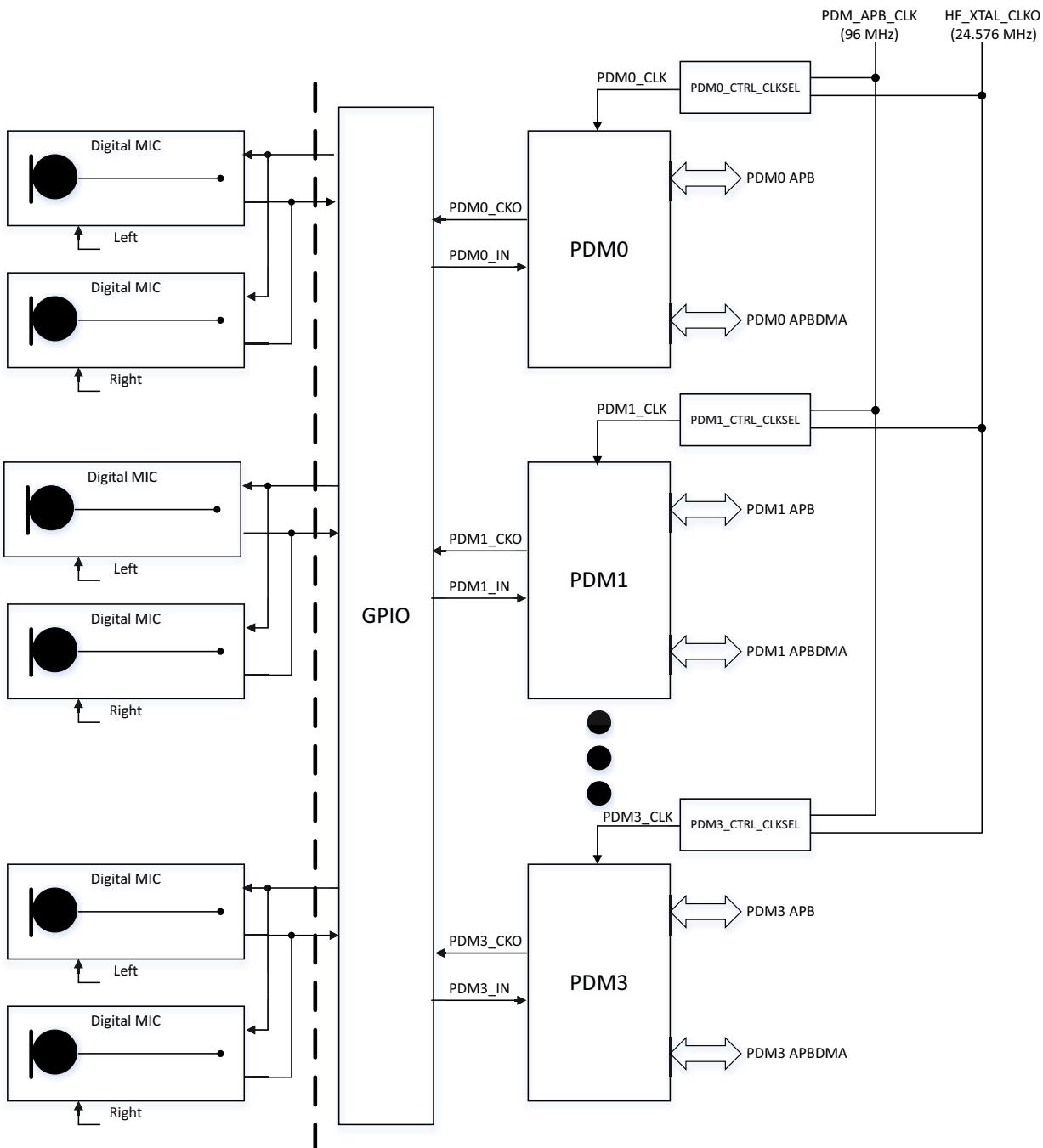

| 21.1 Features .....                                                 | 143        |

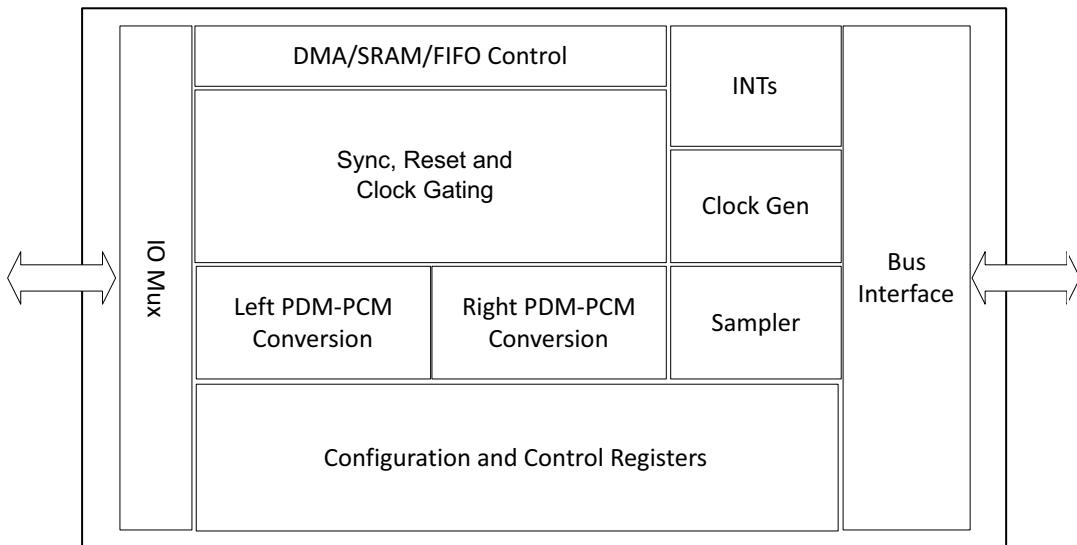

| 21.2 Functional Overview .....                                      | 144        |

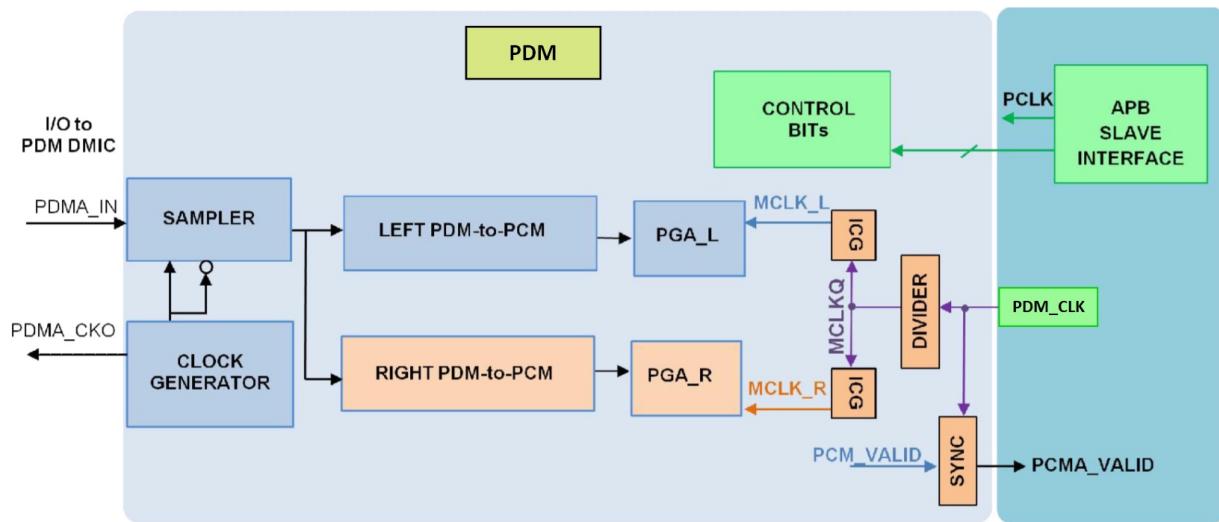

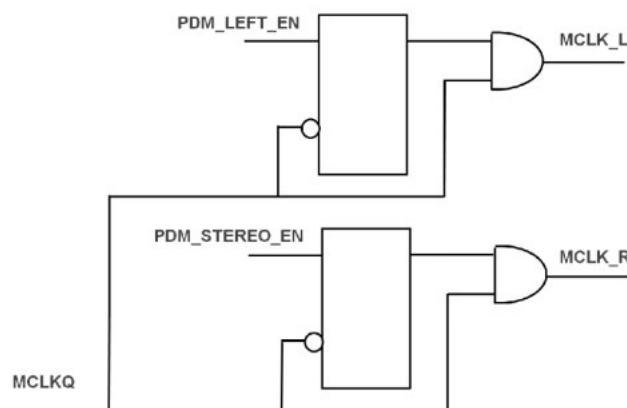

| 21.3 PDM-to-PCM Converter Clocking Mechanism .....                  | 144        |

| 21.3.1 Clock Gating and Data Synchronization .....                  | 146        |

| 21.4 Additional Information .....                                   | 147        |

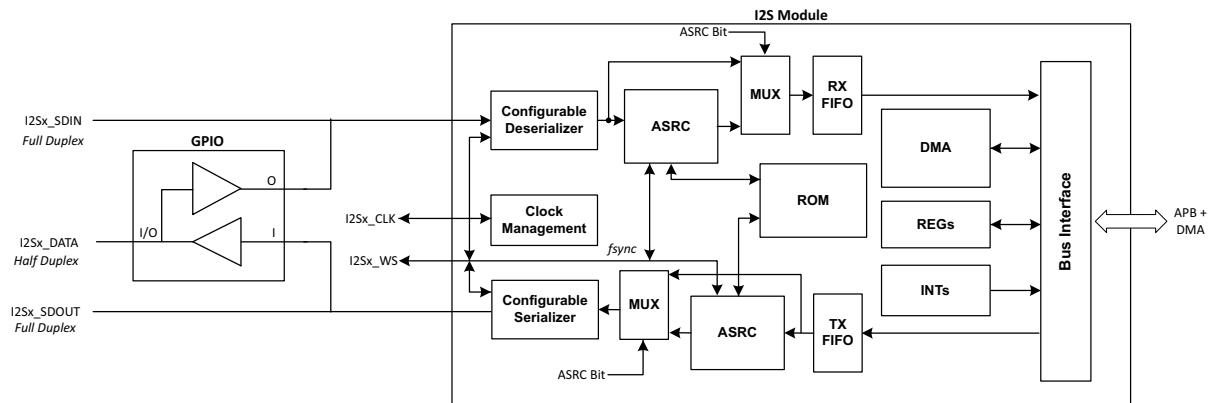

| <b>22. Inter-IC Sound (I2S) .....</b>                               | <b>150</b> |

| 22.1 Features .....                                                 | 150        |

| 22.2 Functional Overview .....                                      | 151        |

| 22.3 Additional Information .....                                   | 151        |

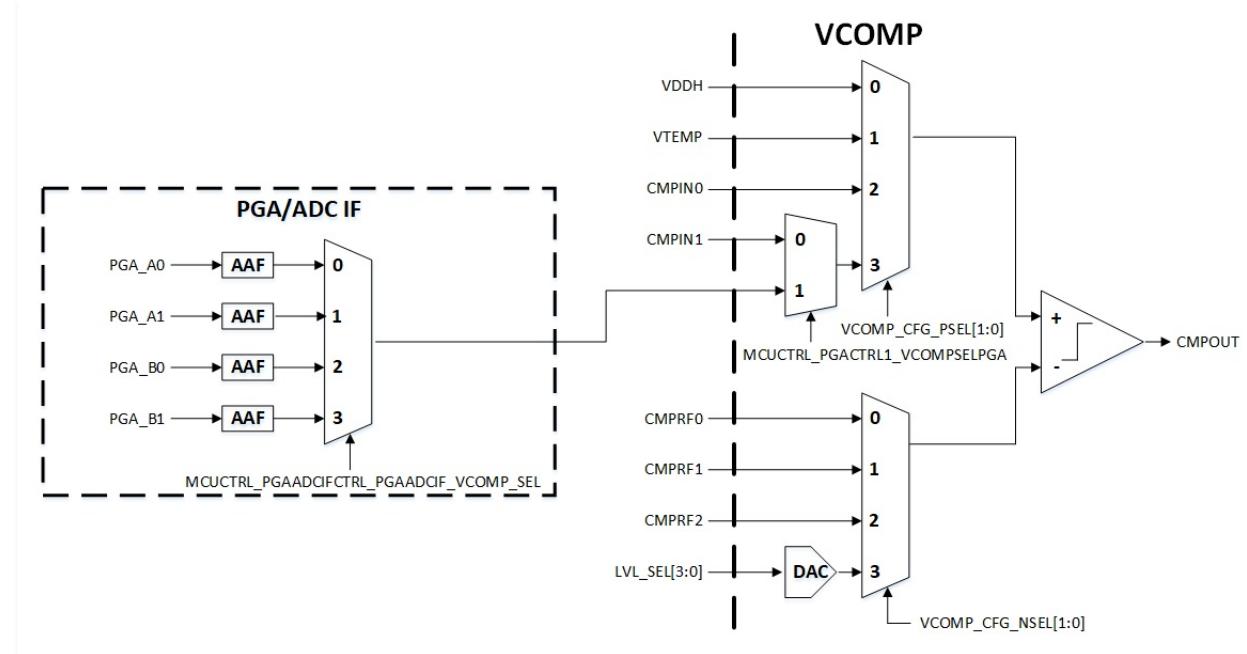

| <b>23. Voltage Comparator (VCOMP) .....</b>                         | <b>152</b> |

| 23.1 Functional Overview .....                                      | 152        |

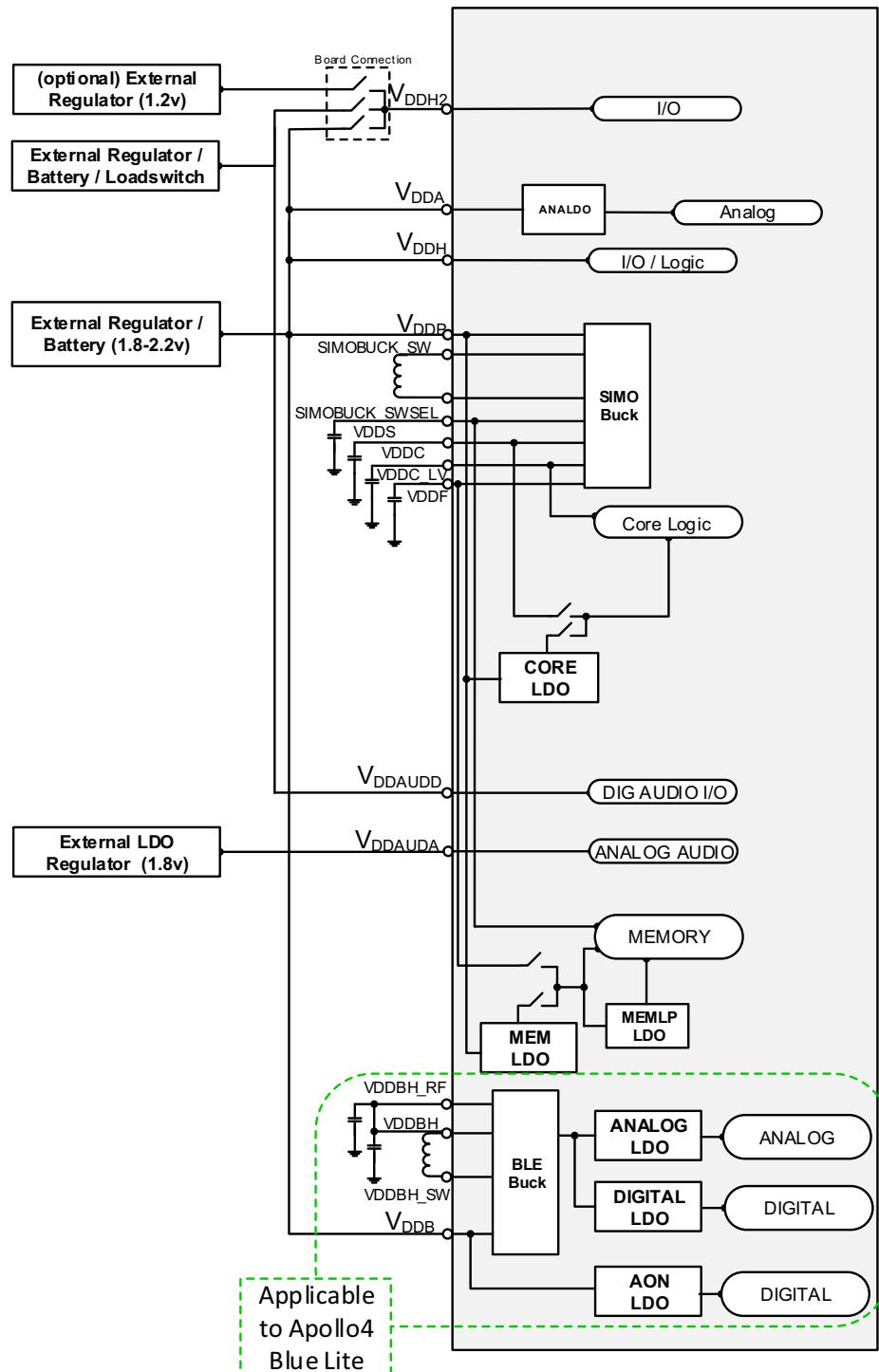

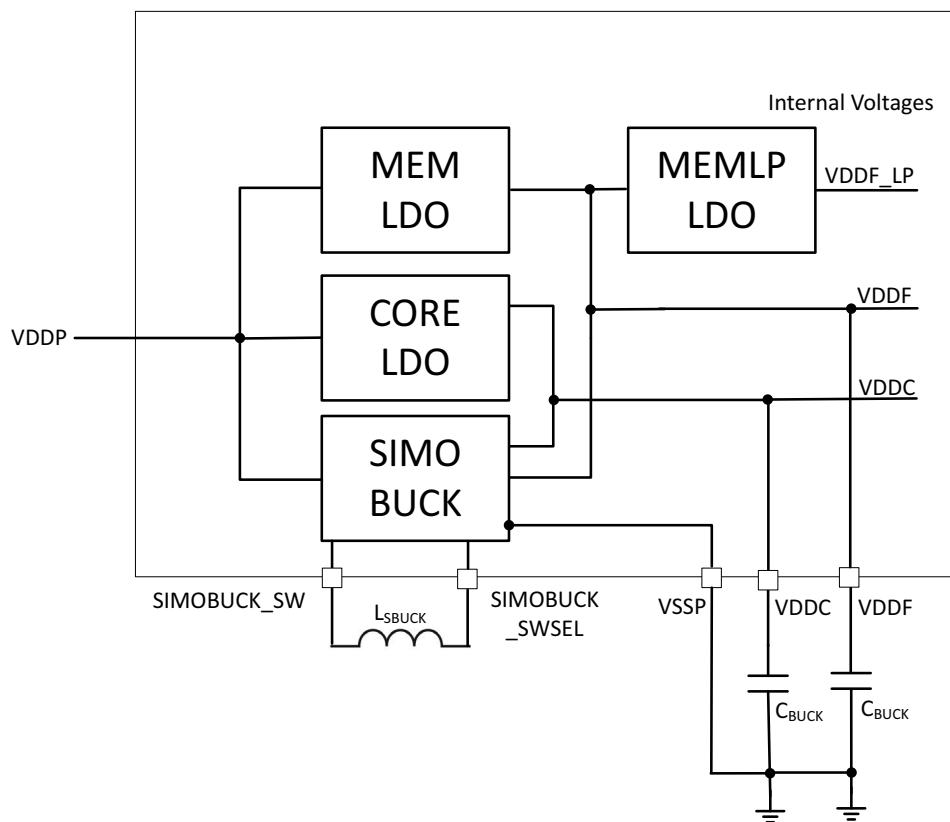

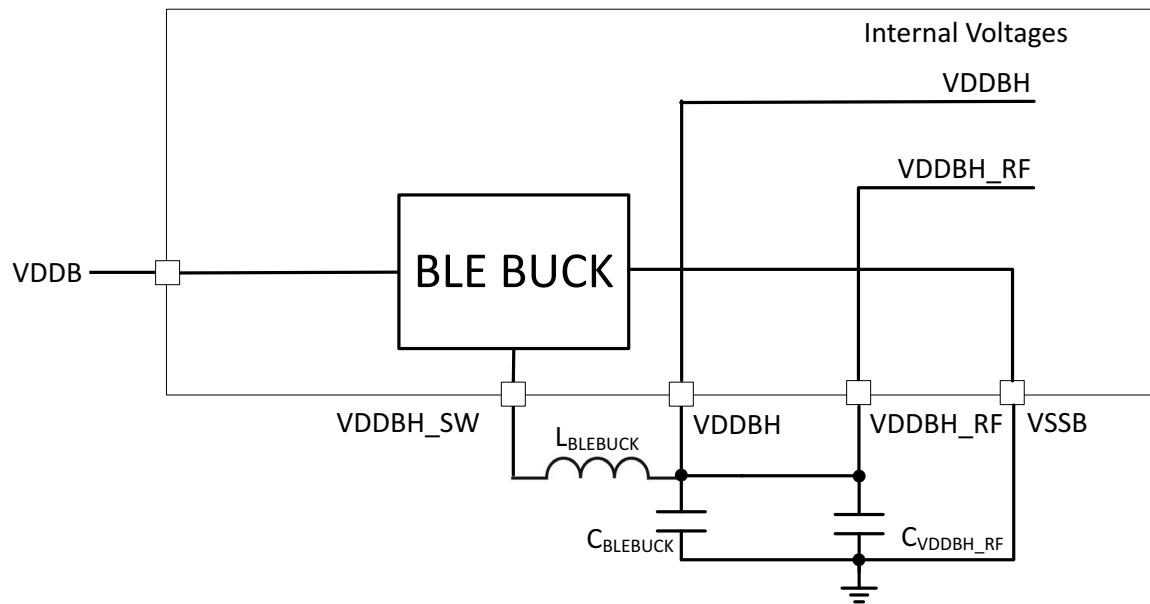

| <b>24. Voltage Regulator Module .....</b>                           | <b>154</b> |

| 24.1 Functional Overview .....                                      | 155        |

| 24.2 SIMO Buck .....                                                | 155        |

| 24.3 BLE Buck .....                                                 | 155        |

| <b>25. Package Mechanical Information .....</b>                     | <b>156</b> |

| 25.1 Apollo4 Blue Lite SoC BGA Package .....                        | 156        |

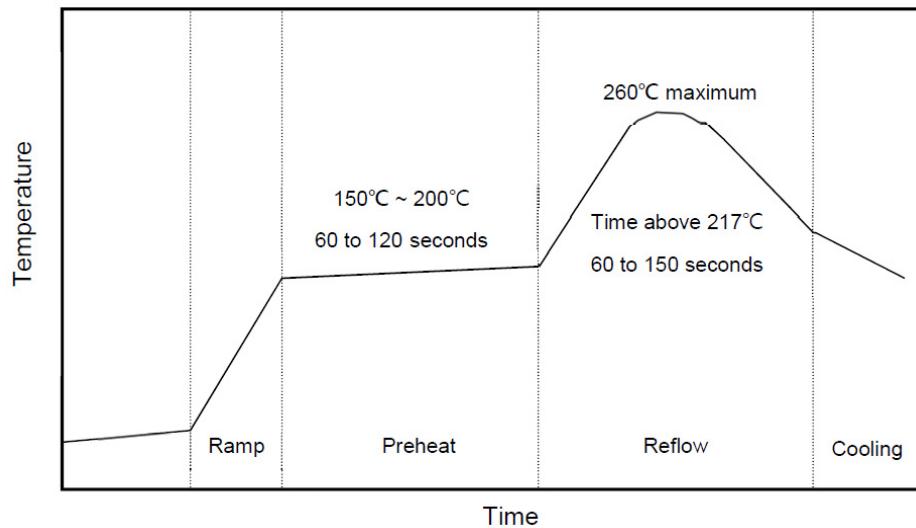

| 25.2 Reflow Profile .....                                           | 157        |

| <b>26. Electrical Characteristics .....</b>                         | <b>158</b> |

| 26.1 Absolute Maximum Ratings .....                                 | 159        |

---

|                                                                      |            |

|----------------------------------------------------------------------|------------|

| 26.2 Recommended Operating Conditions .....                          | 160        |

| 26.2.1 Voltage Supplies .....                                        | 160        |

| 26.2.2 VDDAUDA Voltage Supply Requirements .....                     | 161        |

| 26.2.3 Power Sequence .....                                          | 162        |

| 26.2.4 Recommended External Components for the Buck Converters ..... | 163        |

| 26.2.5 Recommended External Components for Voltage Supplies .....    | 165        |

| 26.3 Current Consumption .....                                       | 166        |

| 26.4 Non-volatile Memory (NVM) .....                                 | 168        |

| 26.5 Power-On RESET (POR) and Brown-Out Detector (BOD) .....         | 169        |

| 26.6 General Purpose Input/Output (GPIO) .....                       | 170        |

| 26.7 Clocks/Oscillators .....                                        | 171        |

| 26.8 Real Time Clock (RTC) .....                                     | 173        |

| 26.9 STIMER .....                                                    | 174        |

| 26.10 Watchdog Timer (WDT) .....                                     | 175        |

| 26.11 Bluetooth Low Energy Controller .....                          | 176        |

| 26.12 Voltage Comparator (VCOMP) .....                               | 177        |

| 26.13 General Purpose Analog-to-Digital Converter (ADC) .....        | 178        |

| 26.14 Multi-bit Serial Peripheral Interface (MSPI) .....             | 180        |

| 26.15 I2C/SPI Master (IOM) .....                                     | 181        |

| 26.15.1 Serial Peripheral Interface (SPI) Master Interface .....     | 181        |

| 26.16 I2C/SPI Slave (IOS) .....                                      | 183        |

| 26.16.1 Serial Peripheral Interface (SPI) Slave Interface .....      | 183        |

| 26.17 Universal Asynchronous Receiver/Transmitter (UART) .....       | 184        |

| 26.18 Secure Digital Input Output (SDIO) .....                       | 185        |

| <b>27. Ordering Information .....</b>                                | <b>186</b> |

| <b>28. Document Revision History .....</b>                           | <b>187</b> |

## List of Figures

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

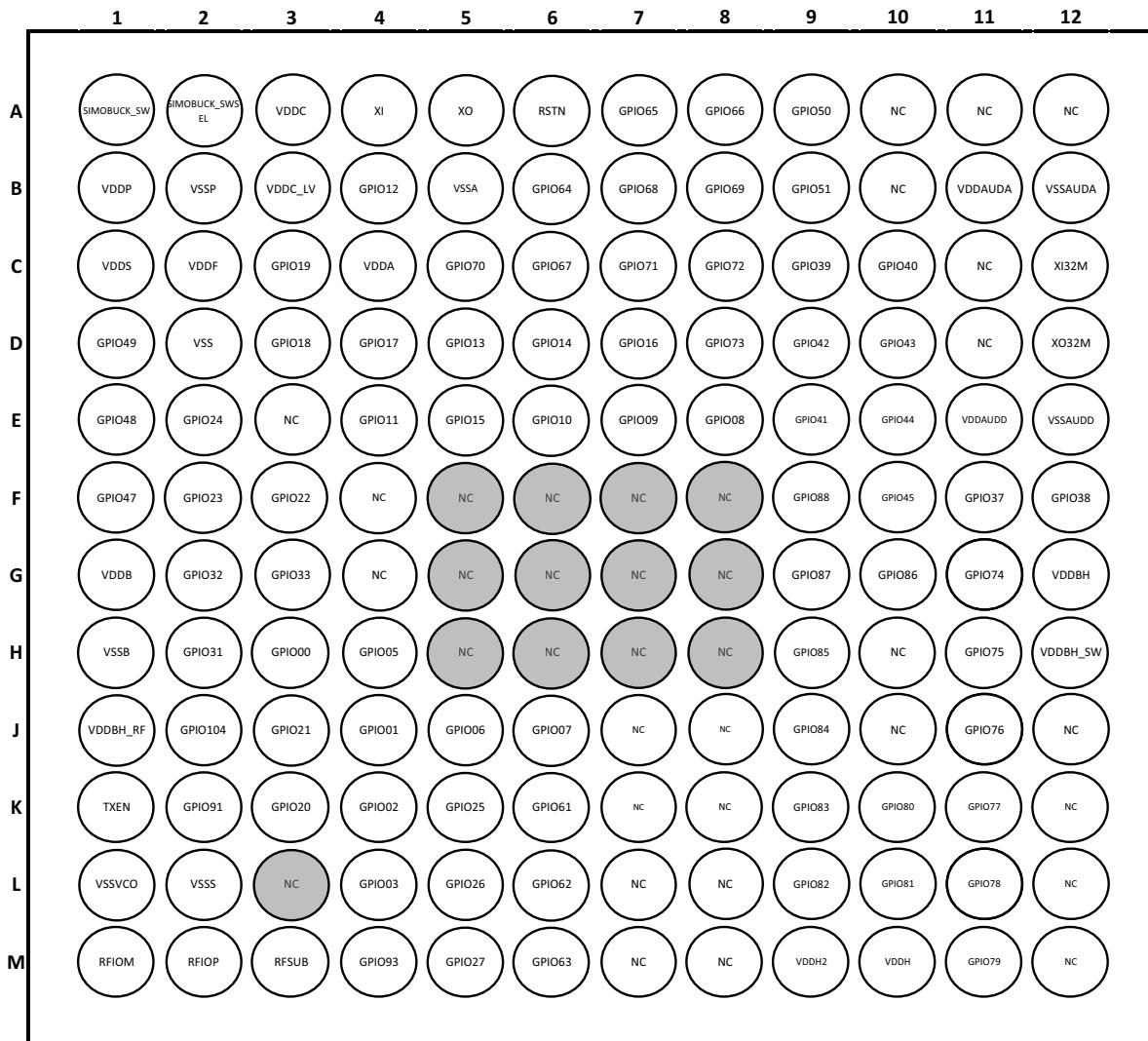

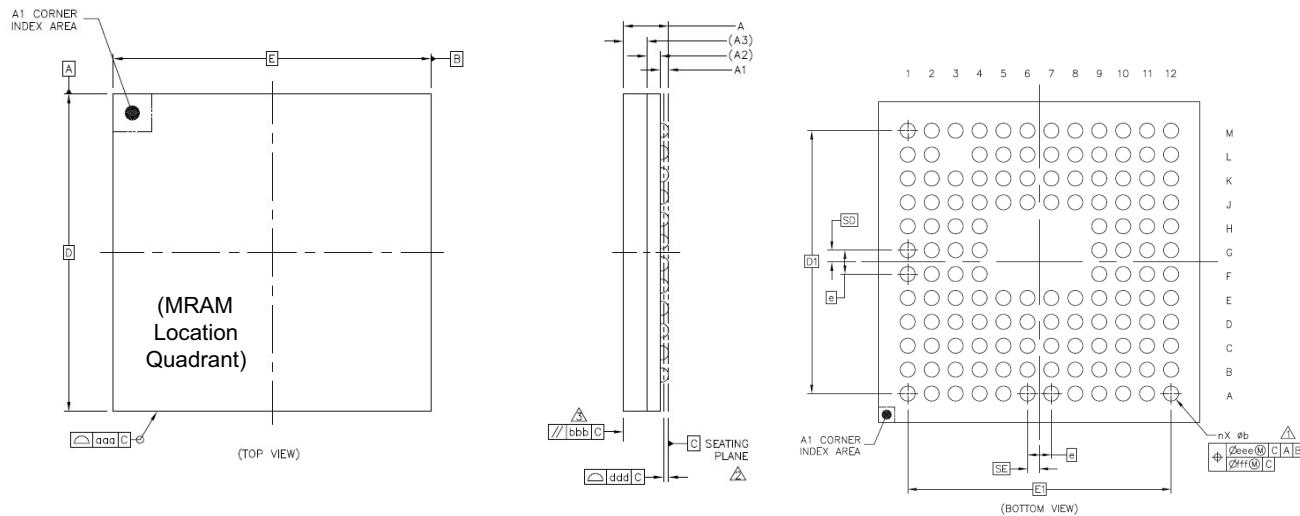

| Figure 1. Apollo4 Blue Lite SoC BGA Pin Configuration Diagram - Top View .....      | 10  |

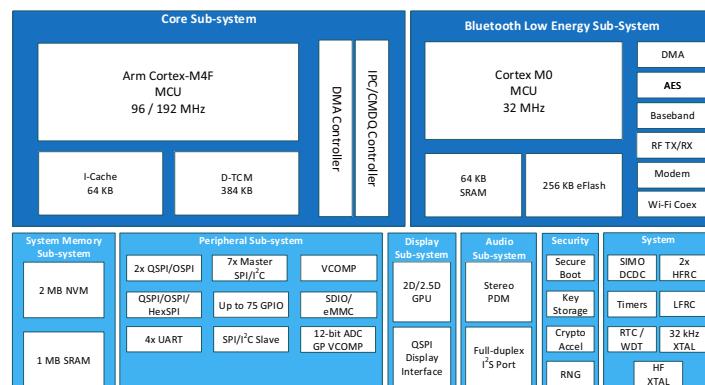

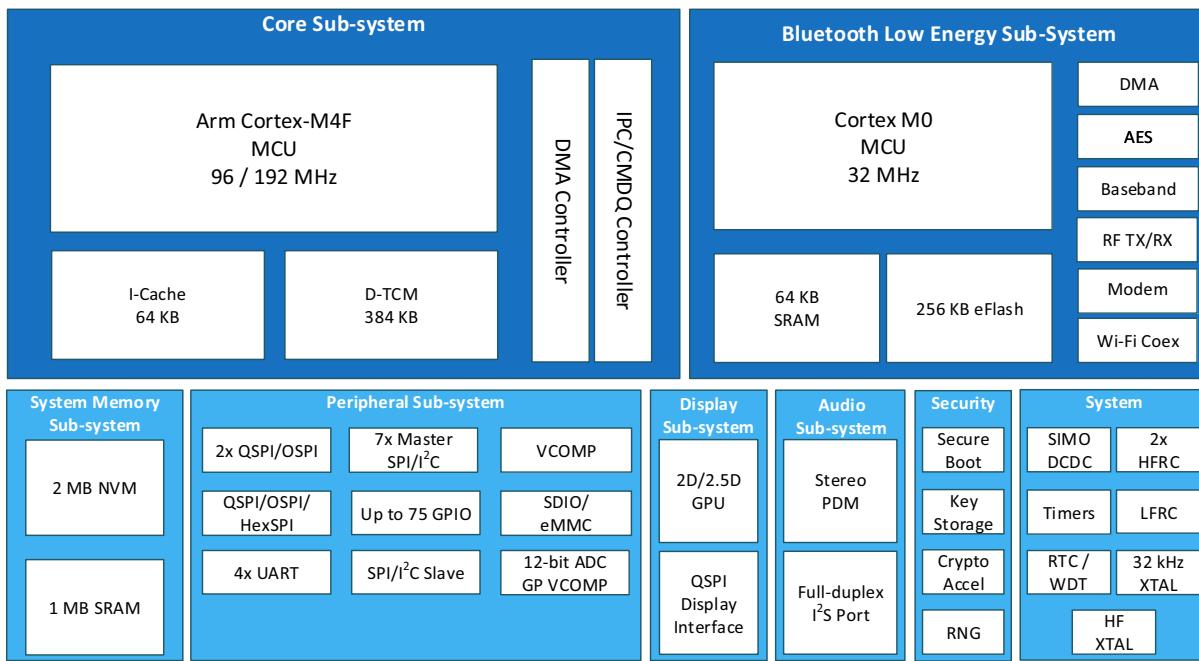

| Figure 2. Apollo4 Blue Lite SoC Block Diagram .....                                 | 38  |

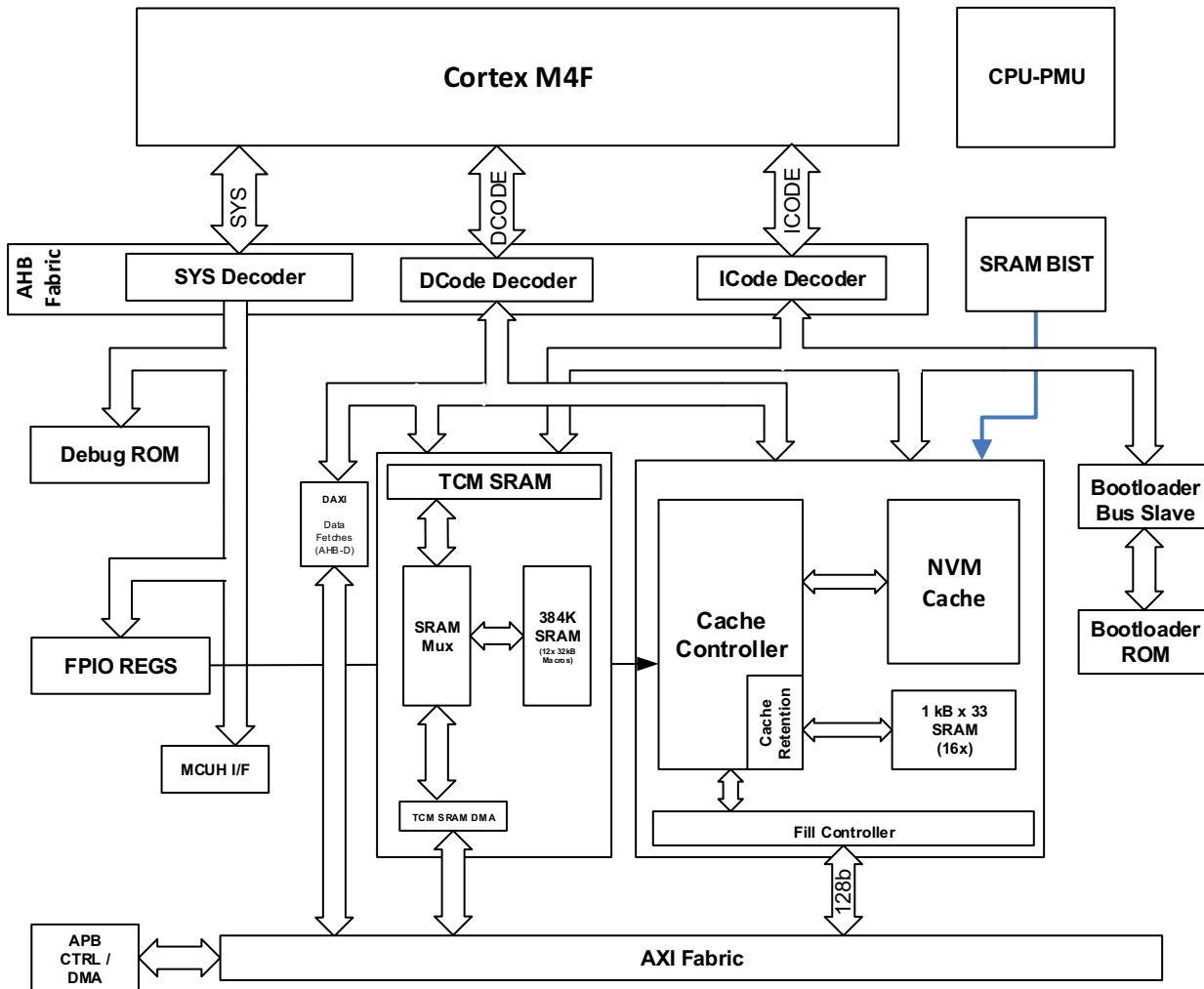

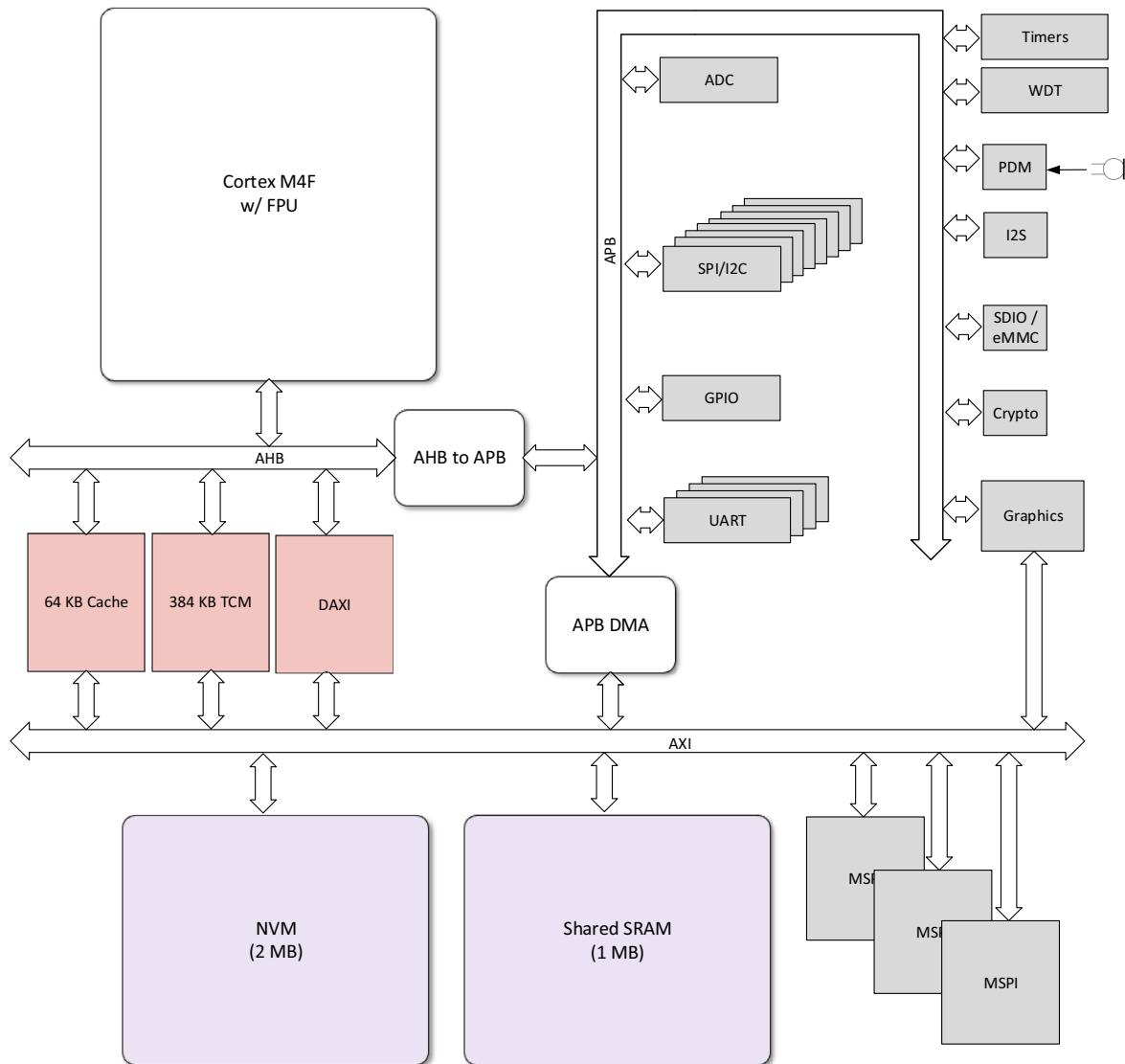

| Figure 3. Apollo4 Blue Lite SoC Core Block Diagram.....                             | 43  |

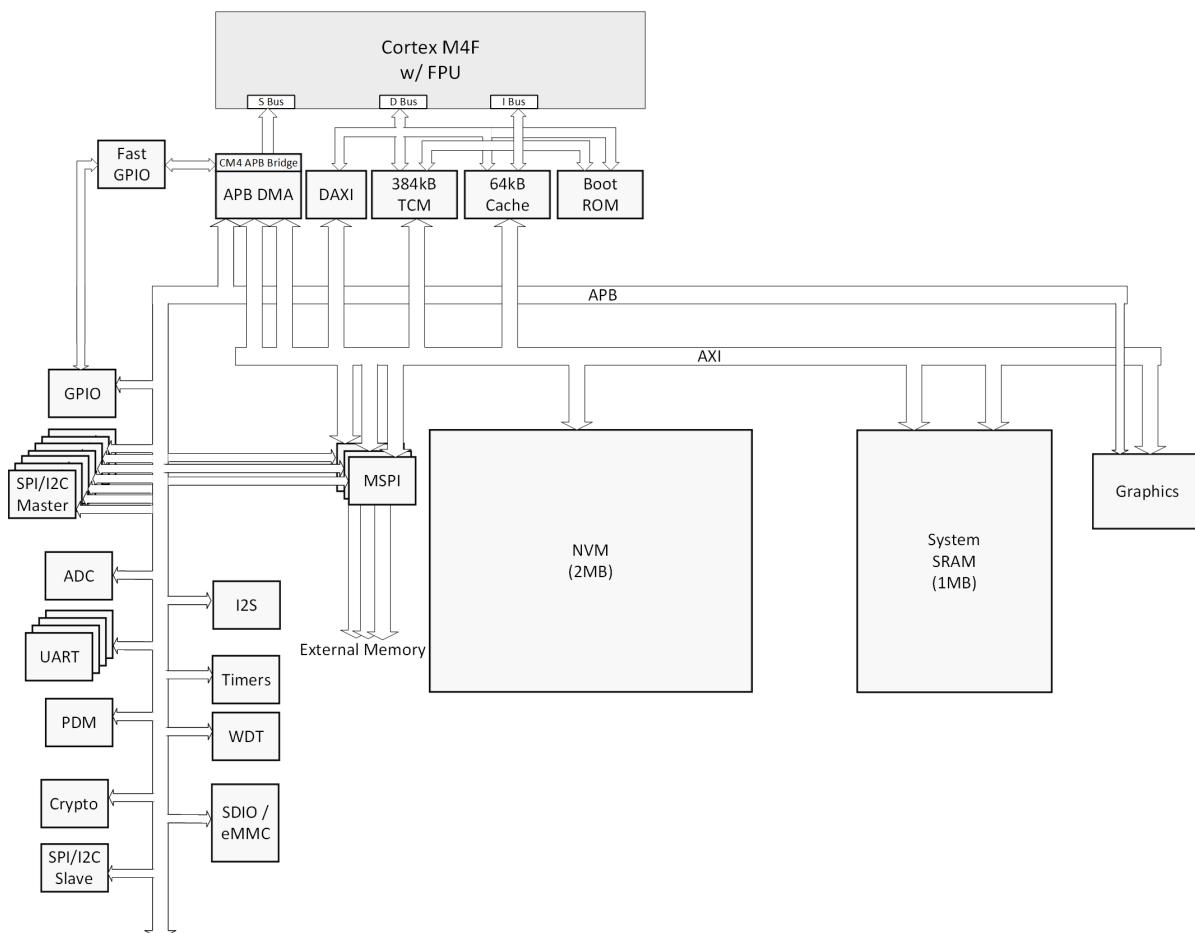

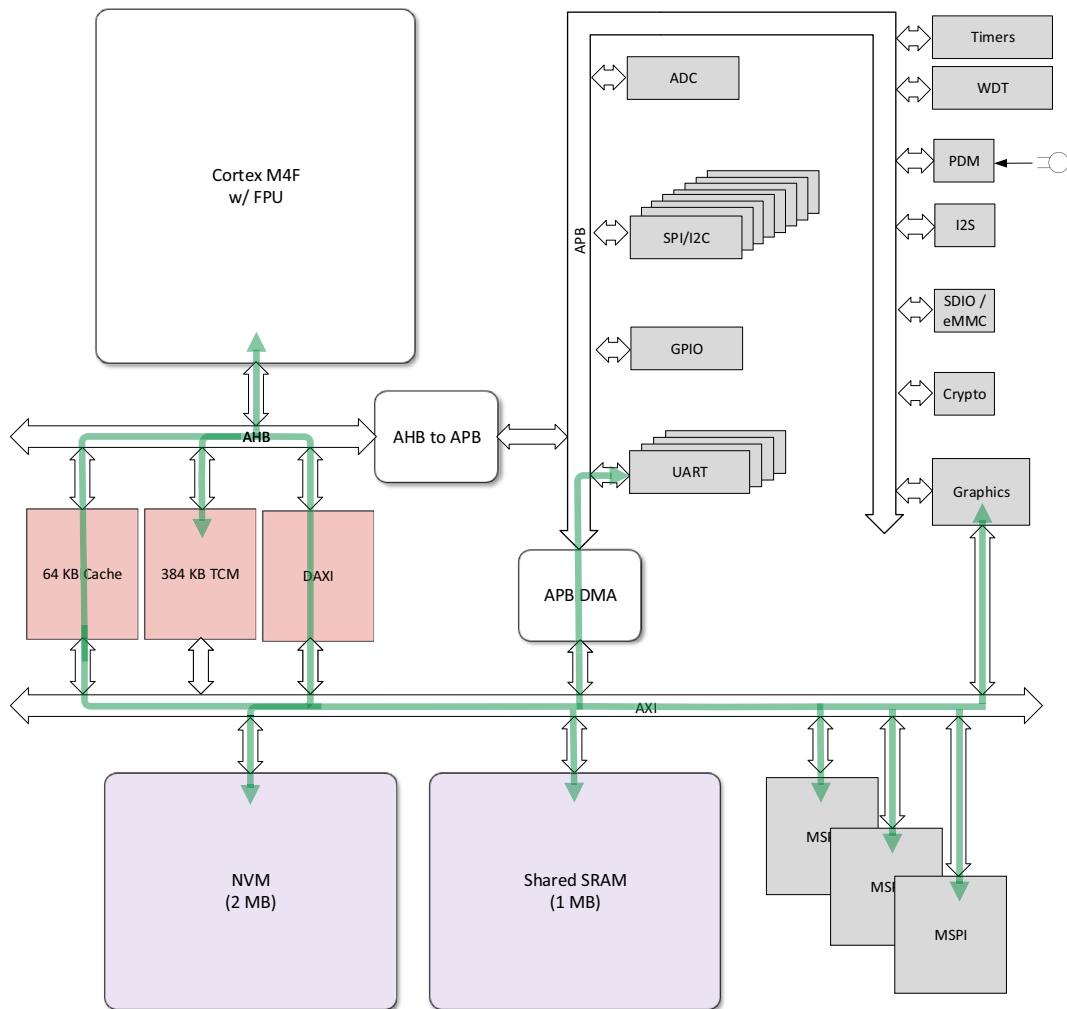

| Figure 4. Apollo4 SoC Peripherals, Memory and Buses.....                            | 58  |

| Figure 5. Apollo4 Blue Lite SoC Peripherals, Memory and Buses.....                  | 58  |

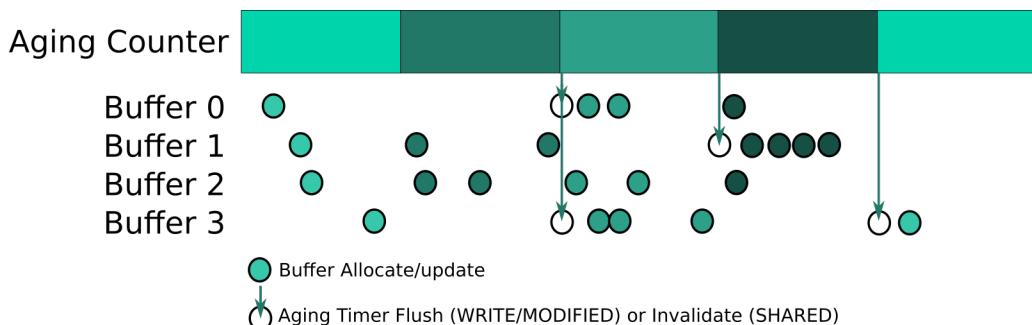

| Figure 6. Aging Counter Operation .....                                             | 62  |

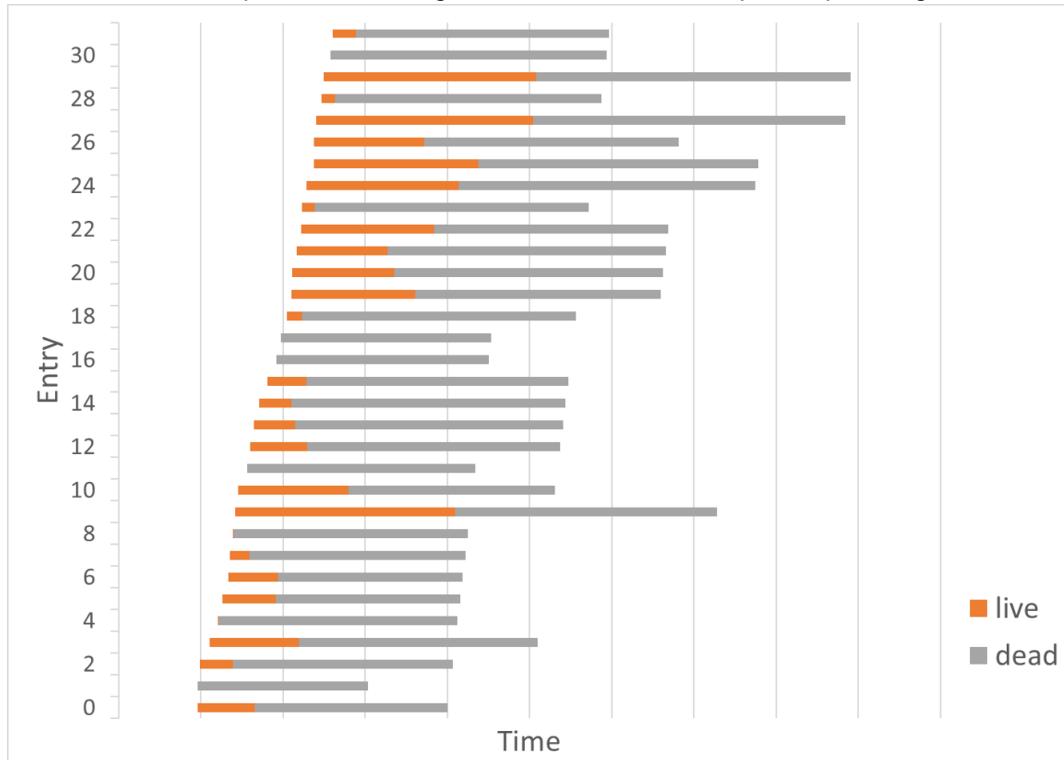

| Figure 7. Flush Spreading.....                                                      | 63  |

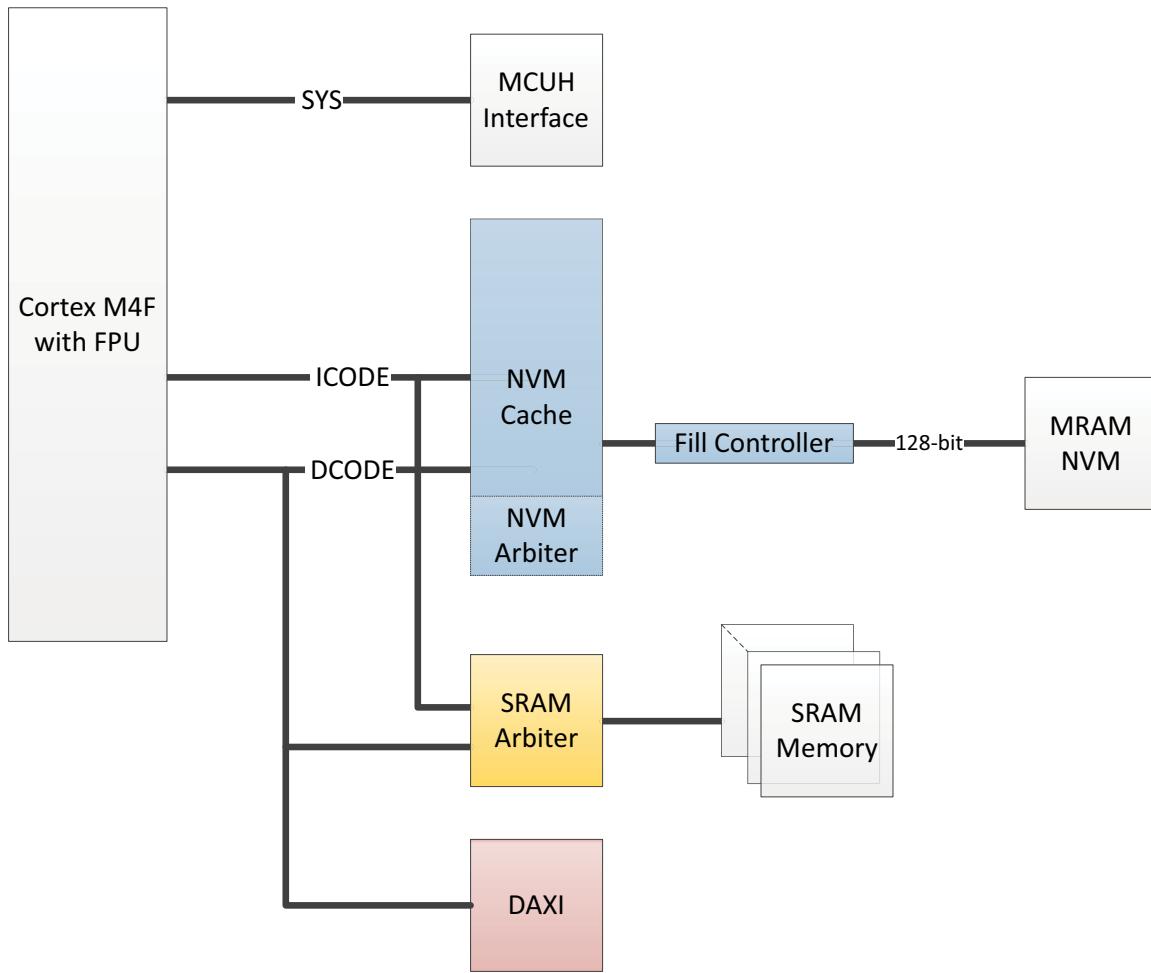

| Figure 8. Block Diagram for Apollo4 Blue Lite SoC NVM Cache.....                    | 65  |

| Figure 9. Apollo4 Blue Lite SoC Bus Architecture Block Diagram.....                 | 66  |

| Figure 10. Apollo4 Blue Lite SoC System Diagram .....                               | 68  |

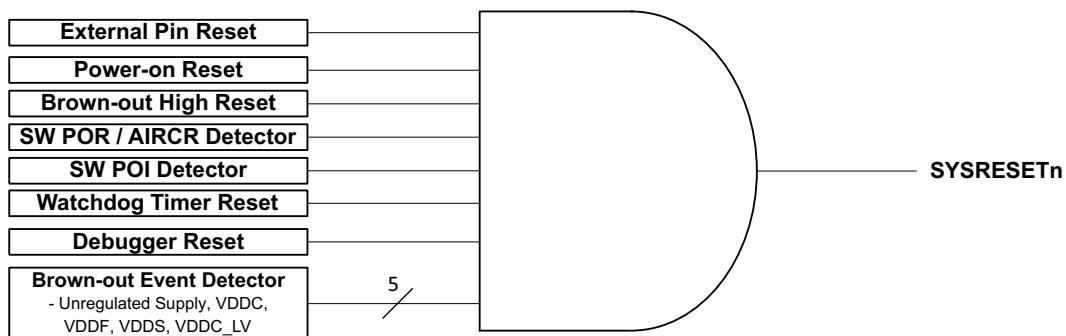

| Figure 11. Block diagram for the Reset Generator Module .....                       | 71  |

| Figure 12. Block diagram of circuitry for Reset pin .....                           | 72  |

| Figure 13. Block diagram for the Clock Generator.....                               | 74  |

| Figure 14. Block diagram for the Real Time Clock Module.....                        | 78  |

| Figure 15. Secure Boot Flow .....                                                   | 80  |

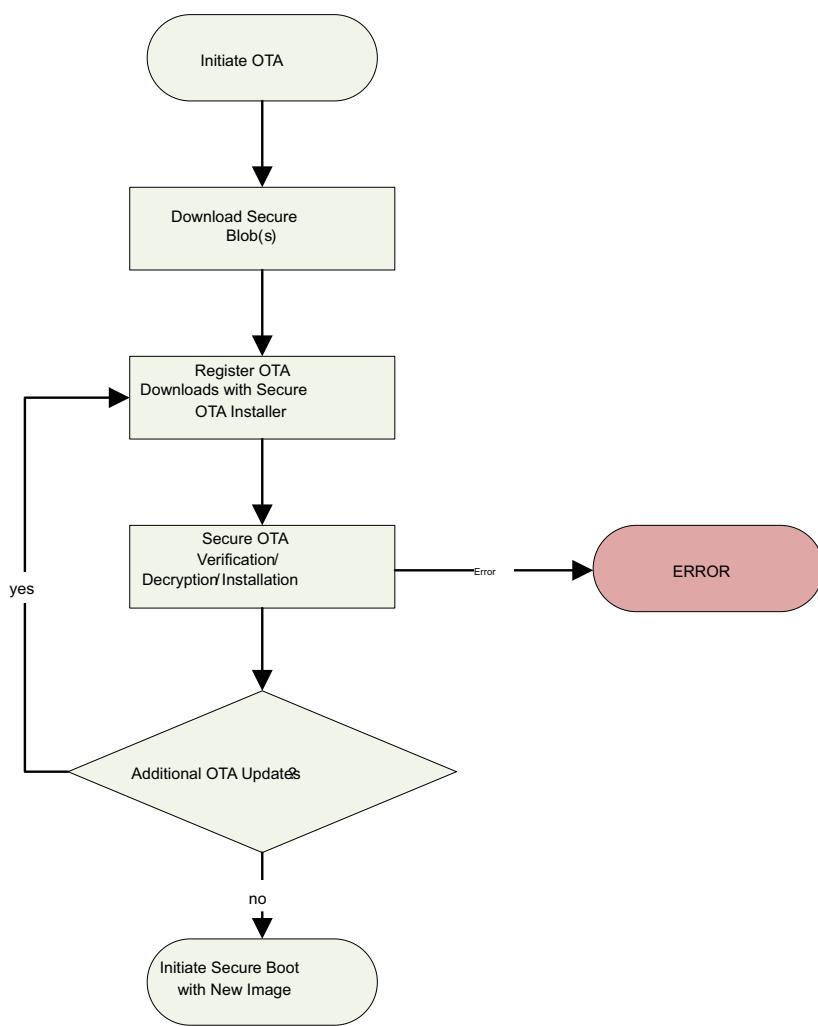

| Figure 16. Secure OTA Flow .....                                                    | 81  |

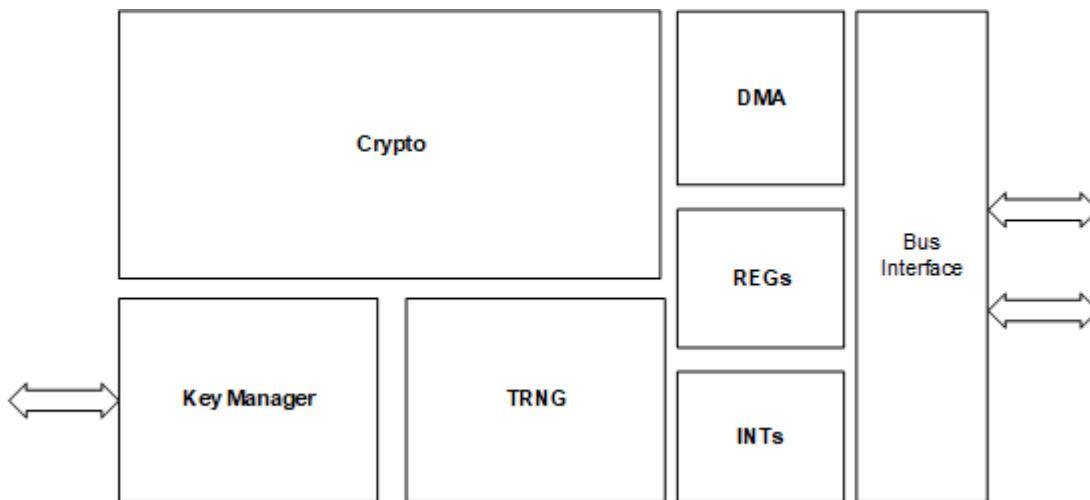

| Figure 17. Crypto Subsystem .....                                                   | 83  |

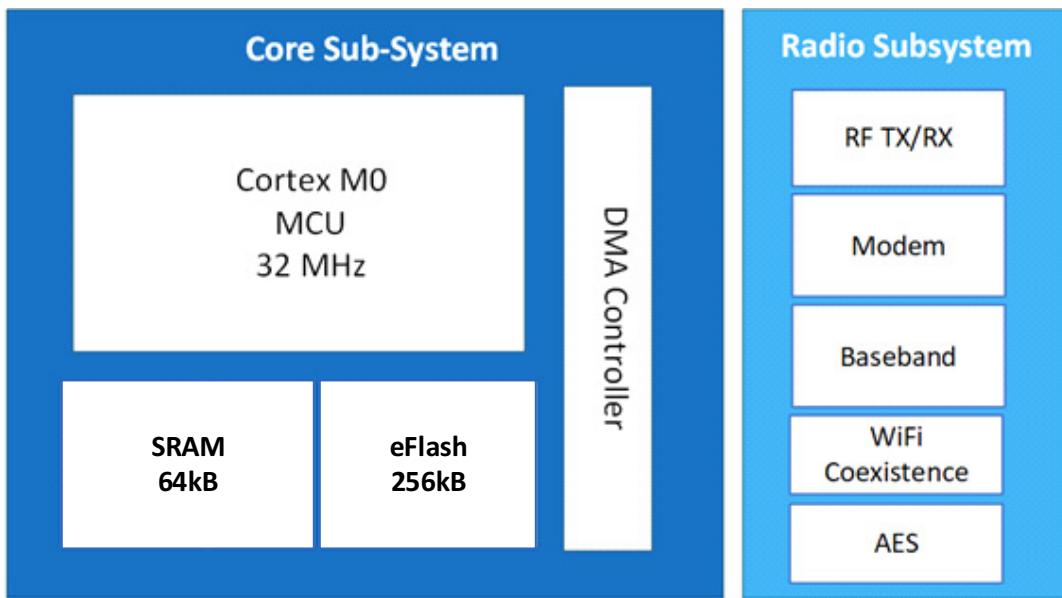

| Figure 18. Apollo4 Blue Lite SoC Bluetooth Low Energy Controller Block Diagram..... | 84  |

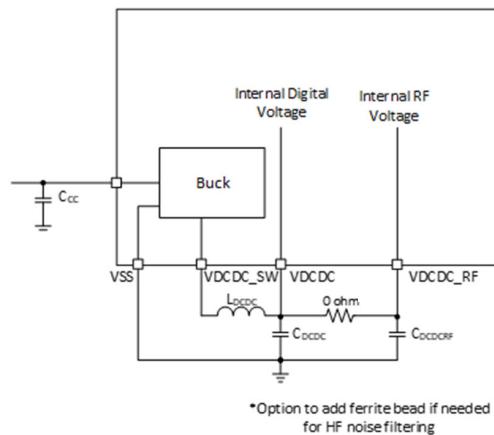

| Figure 19. Integration Diagram for Buck Enabled Configuration .....                 | 86  |

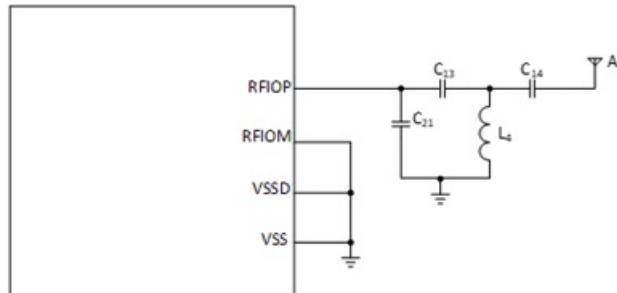

| Figure 20. Recommended Antenna Filter.....                                          | 86  |

| Figure 21. Block Diagram for One Counter/Timer .....                                | 87  |

| Figure 22. Block Diagram for the System Timer .....                                 | 89  |

| Figure 23. Block Diagram for the Watchdog Timer Module .....                        | 91  |

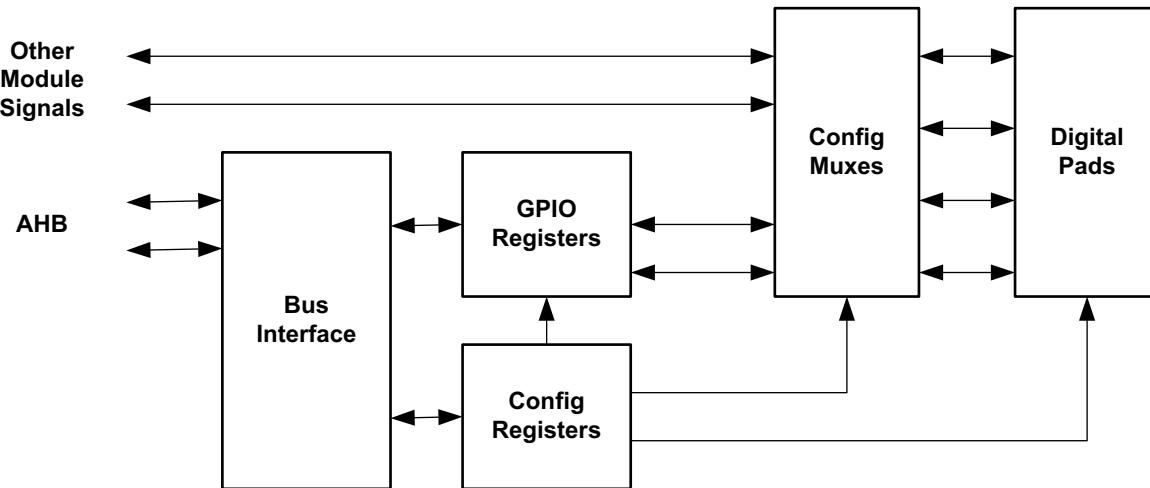

| Figure 24. Block diagram for the General Purpose I/O (GPIO) Module.....             | 92  |

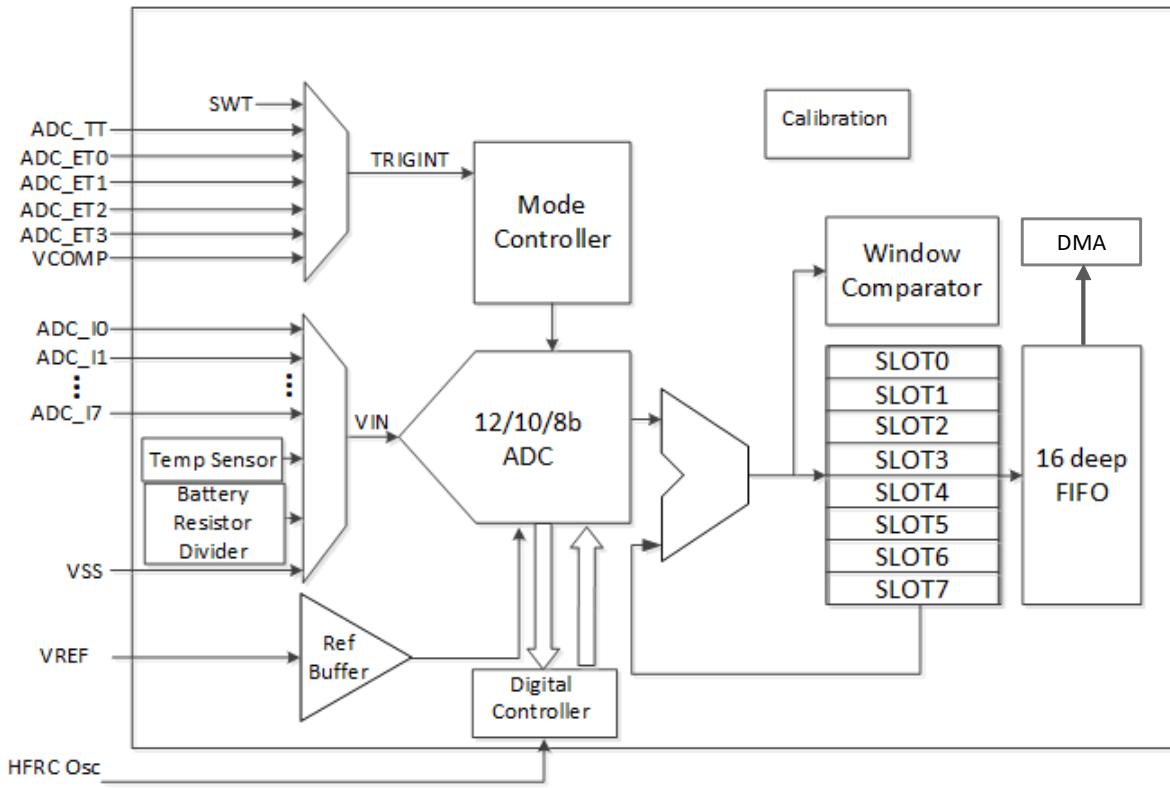

| Figure 25. Block Diagram for ADC and Temperature Sensor.....                        | 98  |

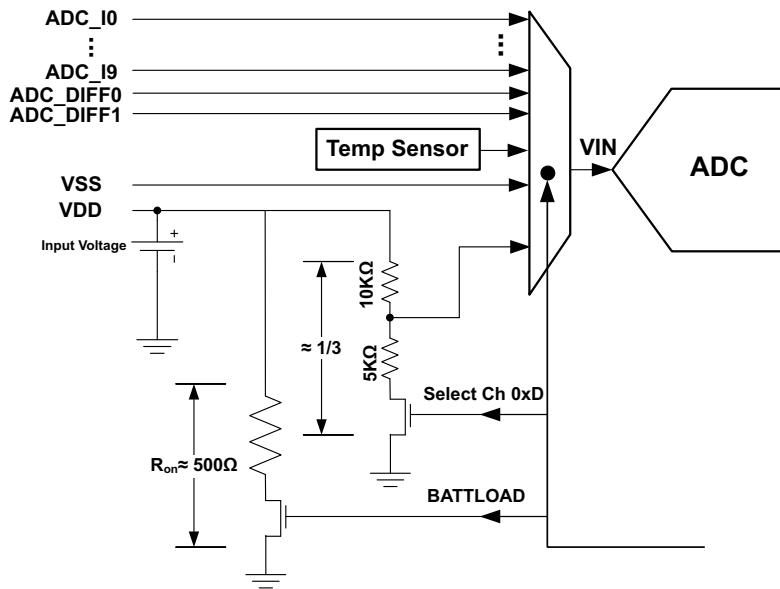

| Figure 26. Switchable Battery Load .....                                            | 100 |

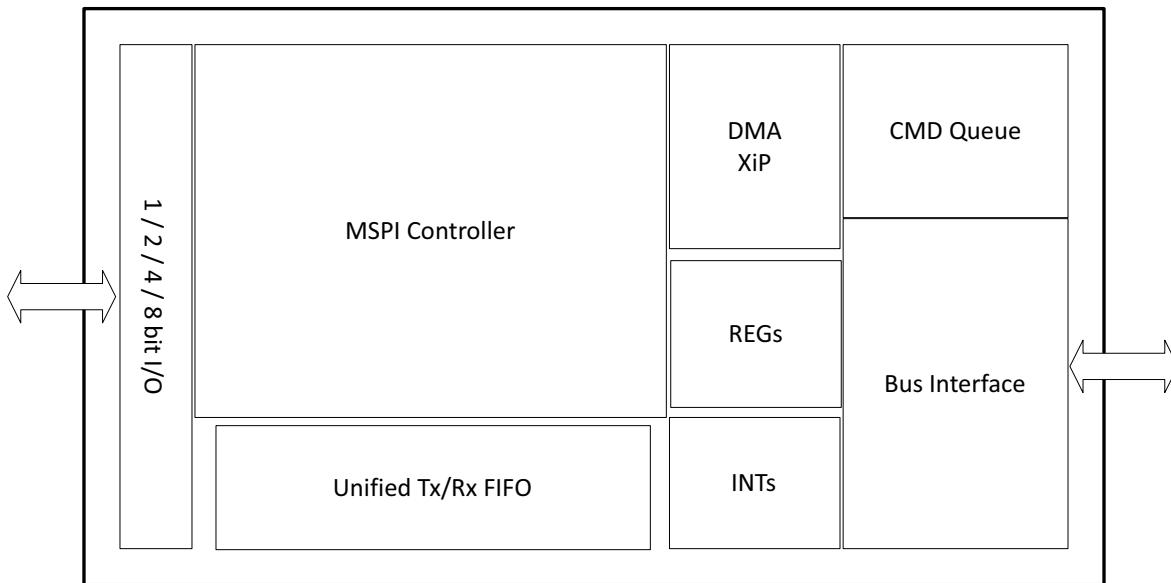

| Figure 27. Block Diagram for the MSPI Master Module.....                            | 101 |

| Figure 28. Block Diagram for the I2C/SPI Master Module .....                        | 108 |

| Figure 29. Clocking Structure for IOM Module.....                                   | 110 |

| Figure 30. IO_CLK Generation .....                                                  | 111 |

| Figure 31. Direct Mode 5-byte Write Transfer.....                                   | 113 |

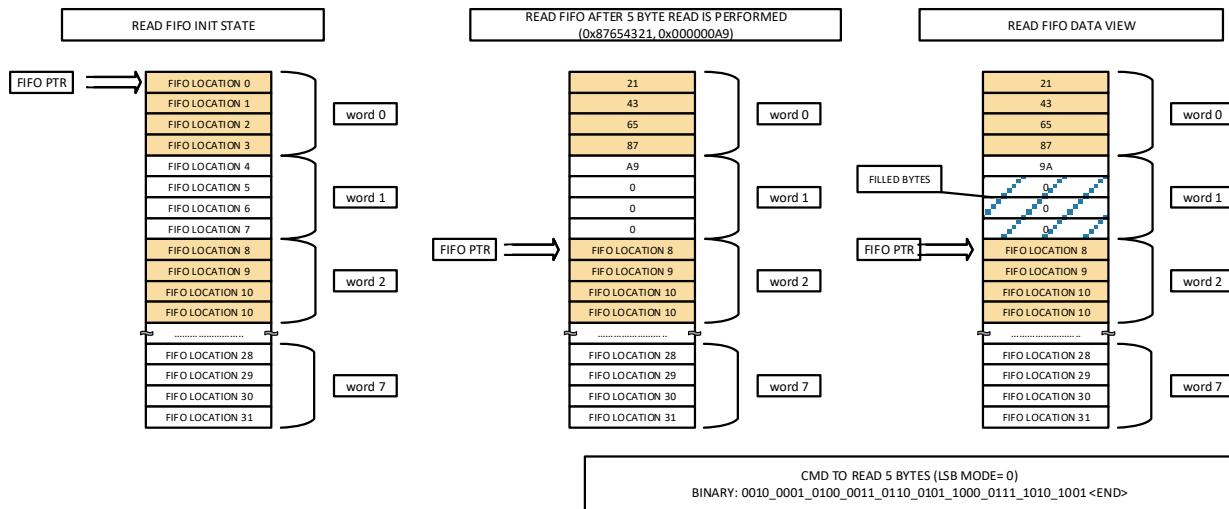

| Figure 32. Direct Mode 5-byte Read.....                                             | 114 |

| Figure 33. Register Write Data Fetches.....                                         | 116 |

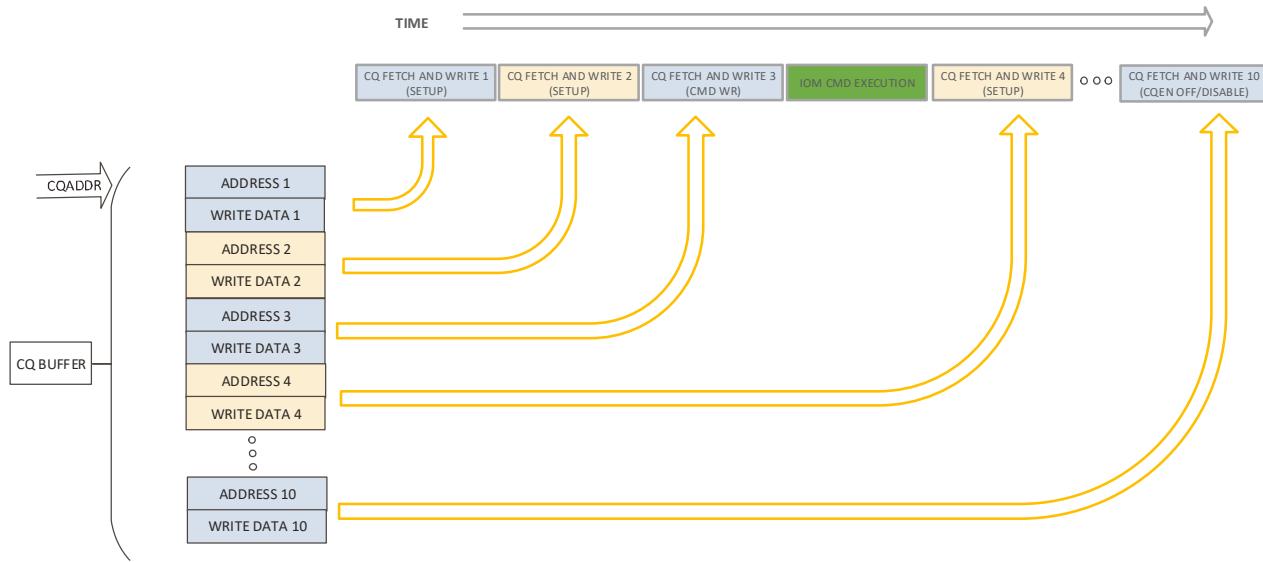

| Figure 34. IOM Pause Example.....                                                   | 117 |

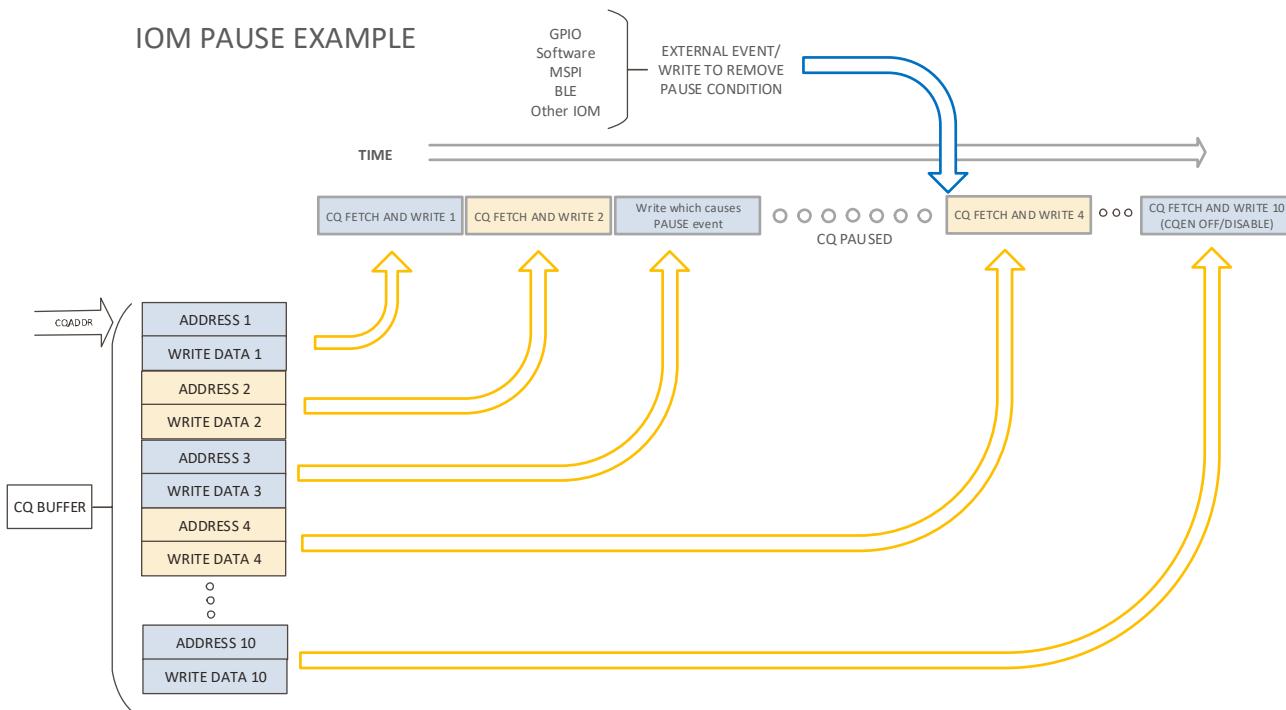

| Figure 35. CQ Pause Bit Fetching .....                                              | 118 |

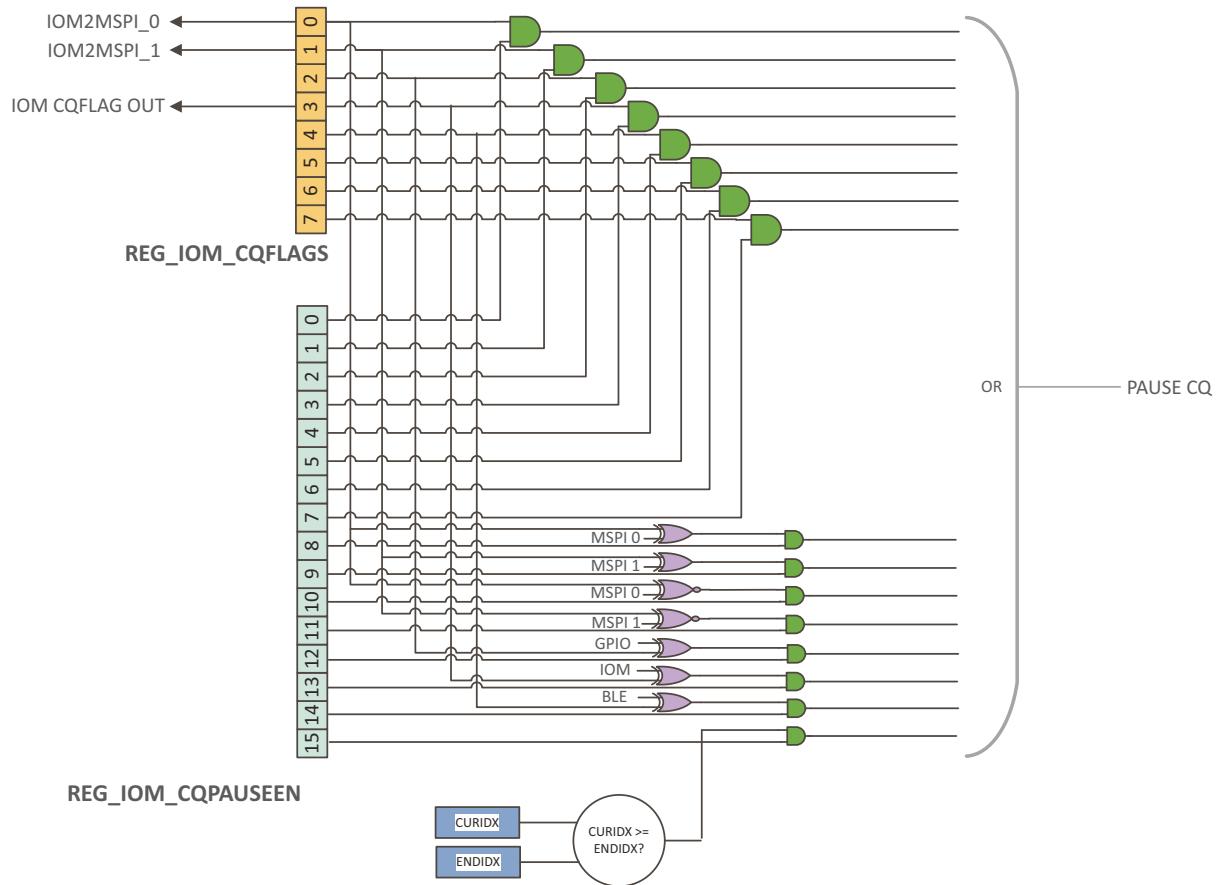

| Figure 36. Block diagram for the I2C/SPI Slave Module.....                          | 120 |

| Figure 37. Block Diagram for the UART Module.....                                   | 122 |

| Figure 38. SDIO Block Diagram.....                                                  | 125 |

| Figure 39. GPU Block Diagram.....                                                   | 127 |

| Figure 40. Blending Modes .....                                                     | 132 |

| Figure 41. TSC™4 /TSC™6 Framebuffer Compression Module.....                         | 133 |

| Figure 42. PDM Instances within Audio Subsystem (4 PDMS Shown).....                 | 142 |

| Figure 43. PDM Block Diagram .....                                                  | 143 |

| Figure 44. Clock Path and Data Synchronization Diagram.....                         | 146 |

| Figure 45. PDM Converter Core Local Clock Gating .....                              | 146 |

| Figure 46. I2S Block Diagram .....                                                  | 150 |

|                                                                                      |     |

|--------------------------------------------------------------------------------------|-----|

| Figure 47. Block diagram for the Voltage Comparator Module.....                      | 152 |

| Figure 48. Block Diagram for Voltage Supplies and Regulation on Apollo4 Family ..... | 154 |

| Figure 49. BGA Package Drawing for Apollo4 Blue Lite SoC.....                        | 156 |

| Figure 50. Reflow Profile.....                                                       | 157 |

| Figure 51. External Components for SIMO Buck.....                                    | 163 |

| Figure 52. External Components for BLE Buck .....                                    | 164 |

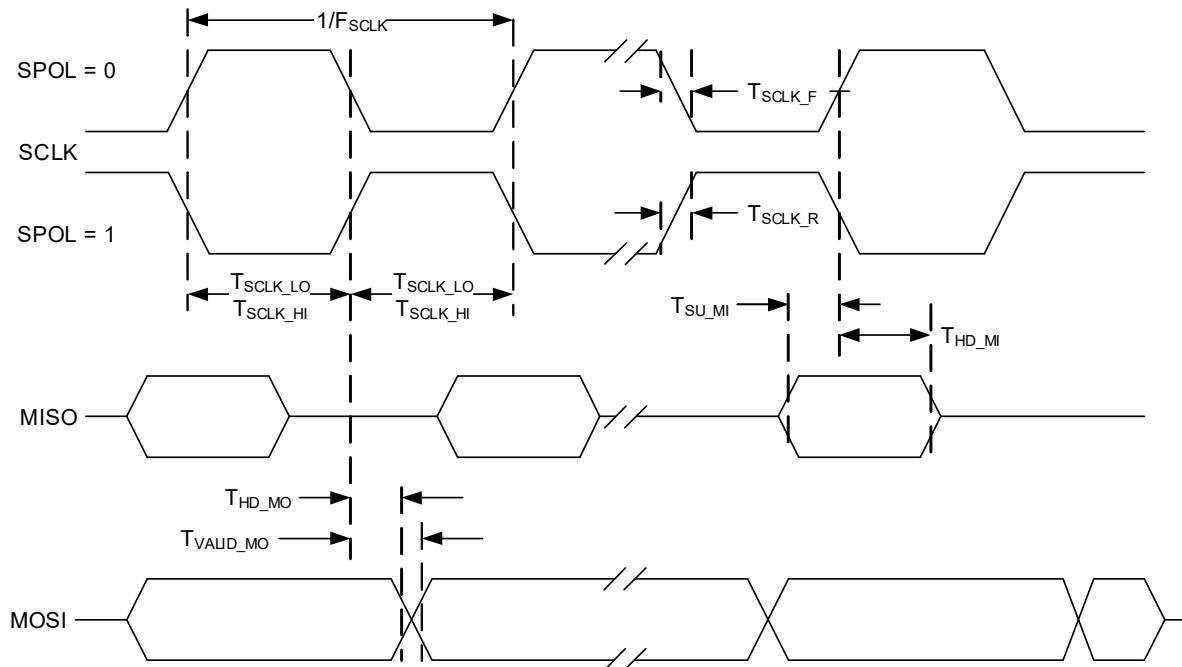

| Figure 53. SPI Master Mode, Phase = 0.....                                           | 181 |

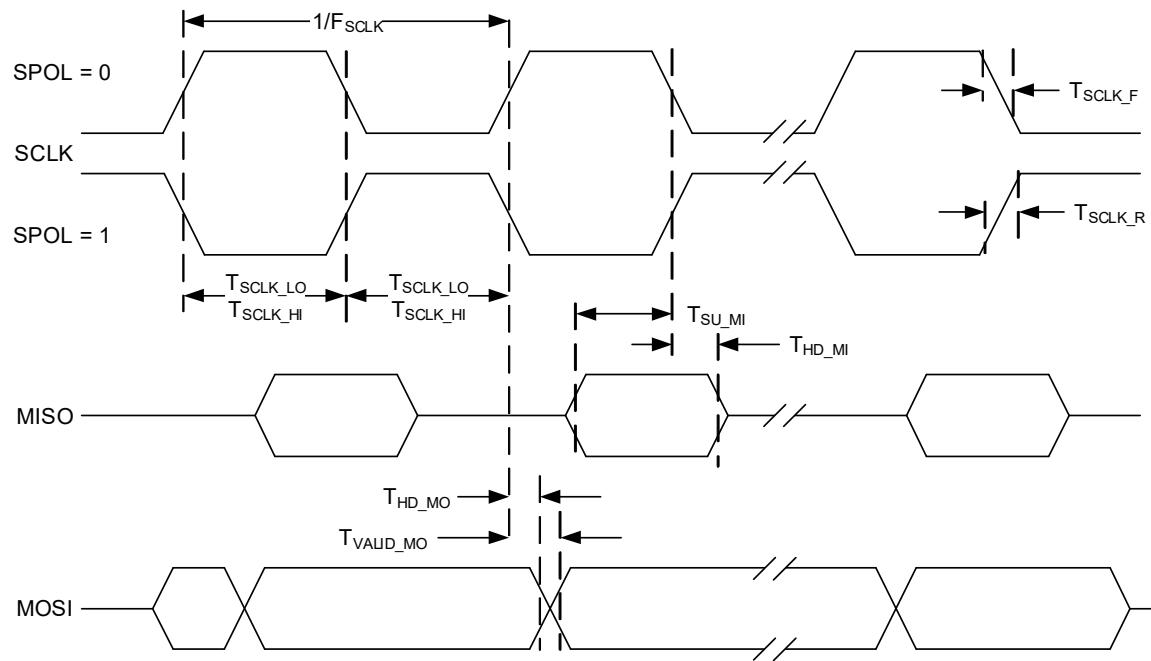

| Figure 54. SPI Master Mode, Phase = 1.....                                           | 182 |

## List of Tables

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

| Table 1: Pin List and Function Table .....                                          | 11  |

| Table 2: Arm Cortex-M4 Memory Map .....                                             | 47  |

| Table 3: Wait States for Accesses to/from the CPU and Memory/Storage Elements ..... | 69  |

| Table 4: I/O Pin Voltage Source .....                                               | 93  |

| Table 5: Apollo4 Blue Lite SoC Pin Mapping (Pg 1) .....                             | 94  |

| Table 6: Apollo4 Blue Lite SoC Pin Mapping (Pg 2) .....                             | 95  |

| Table 7: Pad Function Color Code .....                                              | 96  |

| Table 8: Special Pad Types .....                                                    | 97  |

| Table 9: MSPI0 Pin Muxing (Serial, Dual, Quad, Octal, Hex) .....                    | 104 |

| Table 10: MSPI1 Pin Muxing (Single, Dual, Quad, Octal) .....                        | 105 |

| Table 11: MSPI2 Pin Muxing (Serial, Dual, Quad, Octal) .....                        | 105 |

| Table 12: Required Settings for Typical Configurations .....                        | 107 |

| Table 13: Settings for I2C Clock Speeds .....                                       | 112 |

| Table 14: Blend Factors .....                                                       | 131 |

| Table 15: PDMA_CKO and OSR Settings for Different Sampling Frequencies .....        | 144 |

| Table 16: Reflow Condition (260 °C) for Pb-free Package .....                       | 157 |

| Table 17: Absolute Maximum Ratings .....                                            | 159 |

| Table 18: Voltage Supplies .....                                                    | 160 |

| Table 19: VDDAUDA Noise Spectral Density Specifications to Support XTALHS .....     | 161 |

| Table 20: LDO PSRR Specifications to Support 32 MHz XTALHS .....                    | 161 |

| Table 21: Power Sequence .....                                                      | 162 |

| Table 22: SIMO Buck Converter .....                                                 | 163 |

| Table 23: BLE Buck Converter .....                                                  | 163 |

| Table 24: Recommended Bypass Capacitors for Internal Supplies .....                 | 165 |

| Table 25: Recommended Bypass Capacitors for External Supplies .....                 | 165 |

| Table 26: Current Consumption in Active Mode and Sleep Modes .....                  | 166 |

| Table 27: Bluetooth Low Energy Radio Operating Current .....                        | 167 |

| Table 28: NVM .....                                                                 | 168 |

| Table 29: Power-On Reset (POR) and Brown-Out Detector (BOD) .....                   | 169 |

| Table 30: General Purpose Input/Output (GPIO) .....                                 | 170 |

| Table 31: Primary Internal Clocks .....                                             | 171 |

| Table 32: Low-frequency Crystal .....                                               | 171 |

| Table 33: High-speed Crystal Oscillator .....                                       | 172 |

| Table 34: High-speed External Oscillator .....                                      | 172 |

| Table 35: Real Time Clock (RTC) .....                                               | 173 |

| Table 36: System Timer (STIMER) .....                                               | 174 |

| Table 37: Watchdog Timer (WDT) .....                                                | 175 |

| Table 38: Bluetooth Low Energy Operating Characteristics .....                      | 176 |

| Table 39: Voltage Comparator (VCOMP) .....                                          | 177 |

| Table 40: General Purpose Analog to Digital Converter (ADC) .....                   | 178 |

| Table 41: Multi-bit Serial Peripheral Interface (MSPI) .....                        | 180 |

| Table 42: Serial Peripheral Interface (SPI) Master Interface .....                  | 181 |

| Table 43: Serial Peripheral Interface (SPI) Slave Interface .....                   | 183 |

| Table 44: Universal Asynchronous Receiver/Transmitter (UART) .....                  | 184 |

| Table 45: Secure Digital Input Output (SDIO) .....                                  | 185 |

| Table 46: Ordering Information .....                                                | 186 |

| Table 47: Document Revision List .....                                              | 187 |

## 1. Apollo4 Blue Lite SoC Package Pins

### 1.1 Pin Configuration

Figure 1. Apollo4 Blue Lite SoC BGA Pin Configuration Diagram - Top View

## 1.2 Pin Connections

The following table lists the external pins of the Apollo4 Blue Lite SoC and their available functions.

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                                                         | Pin Type |

|--------------|-----------------|------------------------|-------------------|---------------------------------------------------------------------|----------|

| B5           | -               | -                      | VSSA              | Analog Ground - Same as GNDA                                        | Ground   |

| H1           | -               | -                      | VSSB              | BLE unregulated ground connection                                   | Power    |

| B2           | -               | -                      | VSSP              | Ground Connection for buck regs - Same as GNDP                      | Ground   |

| M1           | -               | -                      | RFIOM             | RF IO negative                                                      | Analog   |

| M2           | -               | -                      | RFIOP             | RF IO positive                                                      | Analog   |

| M3           | -               | -                      | RFSUB             | RF Substrate ground                                                 | Ground   |

| A6           | -               | -                      | RSTN              | External reset input (aka nRST)                                     | Input    |

| A1           | -               | -                      | SIMOBUCK_SW       | SIMO Buck converter inductor switch output                          | Power    |

| A2           | -               | -                      | SIMOBUCK_SWSEL    | SIMO Buck converter inductor switch input                           | Power    |

| K1           | -               | -                      | TXEN              | Transmitter enable                                                  | Output   |

| C4           | -               | -                      | VDDA              | Analog voltage supply                                               | Power    |

| B11          | -               | -                      | VDDAUDA           | Analog Audio Voltage supply                                         | Power    |

| E11          | -               | -                      | VDDAUDD           | Digital Audio Voltage supply                                        | Power    |

| G1           | -               | -                      | VDDB              | BLE voltage supply (VCC)                                            | Power    |

| G12          | -               | -                      | VDBBH             | BLE Buck converter VOUT                                             | Power    |

| J1           | -               | -                      | VDBBH_RF          | BLE Buck converter RF VOUT                                          | Power    |

| H12          | -               | -                      | VDBBH_SW          | BLE Buck converter inductor switch                                  | Power    |

| A3           | -               | -                      | VDDC              | Core Buck converter VOUT                                            | Power    |

| B3           | -               | -                      | VDDC_LV           | Core_LV Buck converter VOUT                                         | Power    |

| C2           | -               | -                      | VDDF              | Mem Buck converter VOUT                                             | Power    |

| M10          | -               | -                      | VDDH              | High voltage domain power supply                                    | Power    |

| M9           | -               | -                      | VDDH2             | High voltage domain2 power supply                                   | Power    |

| B1           | -               | -                      | VDDP              | VDD supply to I/O pads (Core)                                       | Power    |

| C1           | -               | -                      | VDDS              | SRAM high voltage supply                                            | Power    |

| D2           | -               | -                      | VSS               | Digital Ground for VDDF and PADS (Noisy) - (Previously called GNDD) | Ground   |

| B12          | -               | -                      | VSSAUDA           | Analog Audio Ground                                                 | Ground   |

| E12          | -               | -                      | VSSAUDD           | Digital Audio Ground                                                | Ground   |

| L2           | -               | -                      | VSSS              | HVSIMOBUCK Ground                                                   | Ground   |

| L1           | -               | -                      | VSSVCO            | BLECORE Signals - Ground for VCO                                    | Ground   |

| A4           | -               | -                      | XI                | 32.768kHz crystal input                                             | XT       |

| C12          | -               | -                      | XI32M             | 32MHz crystal input                                                 | XT24M    |

| A5           | -               | -                      | XO                | 32.768kHz crystal output                                            | XT       |

| D12          | -               | -                      | XO32M             | 32MHz crystal output                                                | XT24M    |

Table 1: Pin List and Function Table

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                                | Pin Type                 |

|--------------|-----------------|------------------------|-------------------|--------------------------------------------|--------------------------|

| H3           | 0               | 0                      | SWTRACECLK        | Serial Wire Debug Trace Clock              | Output                   |

|              |                 | 1                      | SLSCL             | I2C Slave clock                            | Input                    |

|              |                 | 2                      | SLSCK             | SPI Slave clock                            | Input                    |

|              |                 | 3                      | GPIO00            | General purpose I/O                        | I/O                      |

|              |                 | 4                      | UART0TX           | UART0 transmit output                      | Output                   |

|              |                 | 5                      | UART1TX           | UART1 transmit output                      | Output                   |

|              |                 | 6                      | CT0               | Timer/counter 0                            | Output                   |

|              |                 | 7                      | NCE0              | IOMSTR N Chip Select 0                     | Output                   |

|              |                 | 9                      | VCMPO             | Output of the voltage comparator signal    | -                        |

|              |                 | 10                     | -                 | -                                          | -                        |

|              |                 | 11                     | FPIO00            | Fast PIO                                   | -                        |

| J4           | 1               | 0                      | SWTRACE0          | Serial Wire Debug Trace Output 0           | Output                   |

|              |                 | 1                      | SLSDAWIR3         | I2C Slave I/O data (I2C) 3 Wire Data (SPI) | Bidirectional Open Drain |

|              |                 | 2                      | SLMOSI            | SPI Slave input data                       | Input                    |

|              |                 | 3                      | GPIO01            | General purpose I/O                        | I/O                      |

|              |                 | 4                      | UART2TX           | UART2 transmit output                      | Output                   |

|              |                 | 5                      | UART3TX           | UART3 transmit output                      | Output                   |

|              |                 | 6                      | CT1               | Timer/counter 1                            | Output                   |

|              |                 | 7                      | NCE1              | IOMSTR N Chip Select 1                     | Output                   |

|              |                 | 9                      | VCMPO             | Output of the voltage comparator signal    | -                        |

|              |                 | 10                     | -                 | -                                          | -                        |

|              |                 | 11                     | FPIO01            | Fast PIO                                   | -                        |

| K4           | 2               | 0                      | SWTRACE1          | Serial Wire Debug Trace Output 1           | Output                   |

|              |                 | 1                      | SLMISO            | SPI Slave output data                      | Output                   |

|              |                 | 2                      | TRIG1             | ADC trigger input                          | Input                    |

|              |                 | 3                      | GPIO02            | General purpose I/O                        | I/O                      |

|              |                 | 4                      | UART0RX           | UART0 receive input                        | Input                    |

|              |                 | 5                      | UART1RX           | UART1 receive input                        | Input                    |

|              |                 | 6                      | CT2               | Timer/counter 2                            | Output                   |

|              |                 | 7                      | NCE2              | IOMSTR N Chip Select 2                     | Output                   |

|              |                 | 9                      | VCMPO             | Output of the voltage comparator signal    | -                        |

|              |                 | 10                     | -                 | -                                          | -                        |

|              |                 | 11                     | FPIO02            | Fast PIO                                   | -                        |

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                                   | Pin Type                 |

|--------------|-----------------|------------------------|-------------------|-----------------------------------------------|--------------------------|

| L4           | 3               | 0                      | SWTRACE2          | Serial Wire Debug Trace Output 2              | Output                   |

|              |                 | 1                      | SLnCE             | SPI Slave chip enable                         | Input                    |

|              |                 | 2                      | SWO               | Serial Wire Debug                             | Output                   |

|              |                 | 3                      | GPIO03            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART2RX           | UART2 receive input                           | Input                    |

|              |                 | 5                      | UART3RX           | UART3 receive input                           | Input                    |

|              |                 | 6                      | CT3               | Timer/counter 3                               | Output                   |

|              |                 | 7                      | NCE3              | IOMSTR N Chip Select 3                        | Output                   |

|              |                 | 9                      | -                 | -                                             | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO03            | Fast PIO                                      | -                        |

| H4           | 5               | 0                      | M0SCL             | I2C Master 0 clock                            | Open Drain Output        |

|              |                 | 1                      | M0SCK             | SPI Master 0 clock                            | Output                   |

|              |                 | 2                      | I2S0_CLK          | I2S0 Bit clock                                | Input                    |

|              |                 | 3                      | GPIO05            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART2RTS          | UART2 Request to Send (RTS)                   | Output                   |

|              |                 | 5                      | UART3RTS          | UART3 Request to Send (RTS)                   | Output                   |

|              |                 | 6                      | CT5               | Timer/counter 5                               | Output                   |

|              |                 | 7                      | NCE5              | IOMSTR N Chip Select 5                        | Output                   |

|              |                 | 9                      | -                 | -                                             | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO05            | Fast PIO                                      | -                        |

| J5           | 6               | 0                      | M0SDAWIR3         | I2C Master 0 I/O data (I2C) 3 Wire data (SPI) | Bidirectional Open Drain |

|              |                 | 1                      | M0MOSI            | SPI Master 0 output data                      | Output                   |

|              |                 | 2                      | I2S0_DATA         | I2S0 Data                                     | Bidirectional            |

|              |                 | 3                      | GPIO06            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART0CTS          | UART0 Clear to Send (CTS)                     | Input                    |

|              |                 | 5                      | UART1CTS          | UART1 Clear to Send (CTS) input               | Input                    |

|              |                 | 6                      | CT6               | Timer/counter 6                               | Output                   |

|              |                 | 7                      | NCE6              | IOMSTR N Chip Select 6                        | Output                   |

|              |                 | 9                      | I2S0_SDOUT        | I2S0 Data output                              | Output                   |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO06            | Fast PIO                                      | -                        |

Table 1: Pin List and Function Table

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                                   | Pin Type                 |

|--------------|-----------------|------------------------|-------------------|-----------------------------------------------|--------------------------|

| J6           | 7               | 0                      | M0MISO            | SPI Master 0 input data                       | Input                    |

|              |                 | 1                      | TRIG0             | ADC trigger input                             | Input                    |

|              |                 | 2                      | I2S0_WS           | I2S0 L/R clock                                | Input                    |

|              |                 | 3                      | GPIO07            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART2CTS          | UART2 Clear to Send (CTS) input               | Input                    |

|              |                 | 5                      | UART3CTS          | UART3 Clear to Send (CTS) input               | Input                    |

|              |                 | 6                      | CT7               | Timer/counter 7                               | Output                   |

|              |                 | 7                      | NCE7              | IOMSTR/MSPI N Chip Select 7                   | Output                   |

|              |                 | 9                      | -                 | -                                             | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO07            | Fast PIO                                      | -                        |

| E8           | 8               | 0                      | CMPRF1            | Comparator reference 1                        | Input                    |

|              |                 | 1                      | TRIG1             | ADC trigger input                             | Input                    |

|              |                 | 2                      | -                 | -                                             | -                        |

|              |                 | 3                      | GPIO08            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | M1SCL             | I2C Master 1 clock                            | Open Drain Output        |

|              |                 | 5                      | M1SCK             | SPI Master 1 clock                            | Output                   |

|              |                 | 6                      | CT8               | Timer/counter 8                               | Output                   |

|              |                 | 7                      | NCE8              | IOMSTR N Chip Select 8                        | Output                   |

|              |                 | 9                      | -                 | -                                             | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO08            | Fast PIO                                      | -                        |

| E7           | 9               | 0                      | CMPRF0            | Comparator reference 0                        | Input                    |

|              |                 | 1                      | TRIG2             | ADC trigger input                             | Input                    |

|              |                 | 2                      | -                 | -                                             | -                        |

|              |                 | 3                      | GPIO09            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | M1SDAWIR3         | I2C Master 1 I/O data (I2C) 3 Wire data (SPI) | Bidirectional Open Drain |

|              |                 | 5                      | M1MOSI            | SPI Master 1 output data                      | Output                   |

|              |                 | 6                      | CT9               | Timer/counter 9                               | Output                   |

|              |                 | 7                      | NCE9              | IOMSTR N Chip Select 9                        | Output                   |

|              |                 | 9                      | -                 | -                                             | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO09            | Fast PIO                                      | -                        |

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                        | Pin Type      |

|--------------|-----------------|------------------------|-------------------|------------------------------------|---------------|

| E6           | 10              | 0                      | CMPIN0            | Voltage comparator input 0         | Input         |

|              |                 | 1                      | TRIG3             | ADC trigger input                  | Input         |

|              |                 | 2                      | -                 | -                                  | -             |

|              |                 | 3                      | GPIO10            | General purpose I/O                | I/O           |

|              |                 | 4                      | M1MISO            | SPI Master 1 input data            | Input         |

|              |                 | 5                      | -                 | -                                  | -             |

|              |                 | 6                      | CT10              | Timer/counter 10                   | Output        |

|              |                 | 7                      | NCE10             | IOMSTR N Chip Select 10            | Output        |

|              |                 | 9                      | -                 | -                                  | -             |

|              |                 | 10                     | -                 | -                                  | -             |

|              |                 | 11                     | FPIO10            | Fast PIO                           | -             |

| E4           | 11              | 0                      | CMPIN1            | Voltage comparator input 1         | Input         |

|              |                 | 1                      | TRIG0             | ADC trigger input                  | Input         |

|              |                 | 2                      | I2S0_CLK          | I2S0 Bit clock                     | Input         |

|              |                 | 3                      | GPIO11            | General purpose I/O                | I/O           |

|              |                 | 4                      | UART2RX           | UART2 receive input                | Input         |

|              |                 | 5                      | UART3RX           | UART3 receive input                | Input         |

|              |                 | 6                      | CT11              | Timer/counter 11                   | Output        |

|              |                 | 7                      | NCE11             | IOMSTR N Chip Select 11            | Output        |

|              |                 | 9                      | -                 | -                                  | -             |

|              |                 | 10                     | -                 | -                                  | -             |

|              |                 | 11                     | FPIO11            | Fast PIO                           | -             |

| B4           | 12              | 0                      | ADCSE7            | Analog to Digital Converter SE IN7 | Input         |

|              |                 | 1                      | TRIG1             | ADC trigger input                  | Input         |

|              |                 | 2                      | I2S0_DATA         | I2S0 Data                          | Bidirectional |

|              |                 | 3                      | GPIO12            | General purpose I/O                | I/O           |

|              |                 | 4                      | UART0TX           | UART0 transmit output              | Output        |

|              |                 | 5                      | UART1TX           | UART1 transmit output              | Output        |

|              |                 | 6                      | CT12              | Timer/counter 12                   | Output        |

|              |                 | 7                      | NCE12             | IOMSTR N Chip Select 12            | Output        |

|              |                 | 9                      | CMPRF2            | Comparator reference 2             | Input         |

|              |                 | 10                     | I2S0_SDOUT        | I2S0 Data output                   | Output        |

|              |                 | 11                     | FPIO12            | Fast PIO                           | -             |

Table 1: Pin List and Function Table

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                        | Pin Type |

|--------------|-----------------|------------------------|-------------------|------------------------------------|----------|

| D5           | 13              | 0                      | ADCSE6            | Analog to Digital Converter SE IN6 | Input    |

|              |                 | 1                      | TRIG2             | ADC trigger input                  | Input    |

|              |                 | 2                      | I2S0_WS           | I2S0 L/R clock                     | Input    |

|              |                 | 3                      | GPIO13            | General purpose I/O                | I/O      |

|              |                 | 4                      | UART2TX           | UART2 transmit output              | Output   |

|              |                 | 5                      | UART3TX           | UART3 transmit output              | Output   |

|              |                 | 6                      | CT13              | Timer/counter 13                   | Output   |

|              |                 | 7                      | NCE13             | IOMSTR N Chip Select 13            | Output   |

|              |                 | 9                      | -                 | -                                  | -        |

|              |                 | 10                     | -                 | -                                  | -        |

|              |                 | 11                     | FPIO13            | Fast PIO                           | -        |

| D6           | 14              | 0                      | ADCSE5            | Analog to Digital Converter SE IN5 | Input    |

|              |                 | 1                      | TRIG3             | ADC trigger input                  | Input    |

|              |                 | 2                      | -                 | -                                  | -        |

|              |                 | 3                      | GPIO14            | General purpose I/O                | I/O      |

|              |                 | 4                      | -                 | -                                  | -        |

|              |                 | 5                      | UART1RX           | UART1 receive input                | Input    |

|              |                 | 6                      | CT14              | Timer/counter 14                   | Output   |

|              |                 | 7                      | NCE14             | IOMSTR/MSPI N Chip Select 14       | Output   |

|              |                 | 9                      | -                 | -                                  | -        |

|              |                 | 10                     | I2S0_SDIN         | I2S0 Data input                    | Input    |

|              |                 | 11                     | FPIO14            | Fast PIO                           | -        |

| E5           | 15              | 0                      | ADCSE4            | Analog to Digital Converter SE IN4 | Input    |

|              |                 | 1                      | TRIGO             | ADC trigger input                  | Input    |

|              |                 | 2                      | -                 | -                                  | -        |

|              |                 | 3                      | GPIO15            | General purpose I/O                | I/O      |

|              |                 | 4                      | -                 | -                                  | -        |

|              |                 | 5                      | UART3RX           | UART3 receive input                | Input    |

|              |                 | 6                      | CT15              | Timer/counter 15                   | Output   |

|              |                 | 7                      | NCE15             | IOMSTR N Chip Select 15            | Output   |

|              |                 | 9                      | -                 | -                                  | -        |

|              |                 | 10                     | REFCLK_EXT        | External Reference Clock           | Input    |

|              |                 | 11                     | FPIO15            | Fast PIO                           | -        |

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                        | Pin Type |

|--------------|-----------------|------------------------|-------------------|------------------------------------|----------|

| D7           | 16              | 0                      | ADCSE3            | Analog to Digital Converter SE IN3 | Input    |

|              |                 | 1                      | TRIG1             | ADC trigger input                  | Input    |

|              |                 | 2                      | -                 | -                                  | -        |

|              |                 | 3                      | GPIO16            | General purpose I/O                | I/O      |

|              |                 | 4                      | -                 | -                                  | -        |

|              |                 | 5                      | UART1RTS          | UART1 Request to Send (RTS)        | Output   |

|              |                 | 6                      | CT16              | Timer/counter 16                   | Output   |

|              |                 | 7                      | NCE16             | IOMSTR N Chip Select 16            | Output   |

|              |                 | 9                      | -                 | -                                  | -        |

|              |                 | 10                     | -                 | -                                  | -        |

|              |                 | 11                     | FPIO16            | Fast PIO                           | -        |

| D4           | 17              | 0                      | ADCSE2            | Analog to Digital Converter SE IN2 | Input    |

|              |                 | 1                      | TRIG2             | ADC trigger input                  | Input    |

|              |                 | 2                      | -                 | -                                  | -        |

|              |                 | 3                      | GPIO17            | General purpose I/O                | I/O      |

|              |                 | 4                      | -                 | -                                  | -        |

|              |                 | 5                      | UART3RTS          | UART3 Request to Send (RTS)        | Output   |

|              |                 | 6                      | CT17              | Timer/counter 17                   | Output   |

|              |                 | 7                      | NCE17             | IOMSTR N Chip Select 17            | Output   |

|              |                 | 9                      | -                 | -                                  | -        |

|              |                 | 10                     | -                 | -                                  | -        |

|              |                 | 11                     | FPIO17            | Fast PIO                           | -        |

| D3           | 18              | 0                      | ADCSE1            | Analog to Digital Converter SE IN1 | Input    |

|              |                 | 1                      | -                 | -                                  | -        |

|              |                 | 2                      | -                 | -                                  | -        |

|              |                 | 3                      | GPIO18            | General purpose I/O                | I/O      |

|              |                 | 4                      | UART0CTS          | UART0 Clear to Send (CTS)          | Input    |

|              |                 | 5                      | UART1CTS          | UART1 Clear to Send (CTS) input    | Input    |

|              |                 | 6                      | CT18              | Timer/counter 18                   | Output   |

|              |                 | 7                      | NCE18             | IOMSTR N Chip Select 18            | Output   |

|              |                 | 9                      | -                 | -                                  | -        |

|              |                 | 10                     | -                 | -                                  | -        |

|              |                 | 11                     | FPIO18            | Fast PIO                           | -        |

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                        | Pin Type              |

|--------------|-----------------|------------------------|-------------------|------------------------------------|-----------------------|

| C3           | 19              | 0                      | ADCSE0            | Analog to Digital Converter SE IN0 | Input                 |

|              |                 | 1                      | -                 | -                                  | -                     |

|              |                 | 2                      | -                 | -                                  | -                     |

|              |                 | 3                      | GPIO19            | General purpose I/O                | I/O                   |

|              |                 | 4                      | UART2CTS          | UART2 Clear to Send (CTS) input    | Input                 |

|              |                 | 5                      | UART3CTS          | UART3 Clear to Send (CTS) input    | Input                 |

|              |                 | 6                      | CT19              | Timer/counter 19                   | Output                |

|              |                 | 7                      | NCE19             | IOMSTR N Chip Select 19            | Output                |

|              |                 | 9                      | -                 | -                                  | -                     |

|              |                 | 10                     | -                 | -                                  | -                     |

|              |                 | 11                     | FPIO19            | Fast PIO                           | -                     |

| K3           | 20              | 0                      | SWDCK             | Software debug clock Input         | Input                 |

|              |                 | 1                      | TRIG1             | ADC trigger input                  | Input                 |

|              |                 | 2                      | -                 | -                                  | -                     |

|              |                 | 3                      | GPIO20            | General purpose I/O                | I/O                   |

|              |                 | 4                      | UART0TX           | UART0 transmit output              | Output                |

|              |                 | 5                      | UART1TX           | UART1 transmit output              | Output                |

|              |                 | 6                      | CT20              | Timer/counter 20                   | Output                |

|              |                 | 7                      | NCE20             | IOMSTR N Chip Select 20            | Output                |

|              |                 | 9                      | -                 | -                                  | -                     |

|              |                 | 10                     | -                 | -                                  | -                     |

|              |                 | 11                     | FPIO20            | Fast PIO                           | -                     |

| J3           | 21              | 0                      | SWDIO             | Software data I/O                  | Bidirectional 3-state |

|              |                 | 1                      | TRIG2             | ADC trigger input                  | Input                 |

|              |                 | 2                      | -                 | -                                  | -                     |

|              |                 | 3                      | GPIO21            | General purpose I/O                | I/O                   |

|              |                 | 4                      | UART2TX           | UART2 transmit output              | Output                |

|              |                 | 5                      | UART3TX           | UART3 transmit output              | Output                |

|              |                 | 6                      | CT21              | Timer/counter 21                   | Output                |

|              |                 | 7                      | NCE21             | IOMSTR N Chip Select 21            | Output                |

|              |                 | 9                      | -                 | -                                  | -                     |

|              |                 | 10                     | -                 | -                                  | -                     |

|              |                 | 11                     | FPIO21            | Fast PIO                           | -                     |

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                                   | Pin Type                 |

|--------------|-----------------|------------------------|-------------------|-----------------------------------------------|--------------------------|

| F3           | 22              | 0                      | M7SCL             | I2C Master 7 Clk                              | Bidirectional Open Drain |

|              |                 | 1                      | M7SCK             | SPI Master 7 Clk                              | Output                   |

|              |                 | 2                      | SWO               | Serial Wire Debug                             | Output                   |

|              |                 | 3                      | GPIO22            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART0RX           | UART0 receive input                           | Input                    |

|              |                 | 5                      | UART1RX           | UART1 receive input                           | Input                    |

|              |                 | 6                      | CT22              | Timer/counter 22                              | Output                   |

|              |                 | 7                      | NCE22             | IOMSTR N Chip Select 22                       | Output                   |

|              |                 | 9                      | VCMPO             | Output of the voltage comparator signal       | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO22            | Fast PIO                                      | -                        |

| F2           | 23              | 0                      | M7SDAWIR3         | I2C Master 7 I/O data (I2C) 3 Wire data (SPI) | Bidirectional Open Drain |

|              |                 | 1                      | M7MOSI            | SPI Master 7 data out                         | Output                   |

|              |                 | 2                      | SWO               | Serial Wire Debug                             | Output                   |

|              |                 | 3                      | GPIO23            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART2RX           | UART2 receive input                           | Input                    |

|              |                 | 5                      | UART3RX           | UART3 receive input                           | Input                    |

|              |                 | 6                      | CT23              | Timer/counter 23                              | Output                   |

|              |                 | 7                      | NCE23             | IOMSTR N Chip Select 23                       | Output                   |

|              |                 | 9                      | VCMPO             | Output of the voltage comparator signal       | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO23            | Fast PIO                                      | -                        |

| E2           | 24              | 0                      | M7MISO            | SPI Master 7 data in                          | Input                    |

|              |                 | 1                      | TRIG3             | ADC trigger input                             | Input                    |

|              |                 | 2                      | SWO               | Serial Wire Debug                             | Output                   |

|              |                 | 3                      | GPIO24            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | UART0RTS          | UART0 Request to Send (RTS)                   | Output                   |

|              |                 | 5                      | UART1RTS          | UART1 Request to Send (RTS)                   | Output                   |

|              |                 | 6                      | CT24              | Timer/counter 24                              | Output                   |

|              |                 | 7                      | NCE24             | IOMSTR/MSPI N Chip Select 24                  | Output                   |

|              |                 | 9                      | -                 | -                                             | -                        |

|              |                 | 10                     | -                 | -                                             | -                        |

|              |                 | 11                     | FPIO24            | Fast PIO                                      | -                        |

**Table 1: Pin List and Function Table**

| Blue BGA Pin | GPIO Pad Number | Function Select Number | Pad Function Name | Description                                   | Pin Type                 |

|--------------|-----------------|------------------------|-------------------|-----------------------------------------------|--------------------------|

| K5           | 25              | 0                      | M2SCL             | I2C Master 2 clock                            | Open Drain Output        |

|              |                 | 1                      | M2SCK             | SPI Master 2 clock                            | Output                   |

|              |                 | 2                      | -                 | -                                             | -                        |

|              |                 | 3                      | GPIO25            | General purpose I/O                           | I/O                      |

|              |                 | 4                      | -                 | -                                             | -                        |

|              |                 | 5                      | UART1TX           | UART1 transmit output                         | Output                   |

|              |                 | 6                      | CT25              | Timer/counter 25                              | Output                   |