# S32K344

## White Board

Rev. 1.0 — 11 April 2023

User manual

COMPANY PUBLIC

Table 1. Revision history

| Revision Number | Date                         | Changes                                                                                                                   |

|-----------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Draft 0.6       | Dec 2 <sup>nd</sup> , 2020   | Initial Version                                                                                                           |

| Draft 0.7       | Jan 6 <sup>th</sup> , 2021   | Added J86, J87, J88, J89, J90 and SBC debug description based on SCH-47478 rev B.                                         |

| Draft 0.8       | Feb 1 <sup>st</sup> , 2021   | Updated the new board picture of rev B PCB.<br>Added power on requirement.<br>Added a few new jumpers and a power switch. |

| Draft 0.9       | Mar 18 <sup>th</sup> , 2021  | Updated some detailed descriptions of key features.                                                                       |

| 1.0             | April 7 <sup>th</sup> , 2023 | Updated the new BD, deleted the FS26 power up note.                                                                       |

## 1 Introduction

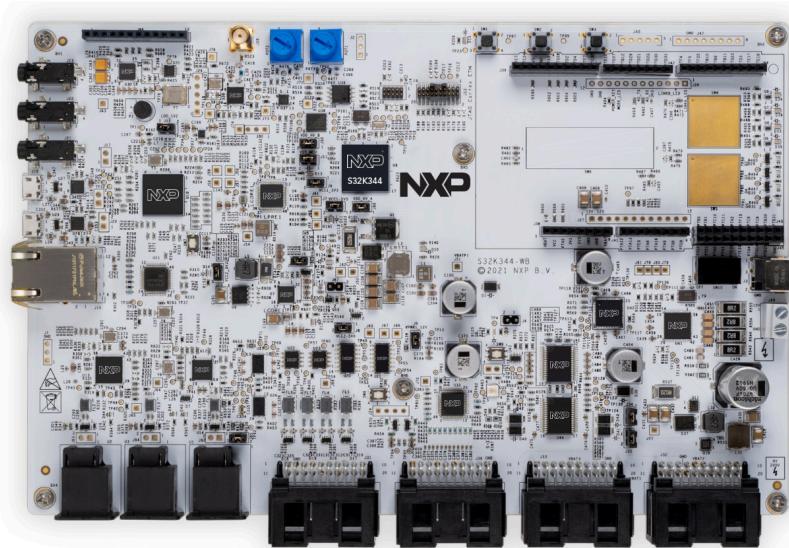

This document introduces the key features of S32K344 White Board, which can be used for various applications evaluation, including Domain Controller, BCM, Gateway, T-box and so on. The block diagram for S32K344 White Board is shown in below [Figure 1 "S32K344 White Board block diagram".](#)

This document illustrates the power supply architecture of the White Board. It also lists the jumpers configuration, connectors/interfaces, and some MCU PINs assignment on the board.

Users can read this manual together with the White Board schematics to better understand the hardware design.

Figure 1. S32K344 White Board block diagram

## 2 Features overview

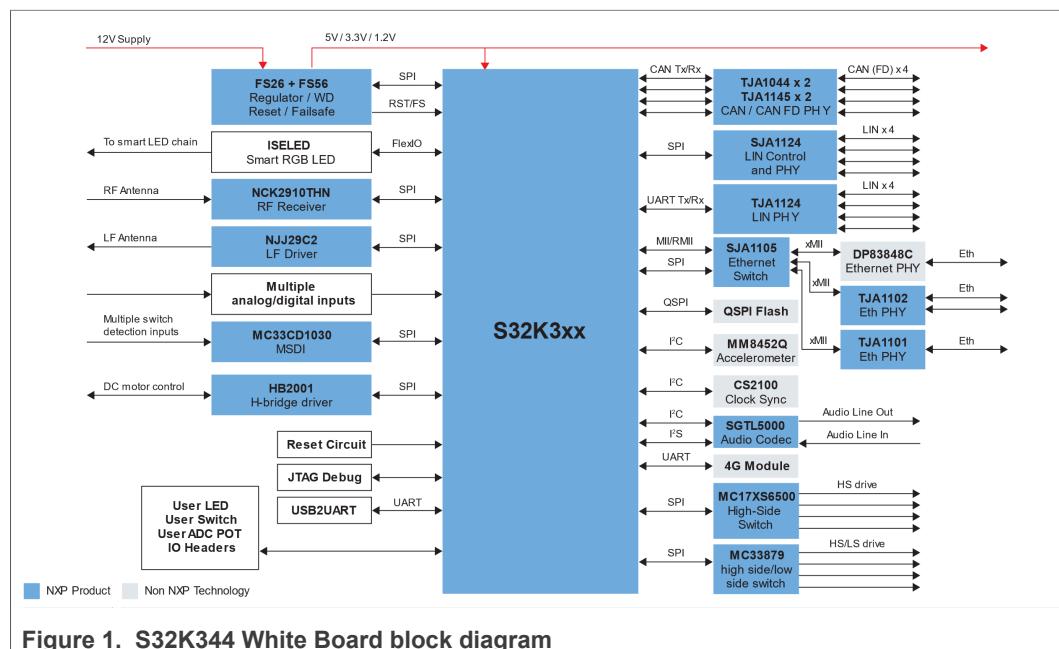

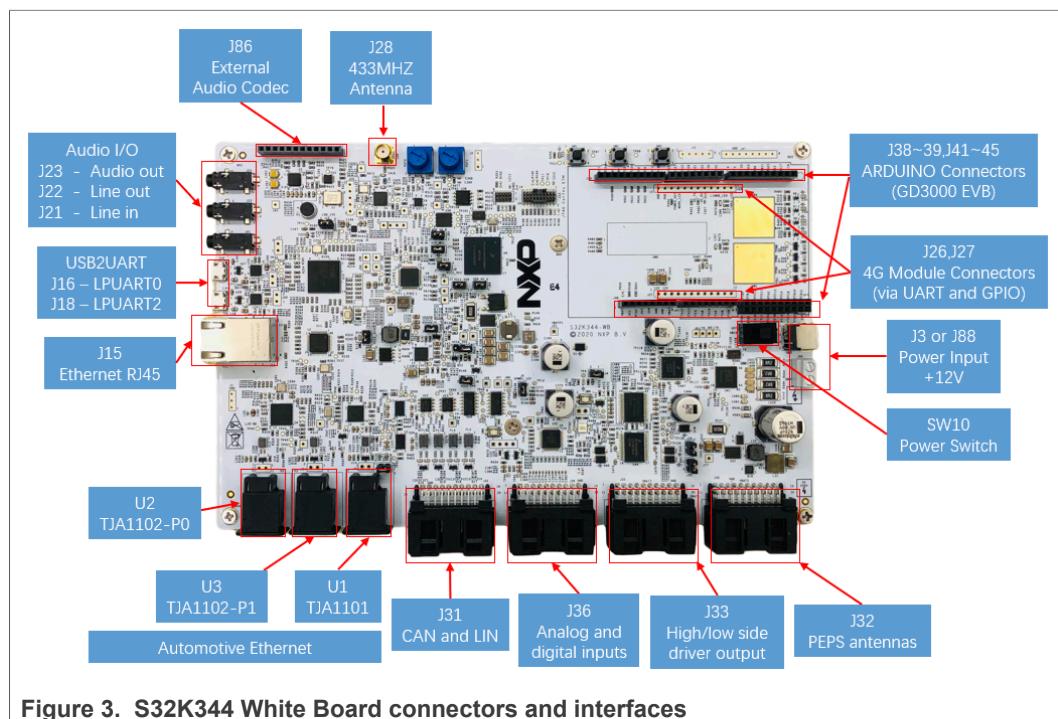

The following figure shows the features of S32K344 White Board. Key features include the following:

Figure 2. S32K344 White Board features overview

- S32K344 BGA257 secured sample.

- Safety SBC FS26 supplies MCU with 5V, 3.3V, 1.5V and monitors MCU status.

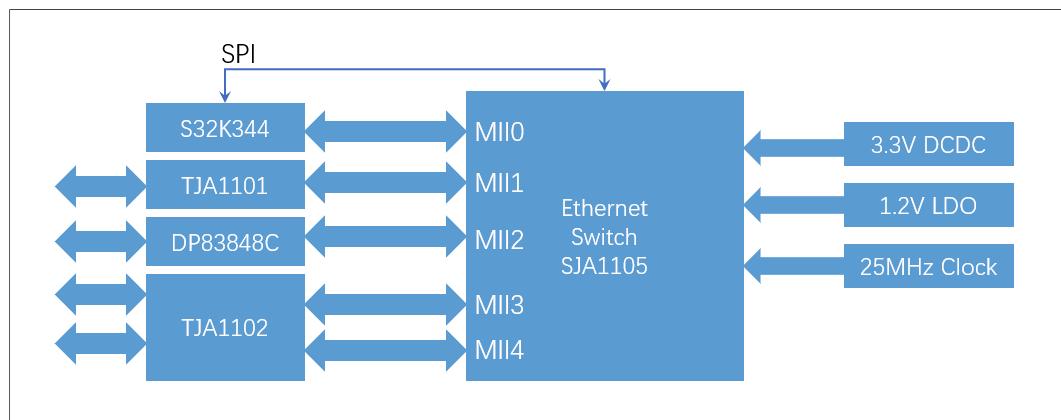

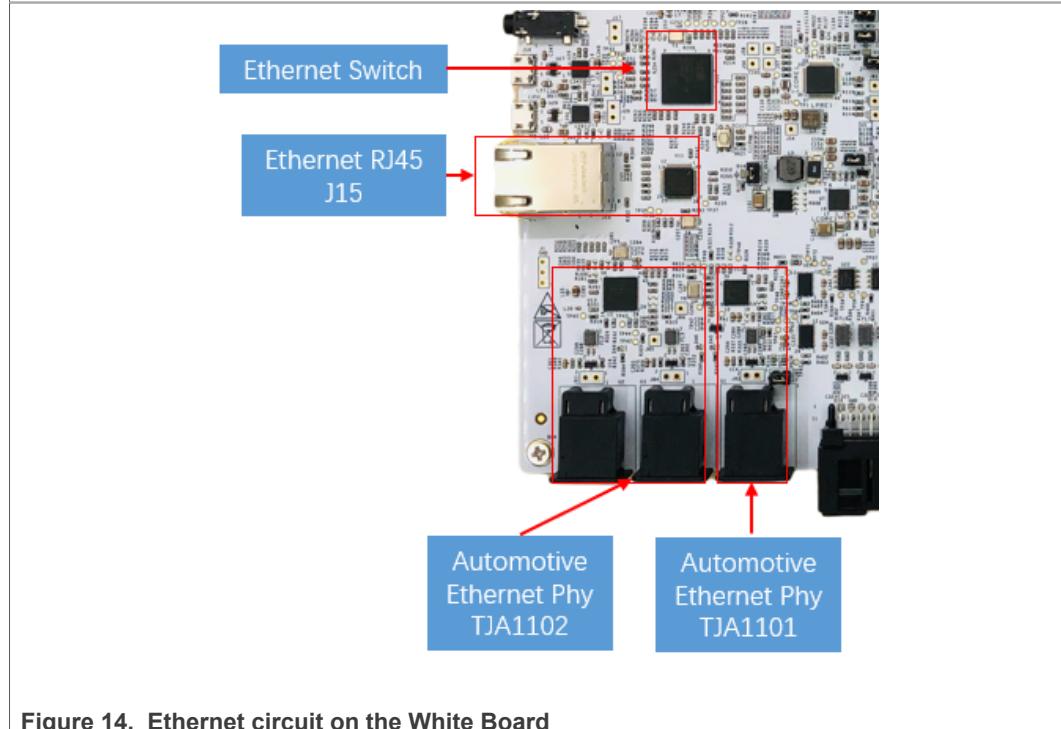

- Ethernet switch SJA1105 and Ethernet phy TJA1101/TJA1102/DP83848C provide 3 channels of automotive ethernet (100BASE-T1) and 1 channel of industrial ethernet (100BASE-TX).

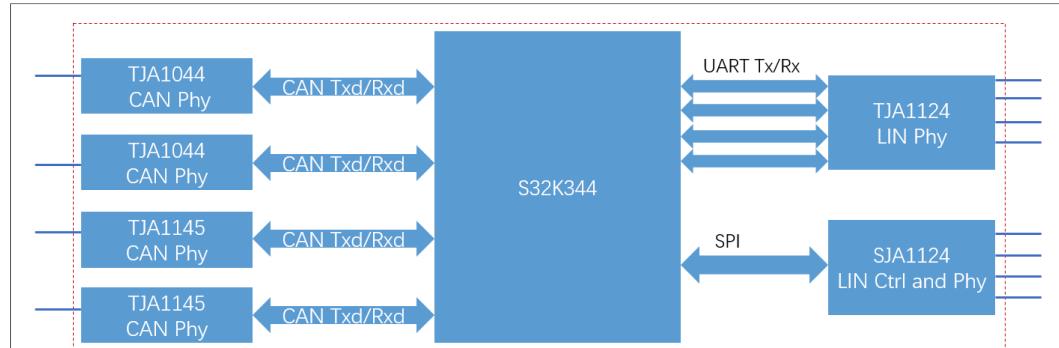

- CAN/CANFD transceivers TJA1044 and TJA1145 provide 4 channels CAN/CANFD.

- LIN controller SJA1124 and LIN transceiver TJA1124 provide 8 channels of LIN.

- QSPI Flash 128Mb.

- I2C FRAM (fast EEPROM) 256 Kb.

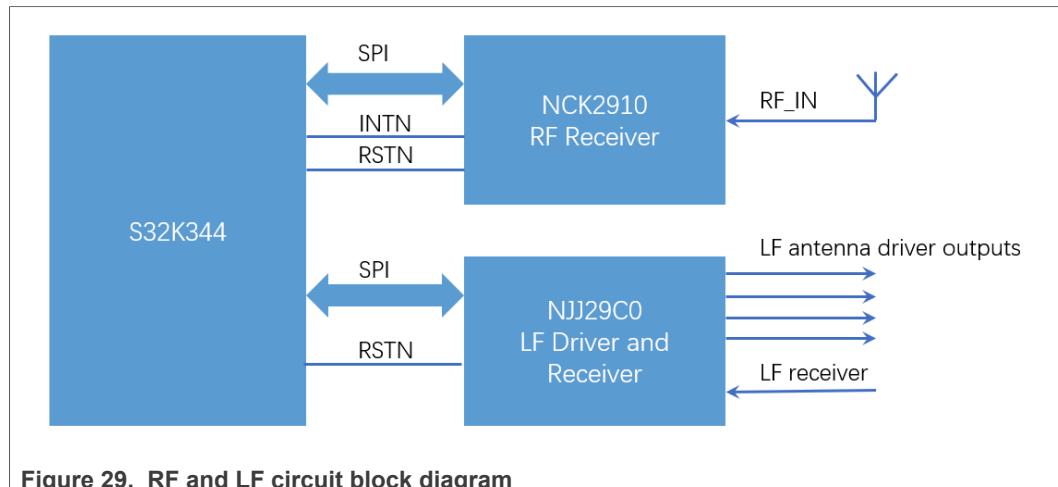

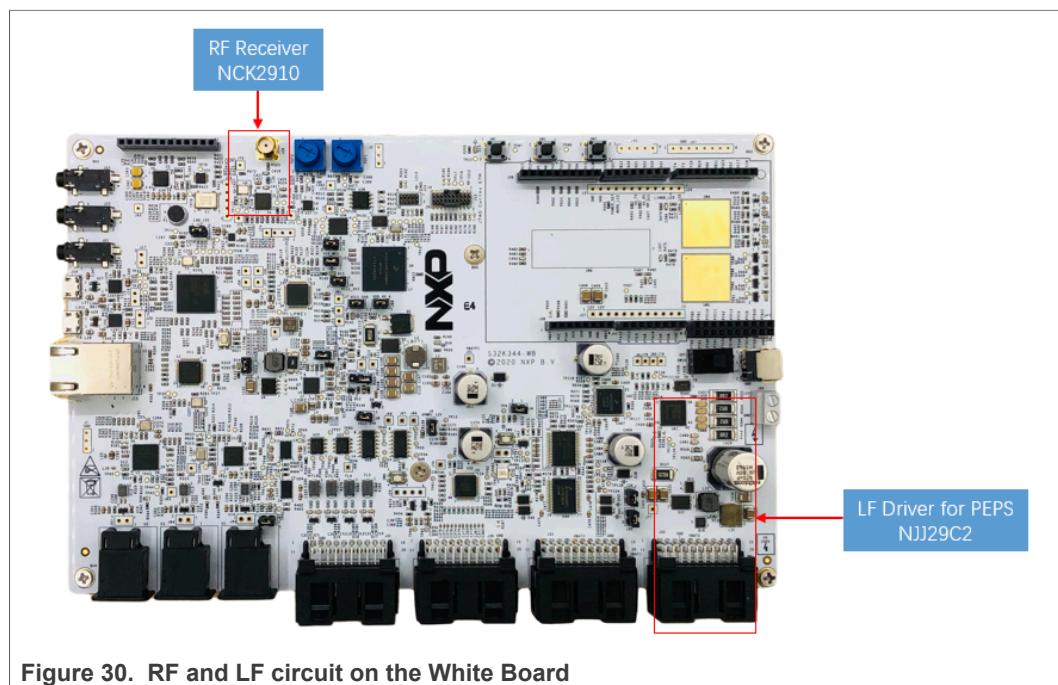

- LF driver and RF receiver for car access applications.

- 4 channels high side driver and 8 channels low side driver outputs.

- 2 channels USB-to-UART interfaces.

- 4 channels general purpose analog and digital inputs.

- 12 channels switch-detection inputs through CD1030.

- HB2001 for H-bridge driver.

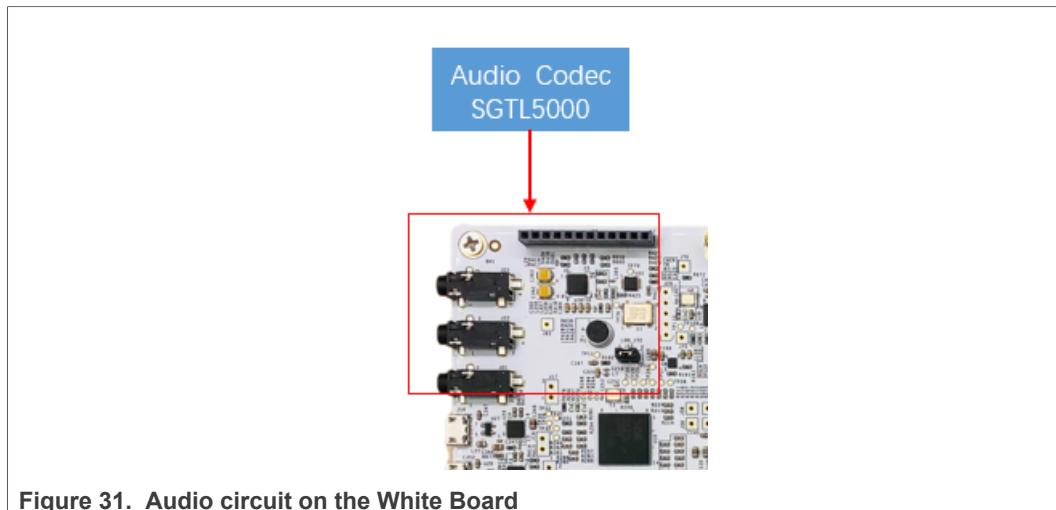

- Audio Codec SGTL5000 connected to MCU via I2S.

- Accelerometer sensor MMA8452 with I2C interface.

- 10 pin SWD debug interface and 20pin JTAG debug interface with TRACE capability.

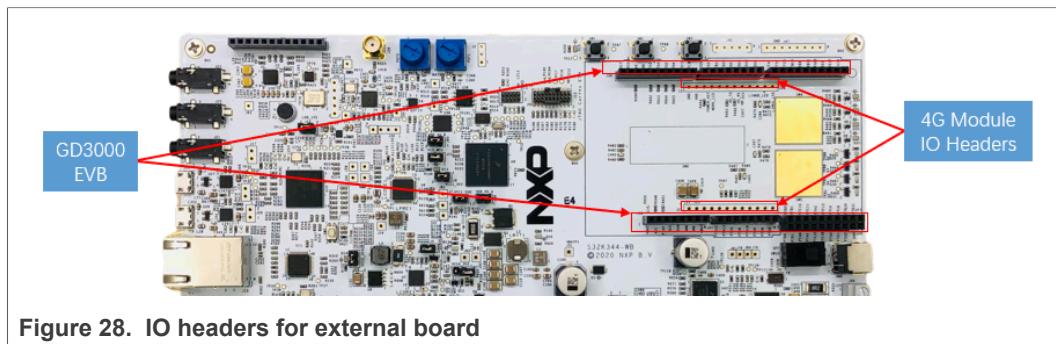

- IO Headers for external GD3000 EVB to evaluate motor control use cases.

- 7 User LEDs, 2 user buttons and 2 ADC potentiometers.

- Touch sense pads.

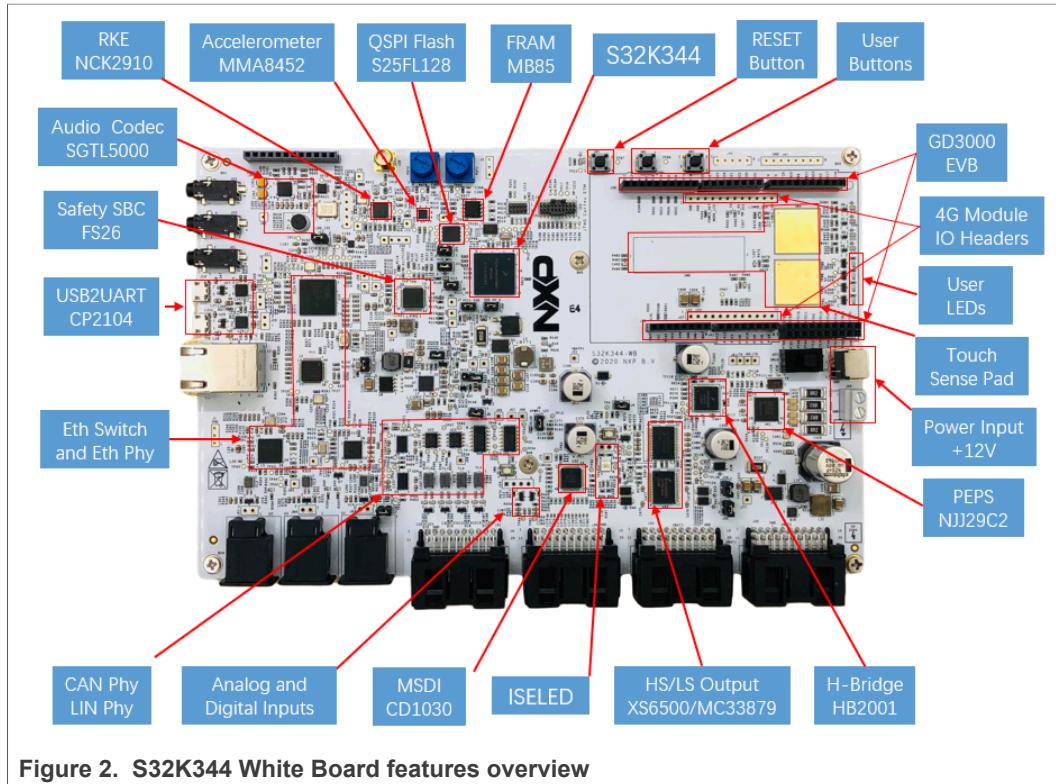

### 3 Connectors and interfaces

The following figure shows the connectors and interfaces of the White Board:

- Four 20-pin connectors J31, J32, J33 and J36 include most general-purpose inputs/outputs and CAN/LIN interfaces.

- Three automotive ethernet interfaces (100BASE-T1);

- One RJ45 can be connected to PC;

- Two USB-to-UART interfaces are used for printing some debug information in MCU;

- ARDUINO shield connectors can be used for compatible EVB installation (such as GD3000 EVB);

- Specific connectors for 4G module communication via UART interface;

Figure 3. S32K344 White Board connectors and interfaces

The signals definitions of J32 are listed in the following table:

Table 2. Signals definitions of J32

|  | <b>PIN</b> | <b>Label</b> | <b>Function</b> | <b>PIN</b> | <b>Label</b> | <b>Function</b> |

|--|------------|--------------|-----------------|------------|--------------|-----------------|

|  | J32-10     | PEPS_TXN5    | PEPS antenna    | J32-20     | PEPS_TXN9    | PEPS antenna    |

|  | J32-9      | PEPS_TXP5    | PEPS antenna    | J32-19     | PEPS_TXP9    | PEPS antenna    |

|  | J32-8      | PEPS_TXN3    | PEPS antenna    | J32-18     | PEPS_TXN7    | PEPS antenna    |

|  | J32-7      | PEPS_TXP3    | PEPS antenna    | J32-17     | PEPS_TXP7    | PEPS antenna    |

|  | J32-6      | VBAT2        | 12V power       | J32-16     | NC           | NC              |

|  | J32-5      | VBAT2        | 12V power       | J32-15     | NC           | NC              |

|  | J32-4      | PEPS_TXN1    | PEPS antenna    | J32-14     | GND          | GND             |

|  | J32-3      | PEPS_TXP1    | PEPS antenna    | J32-13     | GND          | GND             |

|  | J32-2      | D_IN_4       | PEPS wake up    | J32-12     | HB_OUT1      | HB2001 out      |

Table 2. Signals definitions of J32...continued

|  |       |        |              |        |         |            |

|--|-------|--------|--------------|--------|---------|------------|

|  | J32-1 | D_IN_3 | PEPS wake up | J32-11 | HB_OUT2 | HB2001 out |

|--|-------|--------|--------------|--------|---------|------------|

The signals definitions of J33 are listed in the following table:

Table 3. Signals definitions of J33

|  | PIN         | Label            | Function |  | PIN          | Label           | Function |

|-----------------------------------------------------------------------------------|-------------|------------------|----------|------------------------------------------------------------------------------------|--------------|-----------------|----------|

| J33-10                                                                            | GND         | GND              |          | J33-20                                                                             | VBAT1        | 12V power       |          |

| J33-9                                                                             | GND         | GND              |          | J33-19                                                                             | VBAT1        | 12V power       |          |

| J33-8                                                                             | NC          | NC               |          | J33-18                                                                             | LS_DRV_OUT_8 | Low side output |          |

| J33-7                                                                             | NC          | NC               |          | J33-17                                                                             | LS_DRV_OUT_7 | Low side output |          |

| J33-6                                                                             | VBAT3       | 12V power        |          | J33-16                                                                             | LS_DRV_OUT_6 | Low side output |          |

| J33-5                                                                             | VBAT3       | 12V power        |          | J33-15                                                                             | LS_DRV_OUT_5 | Low side output |          |

| J33-4                                                                             | HS_DRV_OUT4 | High side output |          | J33-14                                                                             | LS_DRV_OUT_4 | Low side output |          |

| J33-3                                                                             | HS_DRV_OUT3 | High side output |          | J33-13                                                                             | LS_DRV_OUT_3 | Low side output |          |

| J33-2                                                                             | HS_DRV_OUT2 | High side output |          | J33-12                                                                             | LS_DRV_OUT_2 | Low side output |          |

| J33-1                                                                             | HS_DRV_OUT1 | High side output |          | J33-11                                                                             | LS_DRV_OUT_1 | Low side output |          |

The signals definitions of J36 are listed in the following table:

Table 4. Signals definitions of J36

|  | PIN      | Label            | Function |  | PIN      | Label            | Function |

|-------------------------------------------------------------------------------------|----------|------------------|----------|-------------------------------------------------------------------------------------|----------|------------------|----------|

| J36-10                                                                              | GND      | GND              |          | J36-20                                                                              | +5V_OUT2 | +5V power        |          |

| J36-9                                                                               | ISELED_P | ISELED Interface |          | J36-19                                                                              | ISELED_N | ISELED Interface |          |

| J36-8                                                                               | MSDI_SP5 | Switch input     |          | J36-18                                                                              | MSDI_SG5 | Switch input     |          |

| J36-7                                                                               | MSDI_SP4 | Switch input     |          | J36-17                                                                              | MSDI_SG4 | Switch input     |          |

| J36-6                                                                               | MSDI_SP3 | Switch input     |          | J36-16                                                                              | MSDI_SG3 | Switch input     |          |

| J36-5                                                                               | MSDI_SP2 | Switch input     |          | J36-15                                                                              | MSDI_SG2 | Switch input     |          |

| J36-4                                                                               | MSDI_SP1 | Switch input     |          | J36-14                                                                              | MSDI_SG1 | Switch input     |          |

| J36-3                                                                               | MSDI_SP0 | Switch input     |          | J36-13                                                                              | MSDI_SG0 | Switch input     |          |

| J36-2                                                                               | A_IN_2   | ADC input        |          | J36-12                                                                              | D_IN_2   | Digital input    |          |

| J36-1                                                                               | A_IN_1   | ADC input        |          | J36-11                                                                              | D_IN_1   | Digital input    |          |

The signals definitions of J31 are listed in the following table:

Table 5. Signals definitions of J31

|  | <b>PIN</b> | <b>Label</b> | <b>Function</b> |  | <b>PIN</b> | <b>Label</b> | <b>Function</b> |

|--|------------|--------------|-----------------|--|------------|--------------|-----------------|

|  | J31-10     | LIN8         | LIN interface   |  | J31-20     | NC           | NC              |

|  | J31-9      | LIN7         | LIN interface   |  | J31-19     | NC           | NC              |

|  | J31-8      | LIN6         | LIN interface   |  | J31-18     | CANL_3       | TJA1145 CANL    |

|  | J31-7      | LIN5         | LIN interface   |  | J31-17     | CANH_3       | TJA1145 CANH    |

|  | J31-6      | LIN4         | LIN interface   |  | J31-16     | CANL_2       | TJA1145 CANL    |

|  | J31-5      | LIN3         | LIN interface   |  | J31-15     | CANH_2       | TJA1145 CANH    |

|  | J31-4      | LIN2         | LIN interface   |  | J31-14     | CANL_1       | TJA1044 CANL    |

|  | J31-3      | LIN1         | LIN interface   |  | J31-13     | CANH_1       | TJA1044 CANH    |

|  | J31-2      | GND          | GND             |  | J31-12     | CANL_0       | TJA1044 CANL    |

|  | J31-1      | KL15_WAKE    | SBC wake input  |  | J31-11     | CANH_0       | TJA1044 CANH    |

## 4 MCU pins assignments and board resources mapping

The hardware configurations and MCU PINs assignments are listed in below table.

Table 6. White Board resources mapping

| Interface            | Reference/ Signals  | Configuration | Description                                                        |

|----------------------|---------------------|---------------|--------------------------------------------------------------------|

| Power Input          | VBAT1/2/3           | 12V           | 12V power supply input for this board                              |

| MCU Power Supply     | VCC1_5V0 (VDD_HV_A) | 5.0V          | Some MCU pins are in VDD_HV_A domain                               |

|                      | VCC1_3V3 (VDD_HV_B) | 3.3V          | Some MCU pins are in VDD_HV_B domain                               |

|                      | VREFH MCU           | 5.0V          | ADC reference voltage                                              |

|                      | VCC_1V5             | 1.5V          | MCU Core is supplied by 1.5V from SBC                              |

|                      | V11 MCU             | 1.1V          | MCU generated 1.1V                                                 |

|                      | V25 MCU             | 2.5V          | MCU generated 2.5V                                                 |

| Other Power Supplies | BUCK_5V0            | 5.0V          | 5V to supply some circuits on the board                            |

|                      | BUCK_3V3            | 3.3V          | 3.3V to supply ethernet related circuits                           |

|                      | LDO_1V2             | 1.2V          | 1.2V LDO to supply ethernet switch core                            |

| Ethernet             | MCU MAC             | Enabled       | MCU MAC is connected to ethernet switch SJA1105 MII_0 in RMII mode |

|                      | TJA1101             | Enabled       | SJA1105 MII_1                                                      |

|                      | DP83848C            | Enabled       | SJA1105 MII_2                                                      |

|                      | TJA1102             | Enabled       | SJA1105 MII_3 and MII_4                                            |

| SPI                  | LPSPI_0             | PCS0          | NCK2910 (RF Receiver)                                              |

|                      |                     | PCS2          | CD1030(MSDI)                                                       |

|                      |                     | PCS3          | XS6500(High Side Driver)                                           |

|                      |                     | PCS4          | MC33879 (Low Side Driver)                                          |

|                      |                     | PCS5          | HB2001(H-Bridge Driver)                                            |

|                      | LPSPI_1             | PCS0          | FS26 (Safety SBC)                                                  |

|                      | LPSPI_2 (3.3V)      | PCS0          | SJA1105 (Ethernet Switch)                                          |

|                      | LPSPI_3             | PCS0          | SJA1124 (LIN Ctrl and Phy)                                         |

|                      |                     | PCS1          | TJA1145 (CAN Phy)                                                  |

|                      |                     | PCS3          | TJA1145 (CAN Phy)                                                  |

|                      | LPSPI_4             | PCS0          | IO Header                                                          |

|                      |                     | PCS1          | NJJ29C2 (LF Driver)                                                |

|                      | LPSPI_5             | PCS0          | IO Header                                                          |

| QSPI                 | QSPI_A              | Enabled       | QSPI Flash 128Mb                                                   |

Table 6. White Board resources mapping...continued

|                     |               |                     |                                                        |

|---------------------|---------------|---------------------|--------------------------------------------------------|

| I2C                 | LPI2C0 (3.3V) | Enabled             | MMA8452 (Accel Sensor, address 0x1D)                   |

|                     |               |                     | SGTL5000 (Audio Codec, address 0x0A)                   |

|                     |               |                     | CS2100 (Clock Multiplier, address 0x4F)                |

|                     |               |                     | FRAM (Fast EEPROM, address 0x57)                       |

| CAN                 | CAN_0         | TJA1044_1           | PTA7_CAN0_TX, PTA6_CAN0_RX                             |

|                     | CAN_1         | TJA1044_2           | PTA23_CAN1_TX, PTA22_CAN1_RX                           |

|                     | CAN_2         | TJA1145_1           | PTD18_CAN2_TX, PTD19_CAN2_RX                           |

|                     | CAN_3         | TJA1145_2           | PTE28_CAN3_TX, PTE29_CAN3_RX                           |

|                     | CAN_4         | IO Header           | PTG8_CAN4_TX, PTG9_CAN4_RX                             |

| LIN                 | LIN1          | SJA1124_LIN1        | LIN Controller and Phy controlled by LPSPi3 with PCS0. |

|                     | LIN2          | SJA1124_LIN2        |                                                        |

|                     | LIN3          | SJA1124_LIN3        |                                                        |

|                     | LIN4          | SJA1124_LIN4        |                                                        |

|                     | LIN5          | TJA1124_LIN1        | PTF2_LPUART6_TX,<br>PTF3_LPUART6_RX                    |

|                     | LIN6          | TJA1124_LIN2        | PTF18_LPUART7_TX,<br>PTF19_LPUART7_RX                  |

|                     | LIN7          | TJA1124_LIN3        | PTF23_LPUART9_TX,<br>PTF24_LPUART9_RX                  |

|                     | LIN8          | TJA1124_LIN4        | PTF16_LPUART12_TX,<br>PTF17_LPUART12_RX                |

| UART                | LPUART0       | CP2104 USB2<br>UART | PTA27_LPUART0_TX,<br>PTA28_LPUART0_RX                  |

|                     | LPUART2       |                     | PTE12_LPUART2_TX,<br>PTD17_LPUART2_RX                  |

|                     | LPUART1       | Ext 4G Module       | PTB22_LPUART1_TX,<br>PTB23_LPUART1_RX                  |

| Audio               | SAI0          | Enabled             | SGTL5000 Audio Codec                                   |

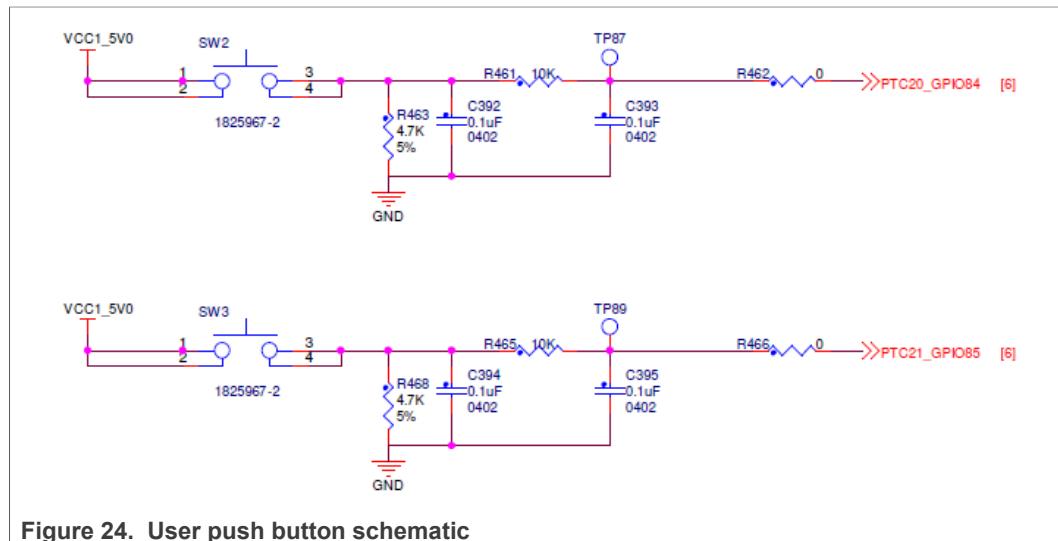

| User<br>Peripherals | Push Buttons  | SW2                 | PTC20 (high active)                                    |

|                     |               | SW3                 | PTC21 (high active)                                    |

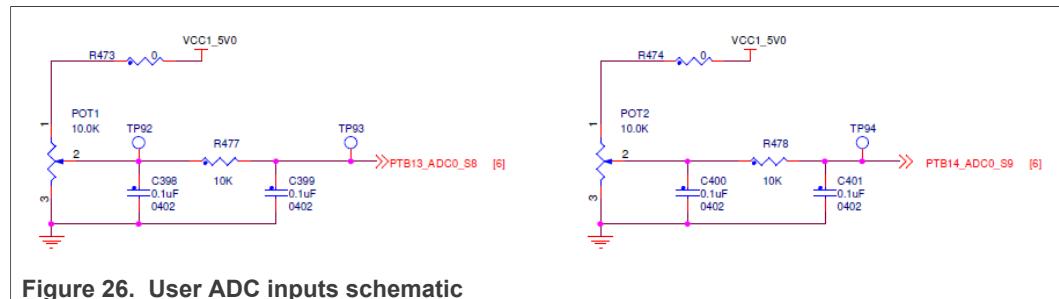

|                     | ADC POT       | POT1                | PTB13 (ADC0_S8)                                        |

|                     |               | POT2                | PTB14 (ADC0_S9)                                        |

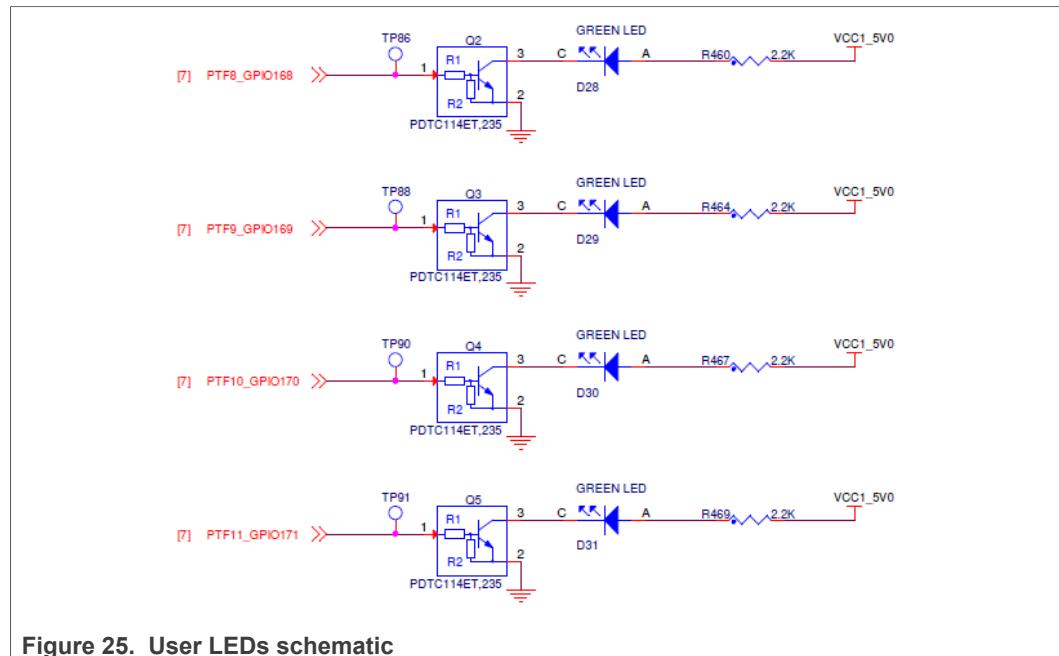

|                     | User LEDs     | LED D28             | PTF8 (high active)                                     |

|                     |               | LED D29             | PTF9 (high active)                                     |

|                     |               | LED D30             | PTF10 (high active)                                    |

|                     |               | LED D31             | PTF11 (high active)                                    |

|                     |               | LED D44             | PTG0 (low active)                                      |

Table 6. White Board resources mapping...continued

|                         |                  |                |                                |

|-------------------------|------------------|----------------|--------------------------------|

|                         | Touch Sense Pad  | LED D45        | PTG1 (low active)              |

|                         |                  | LED D46        | PTG2 (low active)              |

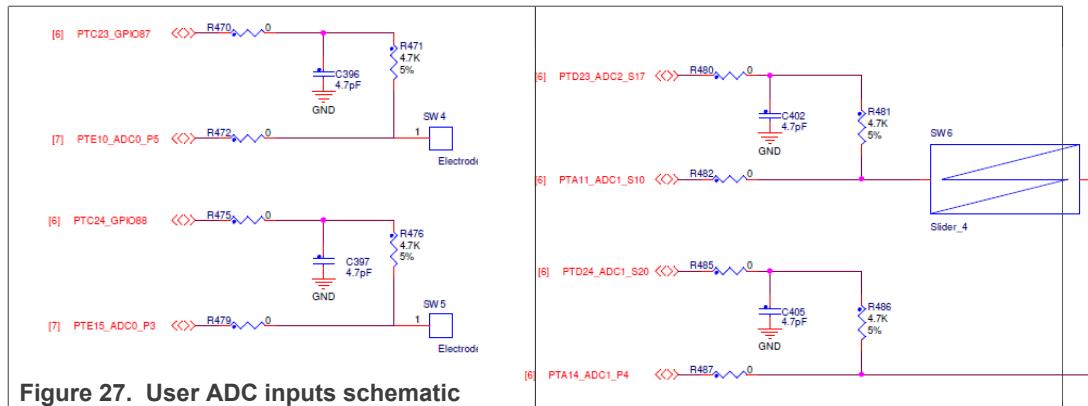

|                         |                  | SW4            | PTC23, PTE10                   |

|                         |                  | SW5            | PTC24, PTE15                   |

|                         |                  | Slider         | PTD23, PTA11, PTD24, PTA14     |

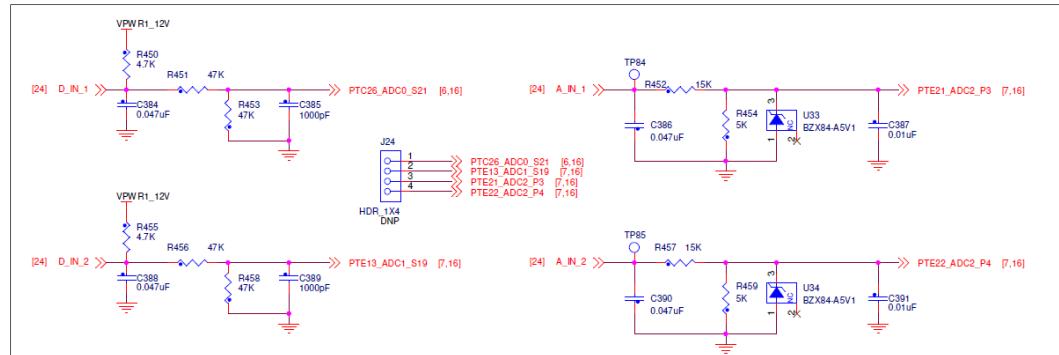

| General Purpose Inputs  | Analog Inputs    | A_IN_1 (0~12V) | PTE21_ADC2_P3                  |

|                         |                  | A_IN_2 (0~12V) | PTE22_ADC2_P4                  |

|                         | Digital Inputs   | D_IN_1 (0~12V) | PTC26_ADC0_S21                 |

|                         |                  | D_IN_2 (0~12V) | PTE13_ADC1_S19                 |

| General Purpose Outputs | High Side Output | HS_D1          | PTG18_EMIOS2_CH18              |

|                         |                  | HS_D2          | PTG19_EMIOS2_CH19              |

|                         |                  | HS_D3          | PTG20_EMIOS2_CH20              |

|                         |                  | HS_D4          | PTG21_EMIOS2_CH21              |

|                         | Low Side Output  | LS_DRV_OUT1    | Controlled by LPSPI0 with PCS4 |

|                         |                  | LS_DRV_OUT2    | Controlled by LPSPI0 with PCS4 |

|                         |                  | LS_DRV_OUT3    | Controlled by LPSPI0 with PCS4 |

|                         |                  | LS_DRV_OUT4    | Controlled by LPSPI0 with PCS4 |

|                         |                  | LS_DRV_OUT5    | PTE20_EMIOS1_CH0               |

|                         |                  | LS_DRV_OUT6    | PTE27_EMIOS1_CH7               |

|                         |                  | LS_DRV_OUT7    | Controlled by LPSPI0 with PCS4 |

|                         |                  | LS_DRV_OUT8    | Controlled by LPSPI0 with PCS4 |

| Debug Interface         | JTAG             | JTAG_TMS       | PTA4                           |

|                         |                  | JTAG_TCLK      | PTC4                           |

|                         |                  | JTAG_TDO       | PTA10                          |

|                         |                  | JTAG_TDI       | PTC5                           |

|                         |                  | RESET          | PTA5                           |

|                         | TRACE            | TRACE_CLKOUT   | PTG6                           |

|                         |                  | TRACE_D0       | PTG7                           |

|                         |                  | TRACE_D1       | PTG15                          |

|                         |                  | TRACE_D2       | PTG16                          |

|                         |                  | TRACE_D3       | PTF31                          |

## 5 White Board startup

Make sure the jumper J5 is closed and J87 is open so the SBC FS26 can power up in debug mode. Apply 12V to the power supply input. Turn on the switch SW10. Connect debugger to the SWD interface and refer to the White Board quick start guide to start the software development.

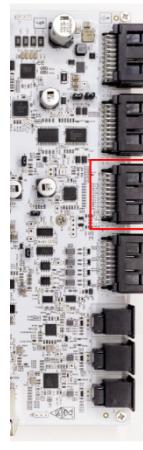

The following figure shows the LED indicators for various power supplies on the board.

Figure 4. S32K344 White Board features

The 12V can be applied either through the power jack J3, connector J88 or the connector pins J33-9,10(GND)/J33-19,20(VBAT). The LEDs indicate the presence of power supply as following:

- LED D10 – indicates that the 12V is connected to the board correctly;

- LED D11 – indicates that the 5V supply from SBC is ON;

- LED D12 – indicates that the 5V supply from the standalone DC/DC is ON;

- LED D13 – indicates that the 3.3V supply from SBC is ON;

- LED D14 – indicates that the 3.3V supply from standalone DC/DC is ON;

- LED D15 – indicates that the MCU RESET pin is low (MCU in reset status);

The above figure also shows the basic elements to start the White Board:

- 12V power input

- 10-pin Cortex Debug Connector (SWD/JTAG debug interface)

- 20-pin Debug + ETM connector (Debug with trace capability)

- RESET push button and RESET LED indicator

- USB2UART interface

## 6 Power supply

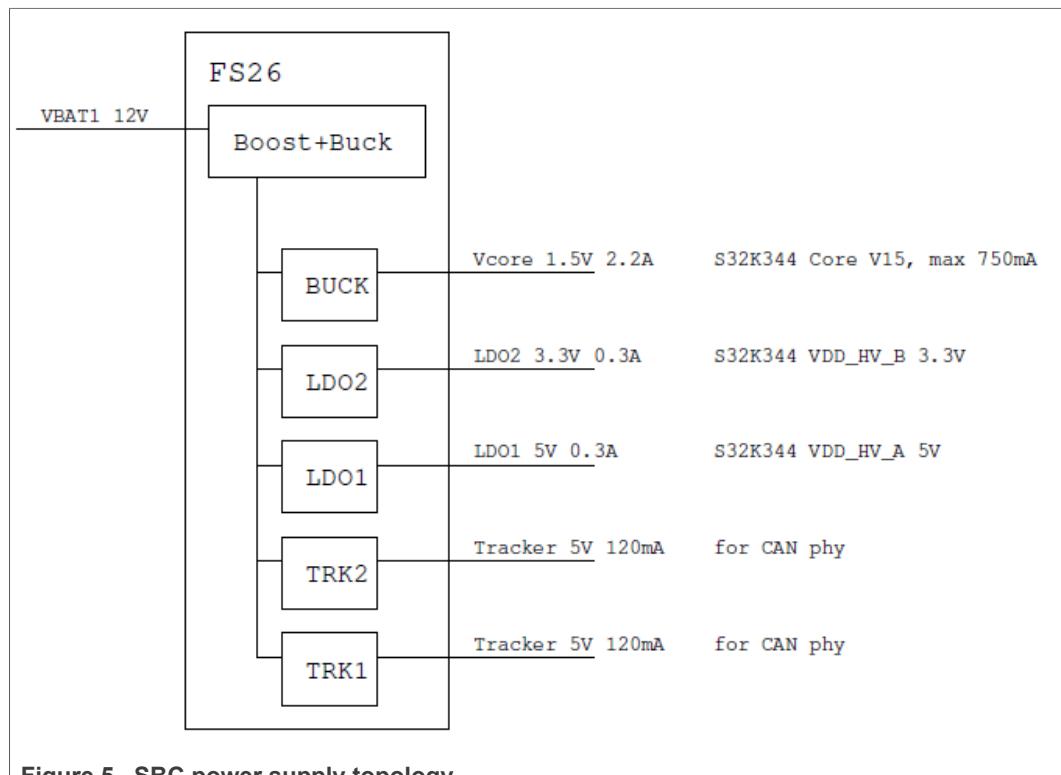

The White Board requires an external power supply of 12V/1A, which is fed to the following devices on the board.

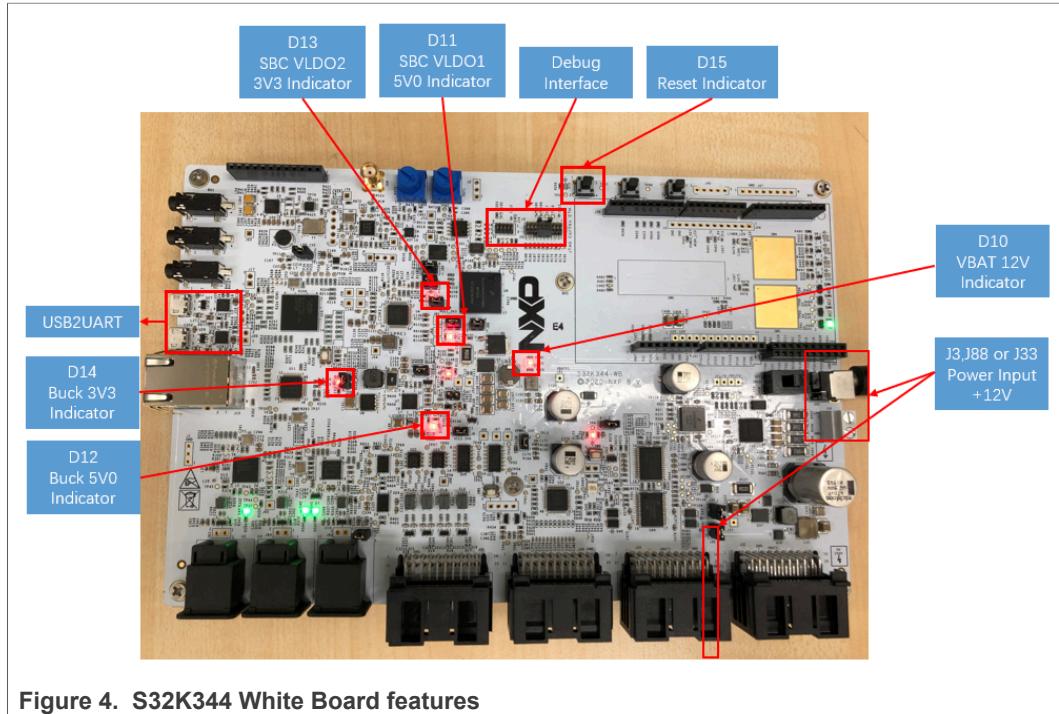

- SBC FS26 – it powers the MCU with 5V (MCU VDD\_HV\_A domain), 3.3V (MCU VDD\_HV\_B domain) and 1.5V (MCU core). See following figure for SBC power supply topology.

- SBC generates 5V(Tracker1 and Tracker2) to power the CAN phys (optional). The CAN phys are powered by VCC1\_5V0 by default.

- 5V buck circuit – it is used as a backup 5V power supply.

- 3.3V buck circuit – it powers the ethernet switch and ethernet phy circuits.

- The 3.3V is supplied to the standalone 1.2V LDO, which powers the ethernet switch core.

- High side driver (XS6500) – it requires 12V to operate correctly.

- LF driver (NJJ29C2) – it requires 12V to operate correctly.

Power supply topology of this board is shown in the following two figures.

Figure 5. SBC power supply topology

Figure 6. Power supply topology

The MCU has two power domains - VDD\_HV\_A and VDD\_HV\_B. On the white board, VDD\_HV\_A is supplied with 5V and VDD\_HV\_B is supplied with 3.3V and this configuration is fixed on the board. All 5V signals on the MCU are powered by VDD\_HV\_A and all 3.3V signals on MCU are powered by VDD\_HV\_B, so that the use of voltage level shifters is unnecessary.

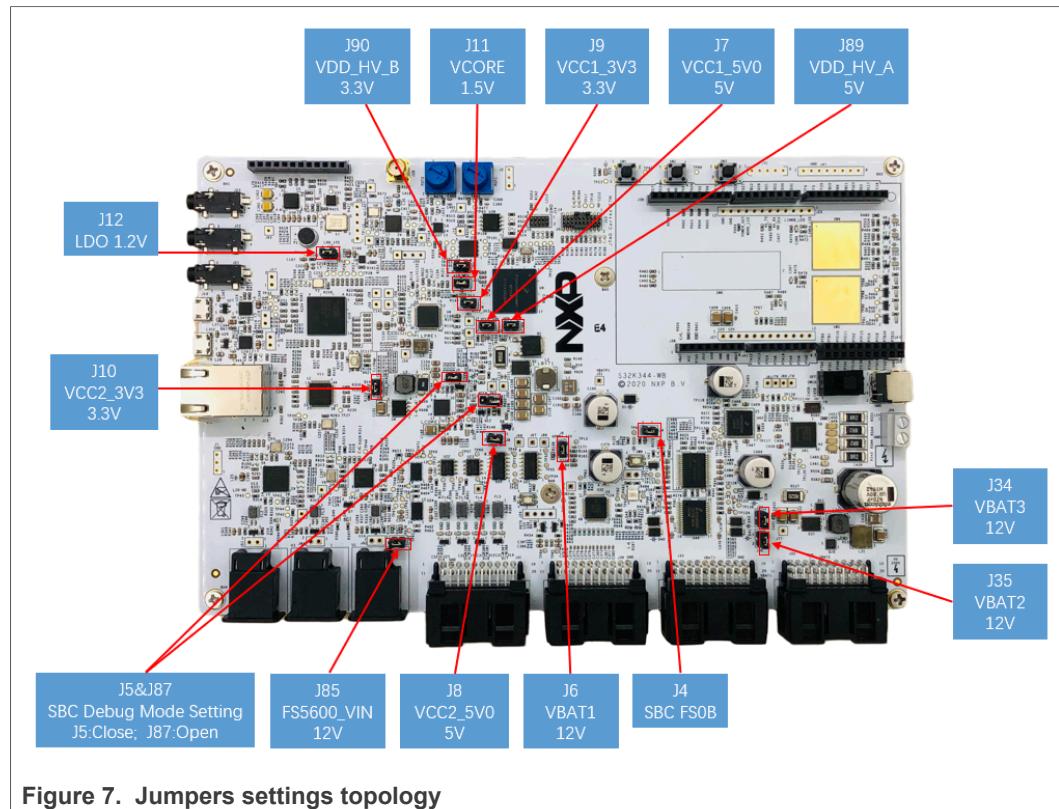

## 7 Jumper settings

The following jumpers on the board are used for measuring the current consumption of the corresponding power supply:

**Table 7. Jumpers for current measurement**

| Reference | Position           | Description                                    |

|-----------|--------------------|------------------------------------------------|

| J6        | 1-2 Default Closed | 12V power input after reverse protection diode |

| J7        | 1-2 Default Closed | FS26 LDO1 (5V) output current                  |

| J89       | 1-2 Default Closed | MCU VDD_HV_A current consumption               |

| J8        | 1-2 Default Closed | Buck 5V output current                         |

| J9        | 1-2 Default Closed | FS26 LDO2 (3.3V) output current                |

| J90       | 1-2 Default Closed | MCU VDD_HV_B current consumption               |

| J10       | 1-2 Default Closed | Buck 3.3V output current                       |

| J11       | 1-2 Default Closed | 1.5V for MCU core                              |

| J12       | 1-2 Default Closed | 1.2V for SJA1105 core                          |

| J34       | 1-2 Default Closed | 12V power input for high side driver XS6500    |

| J35       | 1-2 Default Closed | 12V power input for LF driver NJJ29C2          |

| J85       | 1-2 Default Closed | 12V power input for FS5600                     |

Other jumpers on the board are shown in below table:

**Table 8. Jumpers for VBAT power supply source**

| Reference | Position                               | Description                                                                                                                                      |

|-----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| J5<br>J87 | 1-2 Default Closed<br>1-2 Default Open | Enable SBC debug mode, thus watchdog refreshing from SPI is not needed. J5 should be closed and J87 should be open for FS26 entering debug mode. |

| J4        | 1-2 Default Closed                     | Allow SBC FS0B to disable high/low side driver outputs.                                                                                          |

The following figure shows the locations of these jumpers on the White Board.

## 8 General functional description

### 8.1 MCU HW configuration

#### 8.1.1 MCU power supply configuration

S32K344 has two power domains – VDD\_HV\_A and VDD\_HV\_B. They can be supplied with either 5V or 3.3V. See below figure for PINs distribution for the two domains. The white board optimizes the PINs assignment to minimize the usage of voltage level shifters. VDD\_HV\_A is supplied with 5V and PINs in VDD\_HV\_A domain are mostly used for 5V circuits on the board. VDD\_HV\_B is supplied with 3.3V and PINs in VDD\_HV\_B domain are mostly used for 3.3V circuits on the board.

|                                                                         | 1          | 2          | 3     | 4          | 5     | 6     | 7          | 8        | 9          | 10         | 11         | 12    | 13    | 14         | 15    | 16         | 17               |   |

|-------------------------------------------------------------------------|------------|------------|-------|------------|-------|-------|------------|----------|------------|------------|------------|-------|-------|------------|-------|------------|------------------|---|

| A                                                                       | PTC10      | PTA8       | PTA5  | PTE30      | PTE1  | PTF0  | PTA12      | PTE24    | PTA13      | PTA4       | PTA15      | PTA16 | PTA0  | PTB8       | PTD27 | PTD25      | PTG11            | A |

| B                                                                       | PTA18      | <b>VSS</b> | PTA9  | PTE31      | PTE0  | PTF1  | PTA11      | PTE25    | PTE22      | PTF2       | PTE6       | PTC7  | PTD28 | PTA1       | PTF9  | <b>VSS</b> | PTF10            | B |

| C                                                                       | PTA19      | PTE16      | PTA22 | PTE28      | PTE29 | PTF2  | PTF4       | PTF5     | PTF7       | PTE20      | PTE19      | PTC6  | PTD31 | PTD29      | PTB9  | PTD25      | PTB11 <th>C</th> | C |

| D                                                                       | PTA21      | PTE15      | PTA23 | <b>VSS</b> | PTE26 | PTF3  | PTF6       | PTE23    | <b>VSS</b> | PTF8       | PTE18      | PTE17 | PTD30 | VDD_HV_A   | PTB10 | PTD24      | PTA2             | D |

| E                                                                       | PTE11      | PTE10      | PTD1  | PTA20      |       |       |            |          |            |            |            |       |       | PTF13      | PTF12 | PTA9       | PTD23            | E |

| F                                                                       | PTE13      | PTE5       | PTD0  | PTG8       |       | PTA4  | PTC4       | PTC5     | PTE21      | PTG27      | PTG26      | PTG25 |       | PTF15      | PTF14 | PTD2       | PTD3             | F |

| G                                                                       | PTA24      | PTG9       | PTG13 | PTG4       |       | PTE4  | <b>VSS</b> | PTA10    | PTE27      | VDD_HV_A   | <b>VSS</b> | PTG24 |       | PTF17      | PTF16 | PTD4       | PTD22            | G |

| H                                                                       | PTA25      | PTG1       | PTG14 | PTG5       |       | VREFH | VDD_HV_A   | V15      | V11        | V15        | PTF11      | PTG23 |       | PTF18      | PTD21 | PTD13      | PTD12            | H |

| J                                                                       | <b>VSS</b> | PTG0       | PTG2  | <b>VSS</b> |       | VREFL | V25        | V11      | <b>VSS</b> | V11        | PTF19      | PTG22 |       | <b>VSS</b> | PTF20 | PTB15      | PTB14            | J |

| K                                                                       | XTAL       | PTG3       | PTF30 | PTF29      |       | PTG7  | PTG6       | V15      | V11        | V15        | VDD_HV_A   | PTG21 |       | PTF21      | PTD20 | PTB17      | PTB16            | K |

| L                                                                       | XTAL       | PTA26      | PTE14 | PTD15      |       | PTG15 | <b>VSS</b> | VDD_HV_A | PTF31      | PTF28      | <b>VSS</b> | PTG20 |       | PTC31      | PTD19 | PTD18      | PTA17            | L |

| M                                                                       | PTE12      | PTA27      | PTA29 | PTD14      |       | PTB22 | PTB23      | PTG16    | PTG17      | PTG18      | PTG19      | PTF24 |       | PTF23      | PTA6  | PTA2       | PTE7             | M |

| N                                                                       | PTE5       | PTA28      | PTD17 | VDD_HV_B   |       |       |            |          |            |            |            |       |       | PTC9       | PTC8  | PTC29      | PTC30            | N |

| P                                                                       | PTA31      | PTD16      | PTA30 | <b>VSS</b> | PTD18 | PTC15 | PTB24      | PTB25    | PTB27      | PTB28      | PTC12      | PTF25 | PTF27 | <b>VSS</b> | PTC26 | PTB6       | PTC28            | P |

| R                                                                       | PTB18      | PTB19      | PTE9  | PTE8       | PTD12 | PTC17 | VDD_HV_B   | PTD8     | PTB26      | VDD_HV_B   | PTC13      | PTF26 | PTC21 | PTC25      | PTC24 | PTC27      | PTB1             | R |

| T                                                                       | PTB20      | <b>VSS</b> | PTC5  | PTC2       | PTD6  | PTD10 | <b>VSS</b> | PTC1     | PTC14      | <b>VSS</b> | PTB2       | PTC19 | PTC20 | PTB31      | PTC11 | <b>VSS</b> | PTC10            | T |

| U                                                                       | PTB21      | PTB5       | PTB4  | PTD7       | PTD5  | PTD11 | PTC0       | PTD9     | PTC15      | PTB8       | PTC18      | PTB29 | PTB30 | PTC23      | PTC22 | PTF22      | PTG12            | U |

|                                                                         | 1          | 2          | 3     | 4          | 5     | 6     | 7          | 8        | 9          | 10         | 11         | 12    | 13    | 14         | 15    | 16         | 17               |   |

| MCU Pin Function                                                        |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| #Pins                                                                   |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| VDD_HV_A and VREFH Power Pin                                            |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 6                                                                       |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| I/Os pins on the VDD_HV_A Power Domain [including JTAG(4) and RESET(1)] |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 166                                                                     |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| VDD_HV_B Power Pin                                                      |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 3                                                                       |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| I/Os pins on the VDD_HV_B Power Domain                                  |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 52                                                                      |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| XTAL/EXTAL                                                              |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 2                                                                       |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| V25 Power Pin                                                           |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 1                                                                       |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| V15 Power Pin                                                           |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 4                                                                       |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| V11 Power Pin                                                           |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 4                                                                       |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| VSS and VREFL – Ground pin                                              |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 19                                                                      |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| TOTAL of pins                                                           |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

| 257                                                                     |            |            |       |            |       |       |            |          |            |            |            |       |       |            |       |            |                  |   |

Figure 8. Pins distribution for different power domains

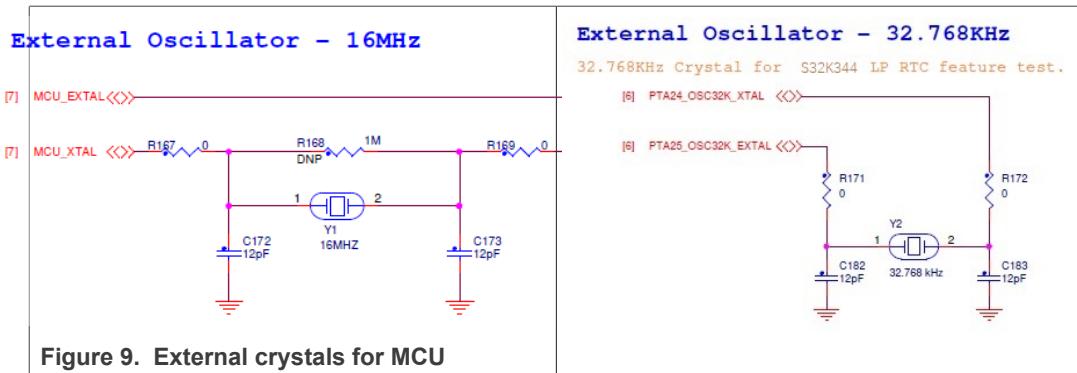

#### 8.1.2 MCU clock settings

MCU can generate 320MHz PLL clock based on 16MHz external crystal. And in low-power modes, it can use external 32KHz crystal to minimize the power consumption.

### 8.1.3 MCU reset control

The MCU RESET pin is bidirectional. When acting as input, MCU can be reset either by push button “SW1” on the board or SBC RESET signal. When acting as output, some MCU internal failures (such as watchdog timeout) will pull RESET pin low and SBC can sense the MCU reset event and react accordingly.

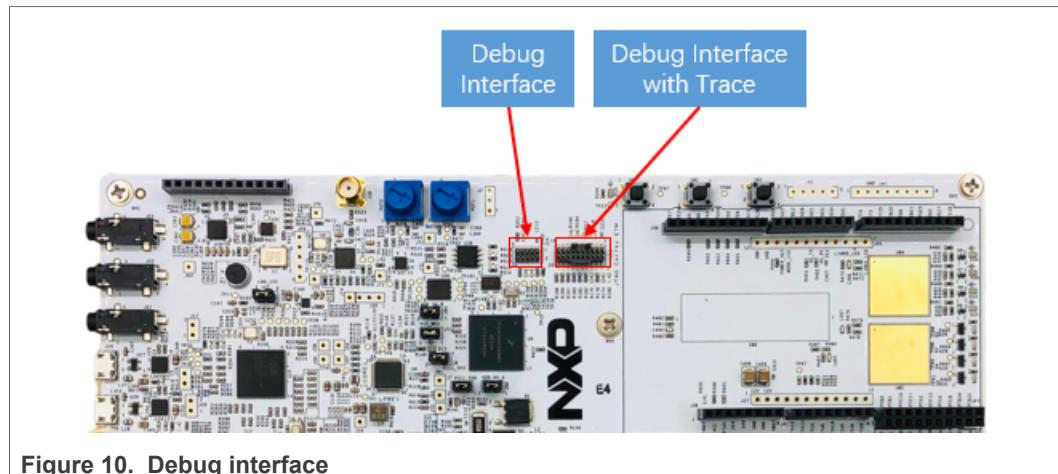

### 8.1.4 MCU debug interface

The White Board provides two types of debug interface 10-pin connector (SWD/JTAG) and 20-pin connector (JTAG with ETM). The pins used are listed in below table. JTAG pins are necessary for debugging the MCU and the TRACE pins are optional.

Table 9. Debug interface pins

|       |              |       |

|-------|--------------|-------|

| JTAG  | JTAG_TMS     | PTA4  |

|       | JTAG_TCLK    | PTC4  |

|       | JTAG_TDO     | PTA10 |

|       | JTAG_TDI     | PTC5  |

|       | RESET        | PTA5  |

| TRACE | TRACE_CLKOUT | PTG6  |

|       | TRACE_D0     | PTG7  |

|       | TRACE_D1     | PTG15 |

|       | TRACE_D2     | PTG16 |

|       | TRACE_D3     | PTF31 |

Figure 10. Debug interface

## 8.2 SBC features

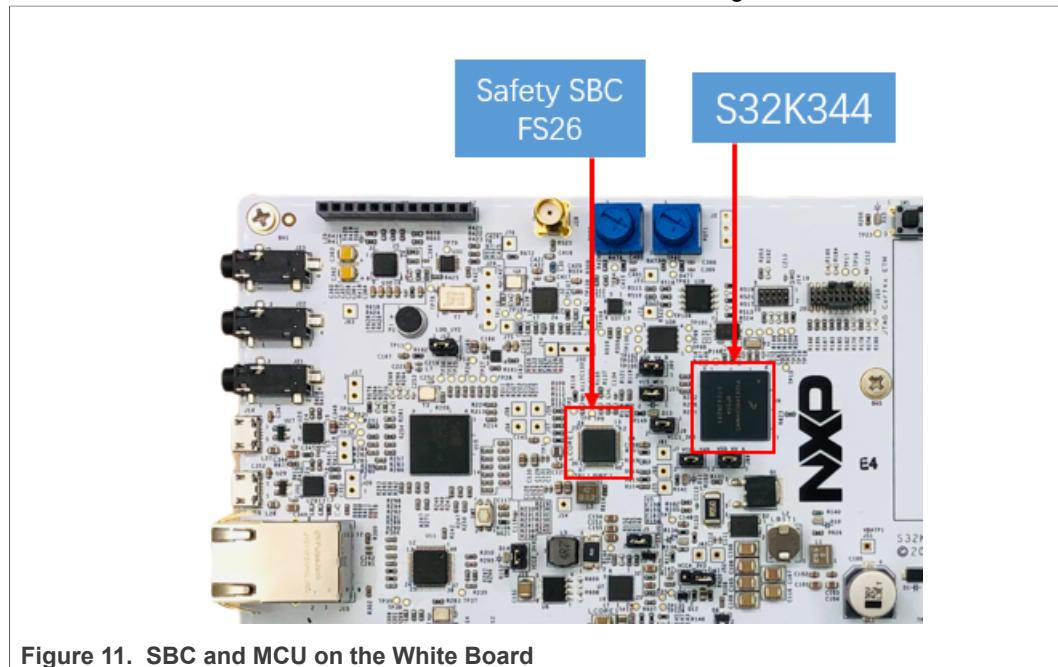

### 8.2.1 SBC and MCU connections

The SBC and MCU on the White Board are shown in below figure.

Figure 11. SBC and MCU on the White Board

Connections between SBC and MCU are listed in below table.

Table 10. SBC and MCU connections

| SBC                        | MCU                            |

|----------------------------|--------------------------------|

| VLDO1 5V                   | VDD_HV_A                       |

| VLDO2 3.3V irrelevant      | VDD_HV_B                       |

| VCORE 1.5V                 | V15                            |

| SPI (MOSI, MISO, SCLK, CS) | LPSPI_1 (SOUT, SIN, SCK, PCS0) |

Table 10. SBC and MCU connections...continued

|             |                                     |

|-------------|-------------------------------------|

| VDDIO       | VDD_HV_A                            |

| RST         | PTA5 MCU_RESETB                     |

| INT         | Interrupt input (PTG3)              |

| FCCU1/FCCU2 | FCCU_ERR0 / FCCU_ERR1 (PTF16/PTF14) |

| MUX-OUT     | ADC2_P7 input (PTE25)               |

### 8.2.2 SBC wakeup function

- Wakeup input by external key-on signal (0V to 12V transition on WAKE1).

- Push button SW7 on the board can generate such transitions.

- Wakeup input by LIN phy.

- Wakeup input by CAN phy or Ethernet phy.

### 8.2.3 SBC fail-safe outputs

SBC will pull FS0B and FS1B low when it detects certain failures, without MCU intervene.

- FS0B – disable high driver outputs (XS6500).

- FS1B – it's left float and can be routed to customer desired circuit.

FS0B or FS1B assertion is indicated by LED D8 or LED D9 on the White Board. These two signals can be released by special sequence of SPI commands. Refer to FS26 datasheet for details.

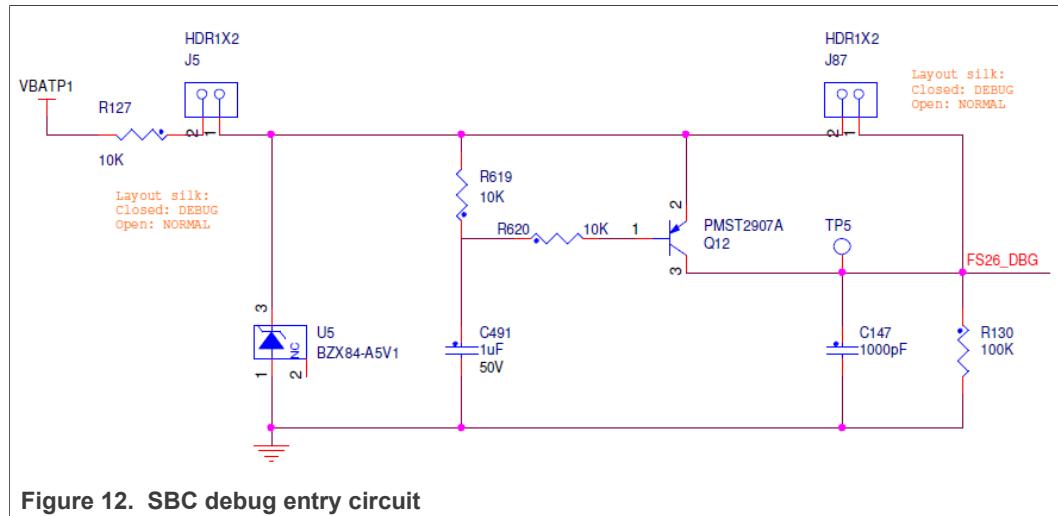

### 8.2.4 SBC debug mode

Jumper J5 needs to be closed and J87 to be open for the FS26 debug mode when powering up. In this way the FS26 doesn't need the watchdog refreshing from the MCU by SPI.

Figure 12. SBC debug entry circuit

According to FS26 datasheet, the FS26 debug mode is entered if ~4V is detected on FS26 DEBUG pin when FS26 is powered up. Then the FS26 starts to supply the MCU when DEBUG pin back to GND. So a 4V pulse is seen during power-up on FS26 DEBUG pin to enter debug mode.

## 8.3 Communication interfaces

### 8.3.1 Ethernet interfaces

The ethernet switch SJA1105 is used and 4 ethernet interfaces are available on the board. One of them is 100BASE-TX which can be connected to PC for diagnostics and test. The other three interfaces are automotive ethernet (100BASE-T1). To meet SJA1105 current consumption requirements, a 3.3V buck circuit from FS56 and a 1.2V LDO is used to supply this device.

Figure 13. Ethernet circuit block diagram

Figure 14. Ethernet circuit on the White Board

### 8.3.2 CAN and LIN interfaces

There are 4 CAN interfaces on this board. The CAN phy TJA1145 is powered from VBAT 12V and can work in sleep mode with only VBAT kept on. External specified CAN

messages can wake up TJA1145. MCU configures TJA1145 operation modes by sending proper SPI commands.

The device SJA1124 is a LIN controller and transceiver. MCU can use one SPI to access this device and generate 4 channels LIN interfaces. The other 4 LINs are linked to 4 LPUART modules on MCU.

Figure 15. CAN/LIN circuit block diagram

Figure 16. CAN and LIN transceivers on White Board

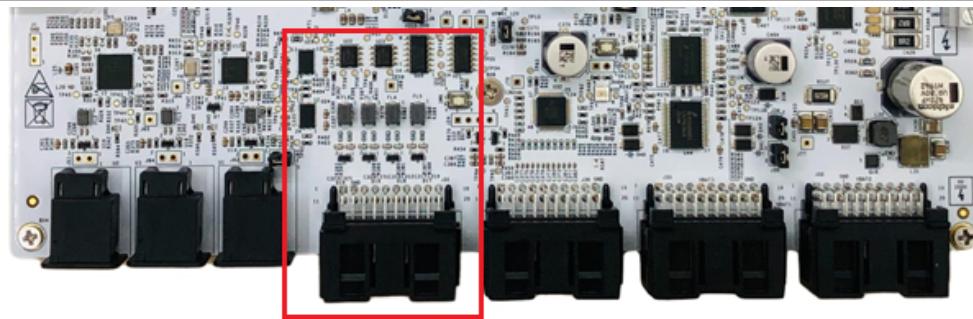

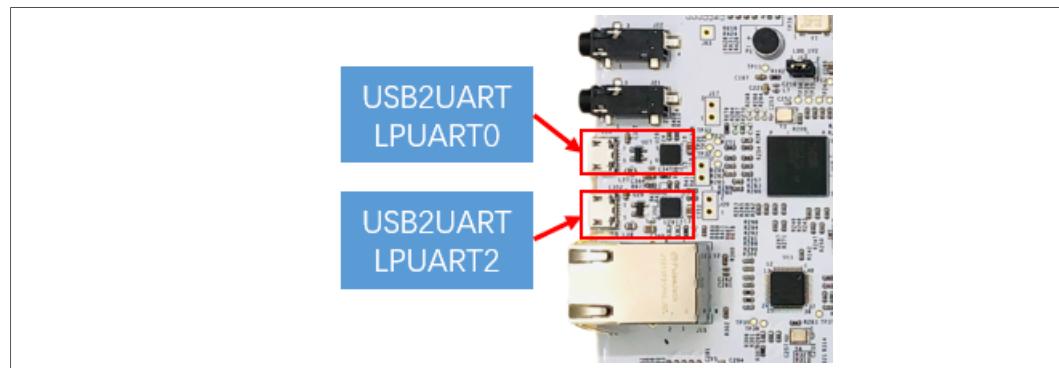

### 8.3.3 USB to UART interface

Two USB2UART devices CP2104 are included on the board so that debug message can be easily transmitted to PC. LPUART0 and LPUART2 of MCU are connected to the USB2UART interfaces.

Figure 17. CAN/LIN circuit block diagram/USB to UART circuit on the White Board

## 8.4 General purpose inputs and outputs

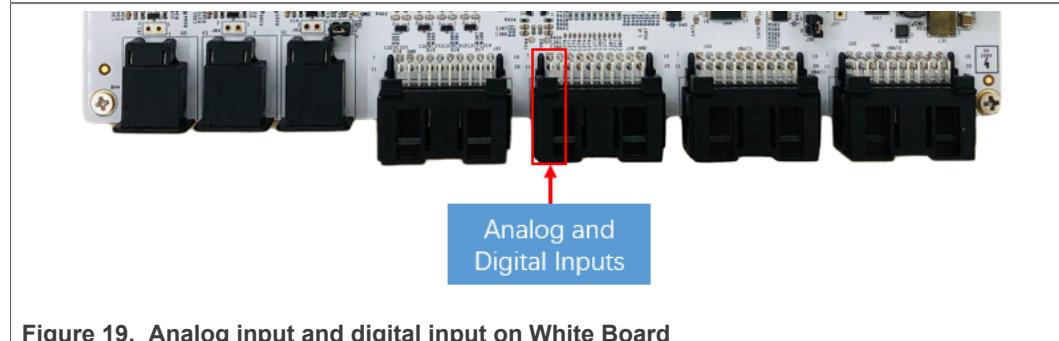

#### 8.4.1 Analog and digital inputs

There are 2 general purpose digital inputs and 2 analog inputs on the White Board. Detailed PINs information can be found in [Table 6](#). The analog input voltage can range from 0V~20V. The digital input voltage can range from 0V~20V and they can also be used for analog signals sampling.

Figure 18. Analog input and digital input circuit

Figure 19. Analog input and digital input on White Board

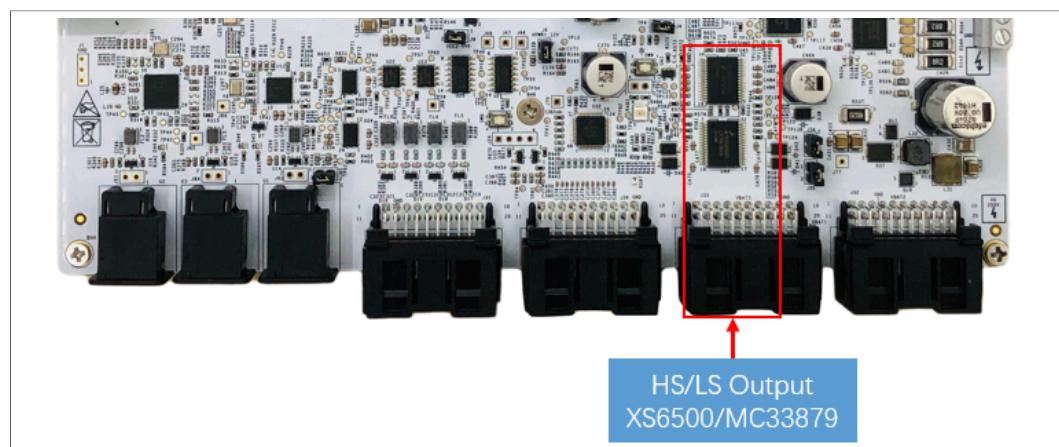

#### 8.4.2 High side and low side driver outputs

There are 4 channels high side outputs driven by XS6500. They can be controlled by 4 MCU GPIO/PWM PINs or by MCU SPI commands sent to XS6500. There are 8 channels low side outputs through MC33879 and they are controlled by MCU SPI commands. Related MCU PINs details are listed in [Table 6](#).

Figure 20. HS/LS outputs on the White Board

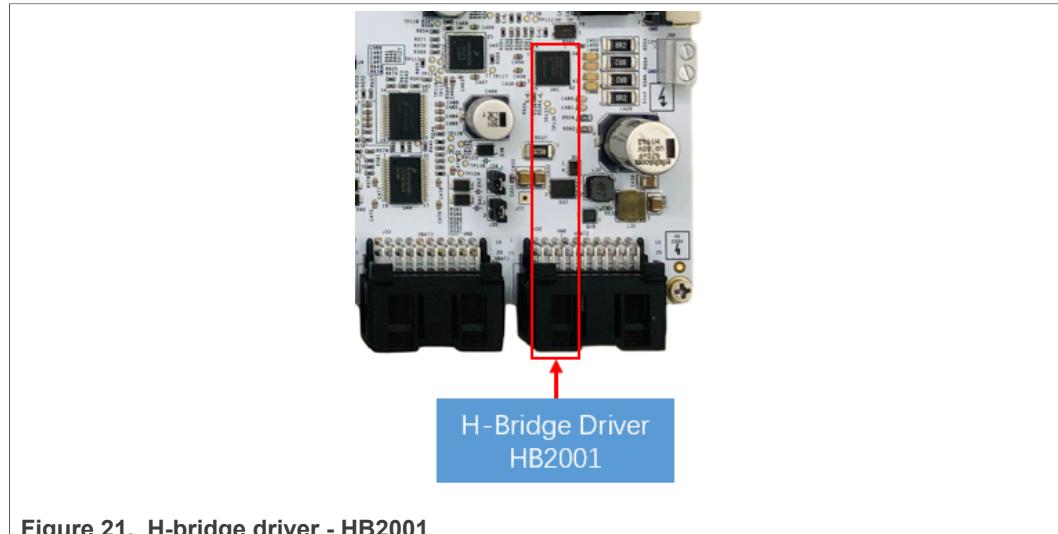

## 8.5 H-bridge driver

There is an H-Bridge driver on this board which is controlled by MCU SPI interface. It can be used for brushed DC motor control.

Figure 21. H-bridge driver - HB2001

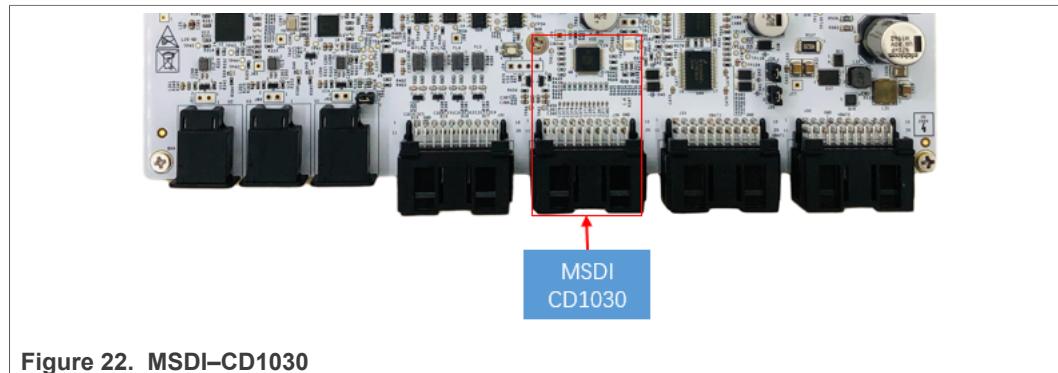

## 8.6 Switch inputs detection

The MSDI device CD1030 includes 21 switch-to-ground inputs and 12 programmable inputs (switch to battery or ground). There are 6 channels SG (Switch-to-Ground inputs) pins and 6 channels SP (Switch to Programmable input) pins which are implemented on the White Board. The switch status, either open or closed, can be read by MCU through an SPI interface. Two push buttons – SW8 and SW9 – are used to trigger the switch status transition for test purpose.

Figure 22. MSDI-CD1030

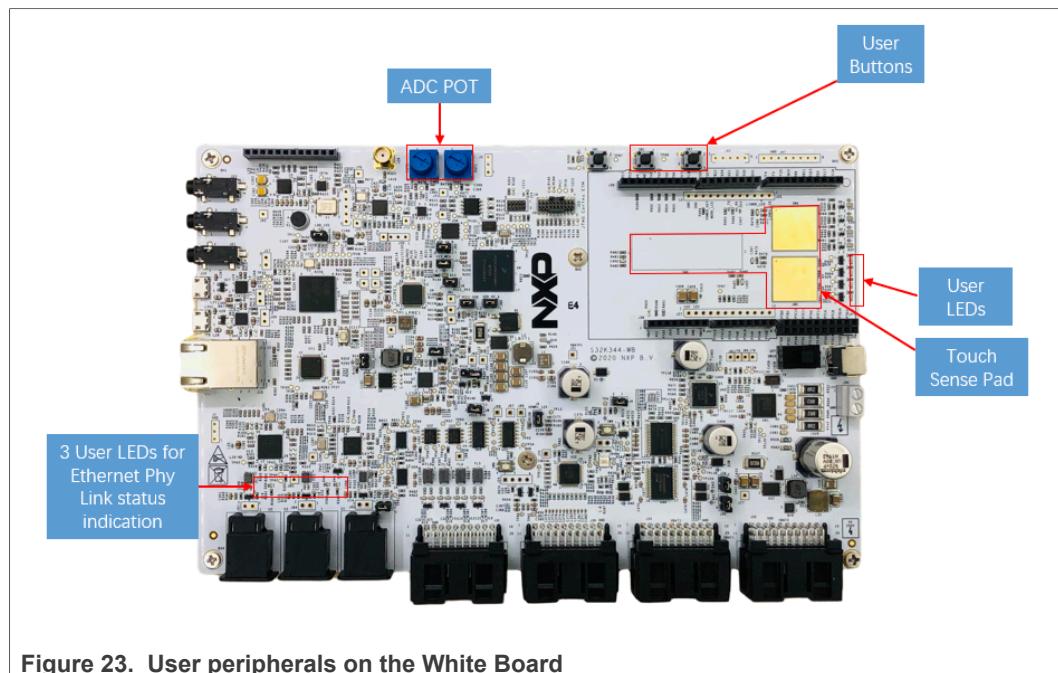

## 8.7 User peripherals

The user buttons, user LEDs, ADC POTs and touch sense pads on the White Board are shown in below figure. The related MCU PINs information are listed in [Table 6](#).

Figure 23. User peripherals on the White Board

### 8.7.1 User buttons

MCU PTC20 and PTC21 are used to monitor the user push buttons state. See the following figure for schematics of related circuits.

Figure 24. User push button schematic

### 8.7.2 User LEDs

MCU GPIO PTF8, PTF9, PTF10, PTF11 are used to drive the 4 user LEDs, and they are high-active. There are another 3 user LEDs driven by PTG0/PTG1/PTG2 which can be used to indicate the ethernet PHY link status.

Figure 25. User LEDs schematic

### 8.7.3 ADC rotary potentiometers

The two ADC POTs are linked to MCU PINs PTB13 and PTB14. See following figure for the schematic.

Figure 26. User ADC inputs schematic

### 8.7.4 Touch sense pads

There are two touch sense buttons and one touch sense slider on the White Board. See following figure for the schematic.

Figure 27. User ADC inputs schematic

## 8.8 IO headers for extension board

There are some IO Headers that can be used for external modules or EVB. See the following figure for these interfaces on the White Board.

Figure 28. IO headers for external board

### 8.8.1 GD3000 EVB

The IO Headers J38, J39, J41, J42, J43, J44, J45J can be used as ARDUINO shield connectors. It's compatible with GD3000 EVB. Install the GD3000 EVB onto these headers and the White Board can drive a 3-phase PMSM motor. Key signals connections can be found in the White Board schematics.

### 8.8.2 4G module extension

The IO Headers J26 and J27 are used for external 4G Module. The part number is "USR-LTE-7S4".

## 8.9 Car access

The RF receiver NCK2910 and the LF driver NJJ29C2 are used in car access applications. External antennas are required for them to communicate with the KEYs. MCU can control these two devices via SPI interfaces. See below figure for block diagram. NCK2910 and NJJ29C2 are under NDA control. Please contact NXP sales representative and sign NDA if you need details about the two devices.

Figure 29. RF and LF circuit block diagram

The RF circuit and LF circuit on the White Board are shown in the following figure.

Figure 30. RF and LF circuit on the White Board

## 8.10 Audio

The audio codec SGTL5000 can be used together with ethernet circuits to evaluate AVB application. The device CS2100CP is used to synchronize the clock between MCU and SGTL5000. MCU transmits/receives audio data with SGTL5000 via SAI\_0 interface and configures the audio codec via LPI2C\_0 interface. We provide a 12-pin header for connecting external multiple-channel audio codec.

Figure 31. Audio circuit on the White Board

## 8.11 Others

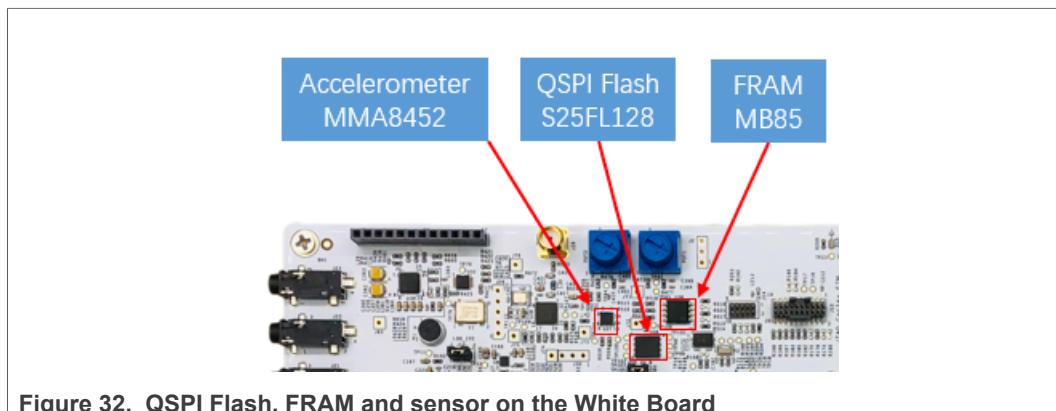

The QSPI Flash (S25FL128L, 128Mbit) on the White Board can be used to store the firmware for S32K344 and other controllers connected to the vehicle network.

The FRAM (MB85RC256VPF, 256Mbit) is used to store some NVM data in case quick write is needed during power down.

The MMA8452Q is a smart, low-power, three-axis, capacitive, micromachined accelerometer with 12 bits of resolution. The device can be configured to generate inertial wakeup interrupt signals from any combination of the configurable embedded functions allowing the MMA8452Q to monitor events while staying in low power mode.

Figure 32. QSPI Flash, FRAM and sensor on the White Board

## 9 Abbreviations used in the document

Table 11. Abbreviations

|      |                                 |

|------|---------------------------------|

| WB   | White Board                     |

| BCM  | Body Control Module             |

| DCU  | Domain Control Unit             |

| GW   | Gateway                         |

| AVB  | Audio Video Bridging            |

| PHY  | Physical Layer Transceiver      |

| SBC  | System Basis Chip               |

| LF   | Low Frequency                   |

| MSDI | Multiple Switch Detection Input |

| HS   | High Side Driver                |

| LS   | Low Side Driver                 |

## 10 Legal information

### 10.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 10.2 Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Terms and conditions of commercial sale** — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <http://www.nxp.com/profile/terms>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Suitability for use in non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Security** — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at [PSIRT@nxp.com](mailto:PSIRT@nxp.com)) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 10.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

**NXP** — wordmark and logo are trademarks of NXP B.V.

## Tables

|         |                                     |   |          |                                            |    |

|---------|-------------------------------------|---|----------|--------------------------------------------|----|

| Tab. 1. | Revision history .....              | 1 | Tab. 7.  | Jumpers for current measurement .....      | 13 |

| Tab. 2. | Signals definitions of J32 .....    | 4 | Tab. 8.  | Jumpers for VBAT power supply source ..... | 13 |

| Tab. 3. | Signals definitions of J33 .....    | 5 | Tab. 9.  | Debug interface pins .....                 | 16 |

| Tab. 4. | Signals definitions of J36 .....    | 5 | Tab. 10. | SBC and MCU connections .....              | 17 |

| Tab. 5. | Signals definitions of J31 .....    | 6 | Tab. 11. | Abbreviations .....                        | 28 |

| Tab. 6. | White Board resources mapping ..... | 7 |          |                                            |    |

## Figures

|          |                                                                              |    |

|----------|------------------------------------------------------------------------------|----|

| Fig. 1.  | S32K344 White Board block diagram .....                                      | 2  |

| Fig. 2.  | S32K344 White Board features overview .....                                  | 3  |

| Fig. 3.  | S32K344 White Board connectors and<br>interfaces .....                       | 4  |

| Fig. 4.  | S32K344 White Board features .....                                           | 10 |

| Fig. 5.  | SBC power supply topology .....                                              | 11 |

| Fig. 6.  | Power supply topology .....                                                  | 12 |

| Fig. 7.  | Jumpers settings topology .....                                              | 14 |

| Fig. 8.  | Pins distribution for different power<br>domains .....                       | 15 |

| Fig. 9.  | External crystals for MCU .....                                              | 16 |

| Fig. 10. | Debug interface .....                                                        | 17 |

| Fig. 11. | SBC and MCU on the White Board .....                                         | 17 |

| Fig. 12. | SBC debug entry circuit .....                                                | 18 |

| Fig. 13. | Ethernet circuit block diagram .....                                         | 19 |

| Fig. 14. | Ethernet circuit on the White Board .....                                    | 19 |

| Fig. 15. | CAN/LIN circuit block diagram .....                                          | 20 |

| Fig. 16. | CAN and LIN transceivers on White Board .....                                | 20 |

| Fig. 17. | CAN/LIN circuit block diagramUSB to<br>UART circuit on the White Board ..... | 20 |

| Fig. 18. | Analog input and digital input circuit .....                                 | 21 |

| Fig. 19. | Analog input and digital input on White<br>Board .....                       | 21 |

| Fig. 20. | HS/LS outputs on the White Board .....                                       | 21 |

| Fig. 21. | H-bridge driver - HB2001 .....                                               | 22 |

| Fig. 22. | MSDI-CD1030 .....                                                            | 22 |

| Fig. 23. | User peripherals on the White Board .....                                    | 23 |

| Fig. 24. | User push button schematic .....                                             | 23 |

| Fig. 25. | User LEDs schematic .....                                                    | 24 |

| Fig. 26. | User ADC inputs schematic .....                                              | 24 |

| Fig. 27. | User ADC inputs schematic .....                                              | 25 |

| Fig. 28. | IO headers for external board .....                                          | 25 |

| Fig. 29. | RF and LF circuit block diagram .....                                        | 26 |

| Fig. 30. | RF and LF circuit on the White Board .....                                   | 26 |

| Fig. 31. | Audio circuit on the White Board .....                                       | 27 |

| Fig. 32. | QSPI Flash, FRAM and sensor on the<br>White Board .....                      | 27 |

## Contents

---

|           |                                                         |           |

|-----------|---------------------------------------------------------|-----------|

| <b>1</b>  | <b>Introduction</b>                                     | <b>2</b>  |

| <b>2</b>  | <b>Features overview</b>                                | <b>3</b>  |

| <b>3</b>  | <b>Connectors and interfaces</b>                        | <b>4</b>  |

| <b>4</b>  | <b>MCU pins assignments and board resources mapping</b> | <b>7</b>  |

| <b>5</b>  | <b>White Board startup</b>                              | <b>10</b> |

| <b>6</b>  | <b>Power supply</b>                                     | <b>11</b> |

| <b>7</b>  | <b>Jumper settings</b>                                  | <b>13</b> |

| <b>8</b>  | <b>General functional description</b>                   | <b>15</b> |

| 8.1       | MCU HW configuration                                    | 15        |

| 8.1.1     | MCU power supply configuration                          | 15        |

| 8.1.2     | MCU clock settings                                      | 15        |

| 8.1.3     | MCU reset control                                       | 16        |

| 8.1.4     | MCU debug interface                                     | 16        |

| 8.2       | SBC features                                            | 17        |

| 8.2.1     | SBC and MCU connections                                 | 17        |

| 8.2.2     | SBC wakeup function                                     | 18        |

| 8.2.3     | SBC fail-safe outputs                                   | 18        |

| 8.2.4     | SBC debug mode                                          | 18        |

| 8.3       | Communication interfaces                                | 19        |

| 8.3.1     | Ethernet interfaces                                     | 19        |

| 8.3.2     | CAN and LIN interfaces                                  | 19        |

| 8.3.3     | USB to UART interface                                   | 20        |

| 8.4       | General purpose inputs and outputs                      | 20        |

| 8.4.1     | Analog and digital inputs                               | 21        |

| 8.4.2     | High side and low side driver outputs                   | 21        |

| 8.5       | H-bridge driver                                         | 22        |

| 8.6       | Switch inputs detection                                 | 22        |

| 8.7       | User peripherals                                        | 22        |

| 8.7.1     | User buttons                                            | 23        |

| 8.7.2     | User LEDs                                               | 23        |

| 8.7.3     | ADC rotary potentiometers                               | 24        |

| 8.7.4     | Touch sense pads                                        | 24        |

| 8.8       | IO headers for extension board                          | 25        |

| 8.8.1     | GD3000 EVB                                              | 25        |

| 8.8.2     | 4G module extension                                     | 25        |

| 8.9       | Car access                                              | 25        |

| 8.10      | Audio                                                   | 26        |

| 8.11      | Others                                                  | 27        |

| <b>9</b>  | <b>Abbreviations used in the document</b>               | <b>28</b> |

| <b>10</b> | <b>Legal information</b>                                | <b>29</b> |

---

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.